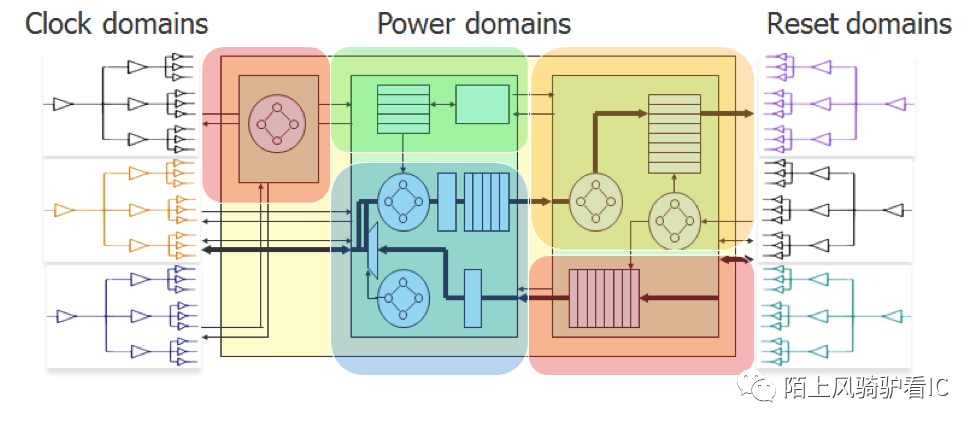

如何确定一个时钟域?

相位关系确定的两个或多个时钟称为同步时钟,所有被同步时钟驱动的时序逻辑,为同一时钟域;无确定相位关系的两个或多个时钟称为异步时钟。同步时钟跟异步时钟特别像夫妻关系跟情人关系,同步时钟像夫妻关系,有固定规则保护其正常运转,出轨就是setup 或hold 没修干净;异步时钟就如情人关系,没有任何规则可以保证共同财产不受侵犯,没有任何责任跟义务,所以需要除了灵肉上的交流之外尽量相互隔离。一个道理:信号是可以夸时钟域的,情人关系是可以有的,只要做好必要的隔离不影响社会规则正常运转就成。

如果规避亚稳态?

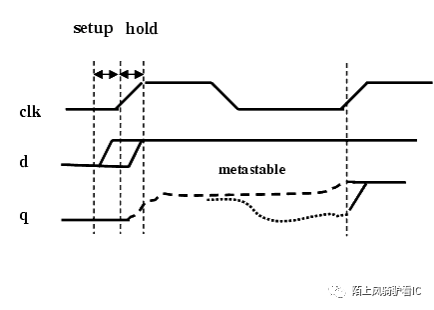

数字电路是个1,0分明的世界,除此之外的状态都不是稳定状态,被称为亚稳态,亚稳态会导致电路功能失效,本来期待一个1结果来了一个0,功能失效,只能姐妹六九天长地久了。同步电路通过setup 跟hold 来规避亚稳态。

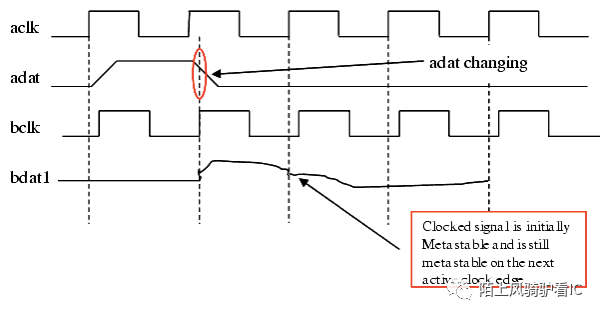

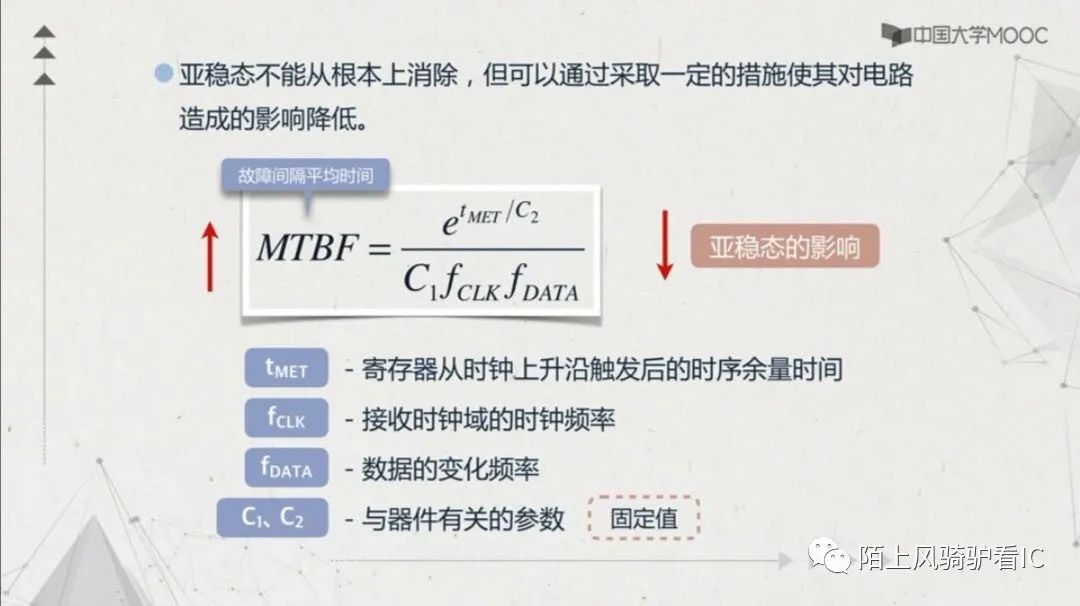

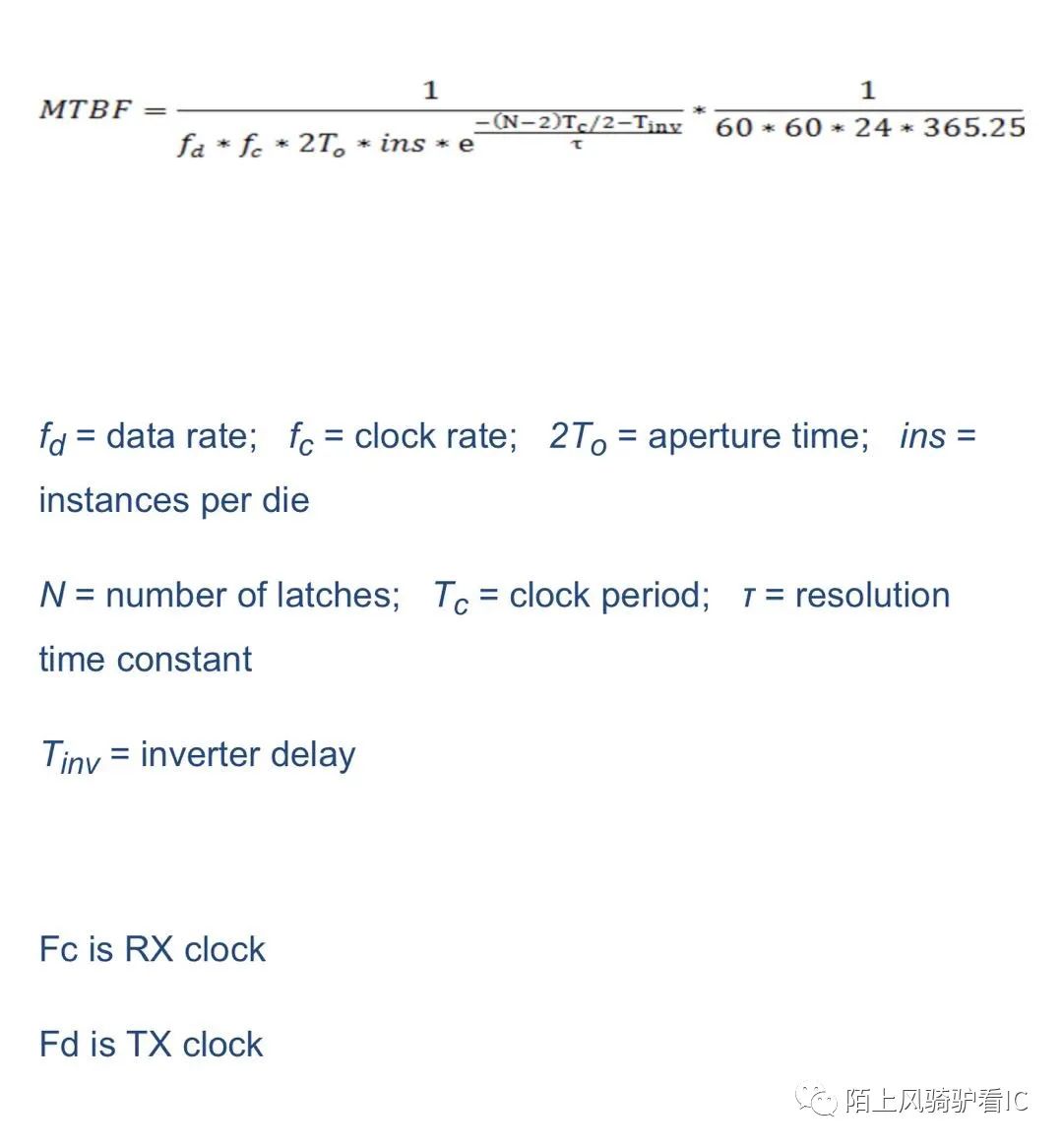

但是对于异步电路而言,因为时钟相位不固定,无法保证来的一定是0或1,所以无法用静态时序分析的办法来规避亚稳态,办法总比问题多,聪明的工程师们拍着地中海造出了同步电路,虽然不能彻底规避亚稳态,但是只要使其发生的概率逼近于无限小,那情人还是情人,灵肉交流就能畅通无阻。

常见的同步电路有哪些?

常见的同步电路有:

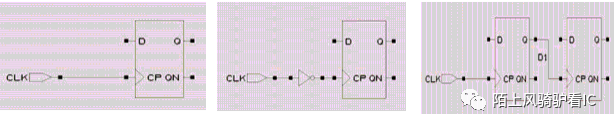

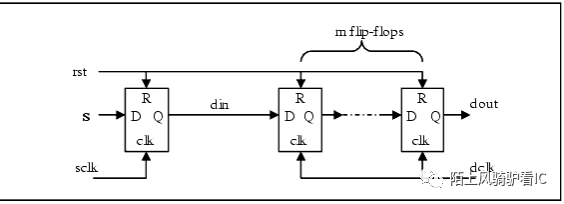

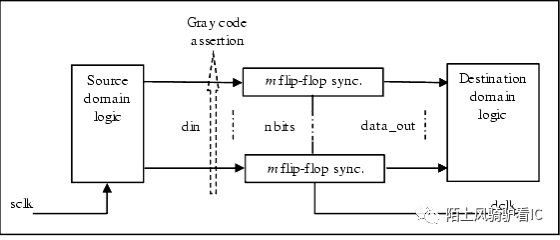

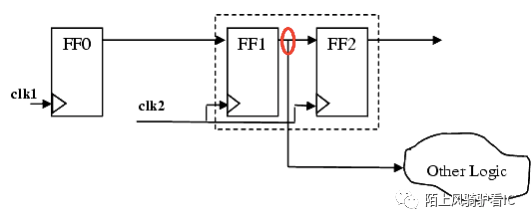

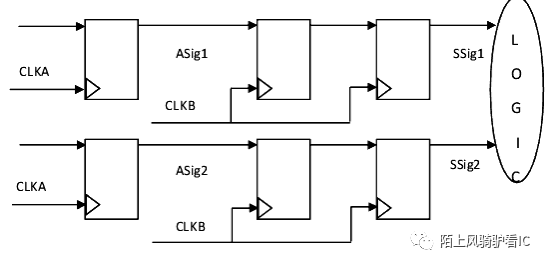

由两级或多级寄存器组成的同步器:这是最常见的同步器,用于同步单根信号或一组bus, 如果是同步一组bus 则这组bus 必须用格雷码。

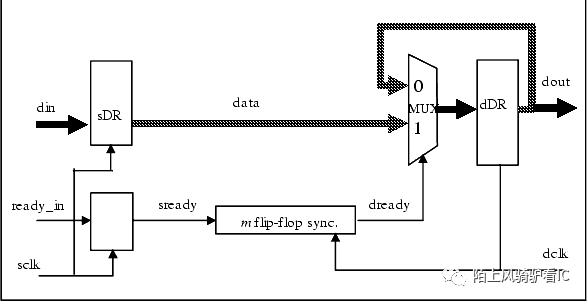

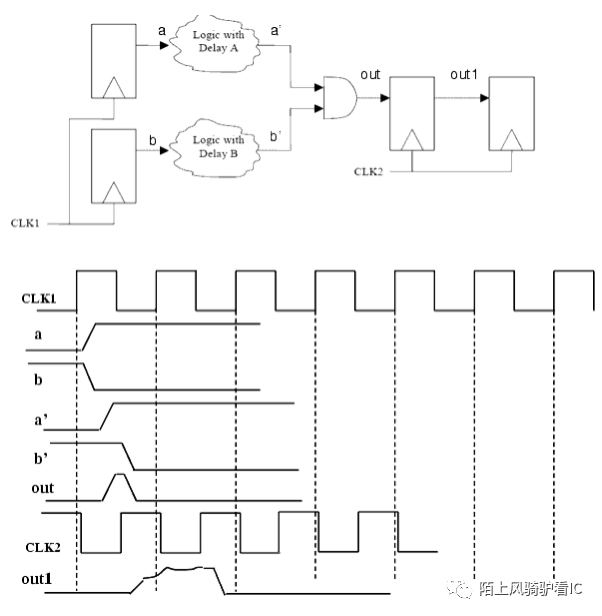

MUX 同步电路:如下图将dready 信号经过同步器送到目标时钟域,对于这种同步电路要在设计上保证:sready 信号必须相对于目标时钟保持m+1 个时钟周期,也就是说sready 在m+1 个dclk 周期内都不能跳变;同时在数据传输过程data 保持稳定,所谓的数据传输过程即dready 信号在dclk 时钟域有效期间。

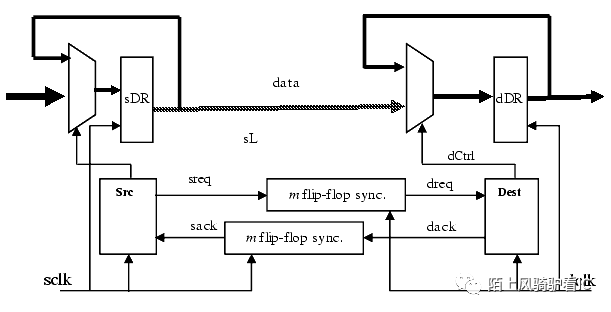

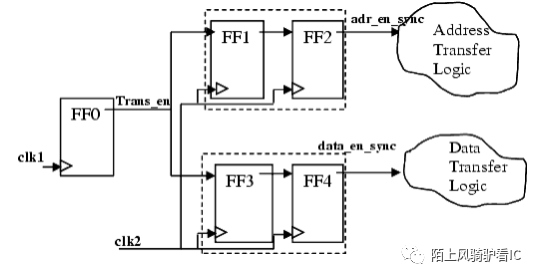

握手同步电路:如下图所示,是一个典型的握手同步电路,握手同步电路通过请求信号跟应答信号进行数据交流,当有数据需要传输时,源时钟域发出请求信号,同时发出数据,目标时钟域收到请求信号后将数据锁存,同时返回应答信号,源时钟域收到应答信号后,可改变数据,握手同步电路的弊端是latency 太长。对于握手同步电路,在设计上要保证:sreq 信号必须保持m+1 个dclk 时钟周期;data 信号必须保持m 个dclk 时钟周期;dack 信号必须保持m+1 个sclk 时钟周期;源时钟域在收到应到信号之前必须保持请求信号;在上一个请求传输没有结束之前不能发出新的请求。

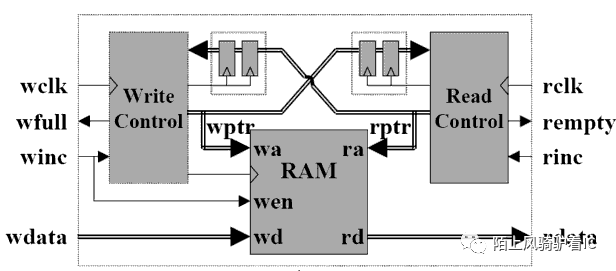

异步FIFO: 异步FIFO 应该是大家最熟悉的同步电路了,在学习Verilog 的时候都应该写过异步FIFO. 异步FIFO 还是常见的笔试面试题,根据需求算FIFO 深度。

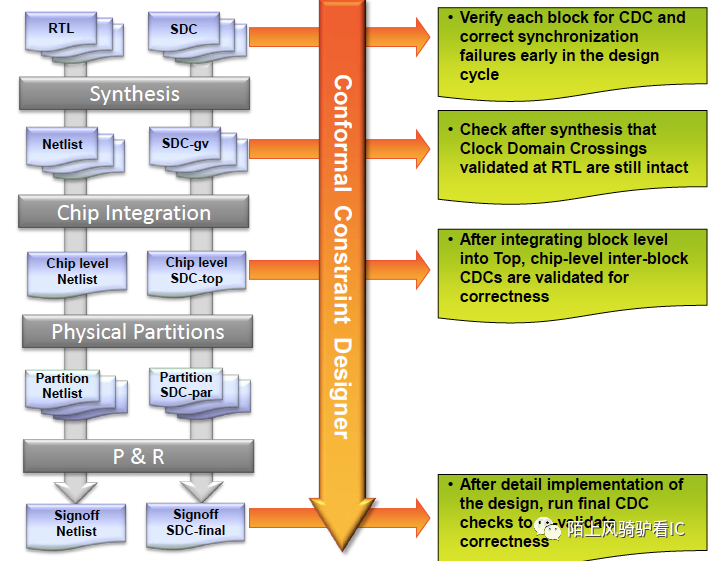

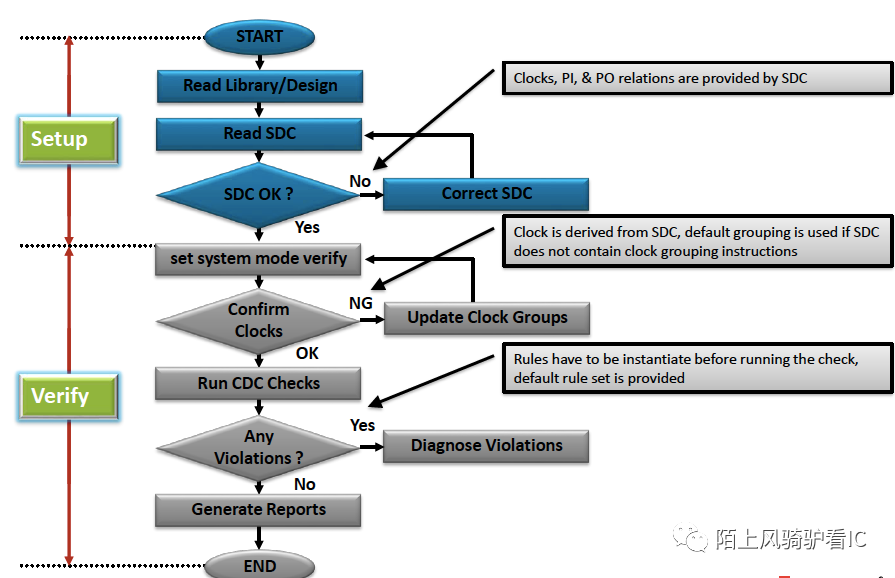

CDC check 在检查什么?

实现端的CDC check 工具,在做CDC check 时,首先根据SDC 确定时钟域,然后在设计中提取同步电路;然后再分析同步电路的各种问题,常见的检查有:

实现端做CDC check 是依赖于SDC 的,所以要确保在SDC 中 clock 关系定义正确。老驴很好奇,在验证端的CDC check 是怎么做的?是否用『断言』更有效?