2020 中国(重庆)ICCAD 于 12 月 10-11 日在重庆悦来国际会议中心顺利召开,会上汇集了业界众多精英领袖,共同探讨集成电路产业的趋势与挑战。在 11 号上午的 EDA 与 IC 设计创新专题论坛,Cadence 公司资深产品工程总监刘淼出席了活动并发表了题为《机器学习,让 EDA 如虎添翼》的演讲,同时分享了 Cadence 在机器学习上的最新进展。

工欲善其事,必先利其器

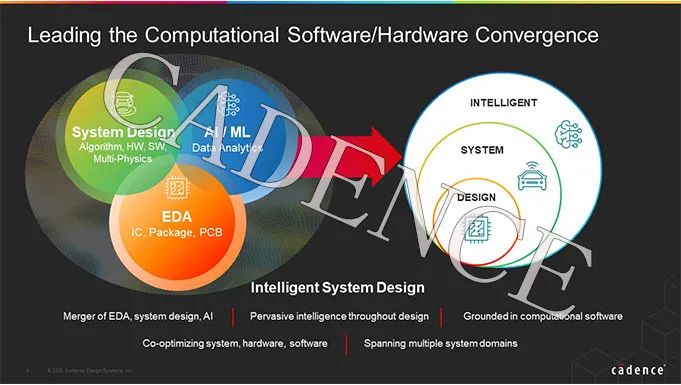

全自动的智能系统设计是应对第四次技术革命的核心,而这之中人工智能与机器学习将会扮演重要角色。目前,智能系统设计正面临着三个层次的挑战,即智能平台的性能、系统的性能和芯片性能,而将机器学习融入到 EDA 设计工具中,无疑是应对挑战最有效的解决办法。

机器学习入局,EDA 算法大提升

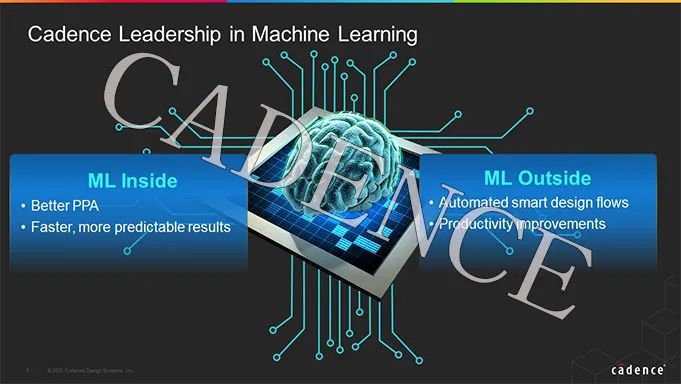

Cadence 的机器学习也集中在“内功”和“外功”两个方面。

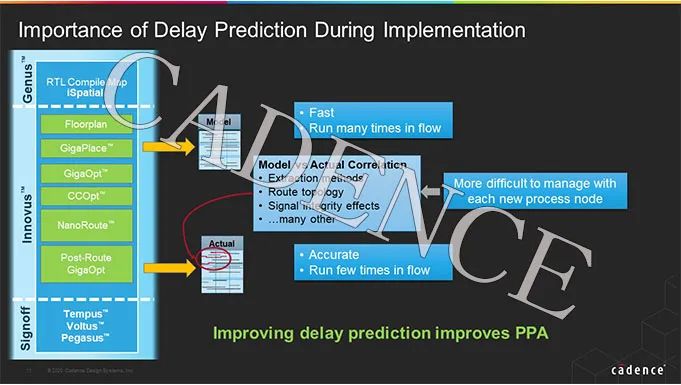

其中,EDA 算法就相当于内功,通过机器学习可以不断提升核心引擎的性能,从而使系统做到更快更精准的预测。

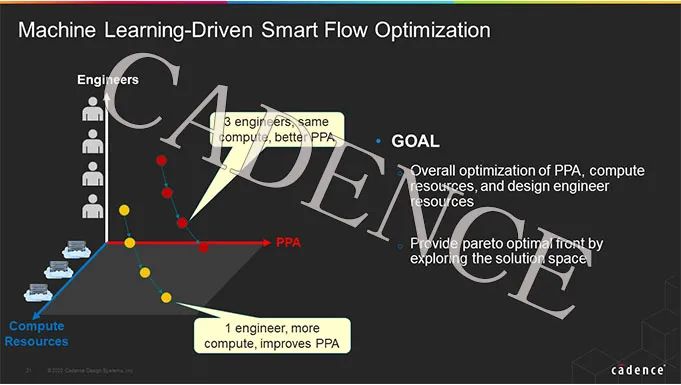

设计中的各种流程就相当于外功,只有知己知彼才能百战不殆。而机器学习就是那个帮你了解“对手”的人,它可以帮设计工程师快速定位最聪明的流程,进而大幅度提高工作效率。

“内家功”提升引擎性能

“外家功”优化流程

摩尔定律不会失效

3DIC 延续未来

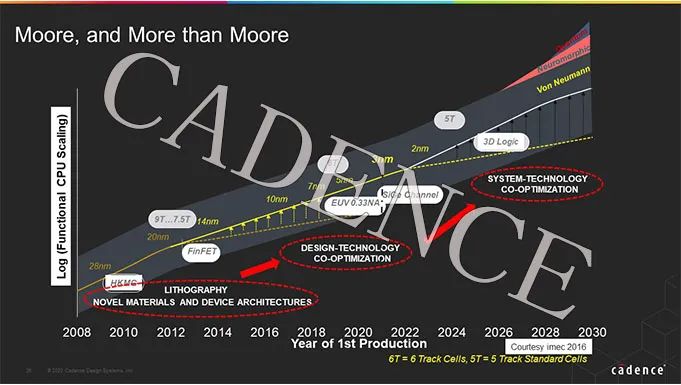

从 14nm 到 5nm 再到 3nm,先进制程的提升所带来的性能收益越来越少,这也就引发了人们对于摩尔定律发展的担忧。从本质上而言,摩尔定律本身不是一个科学定律,而是一种经济学定律,只要有市场的需求,半导体就会找到新的方式让摩尔定律顺延下去。这个新的方式,也许就是 3DIC。

作为全球半导体行业蓬勃发展的见证者与参与者,Cadence 将持续通过创新的产品和与时俱进的战略布局,为中国乃至世界的 IC 设计从业者提供丰富的经验与完善的服务,加速电子设计业和创新应用的腾飞。