以前用过这个ADC,感觉又小又好又贵,今天下班前来说说这个东西好玩的地方。

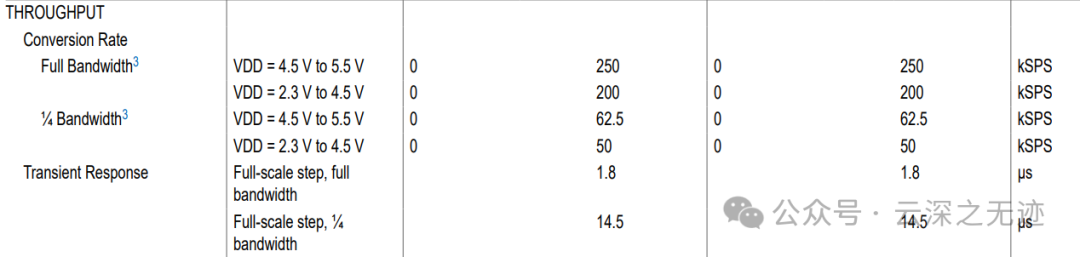

然后就250-kSPS,还是针对一大类低速应用应用,足够了

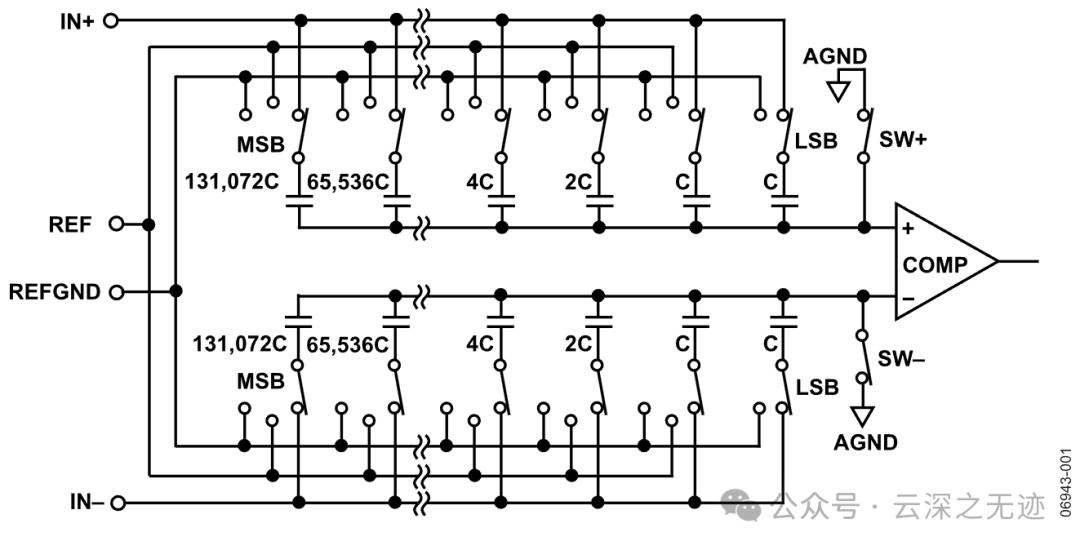

PulSAR速度比得尔塔-ς的构架是快,但是做不到高精度,本身的原因,其实就是二分法做比较。但是他很吃参考源的精度,所以ADC有6中REF就不足为奇了。

工作原理: 通过逐次比较输入模拟信号与内部DAC产生的模拟值,不断逼近,最终得到数字结果。

采集时间特点:

转换时间相对固定,与分辨率相关。分辨率越高,转换时间越长。

转换时间一般较短,适用于中速、高分辨率的应用。

优势:

结构相对简单,成本较低。

转换精度较高。

缺点:

转换时间受分辨率影响,高分辨率时转换时间较长。

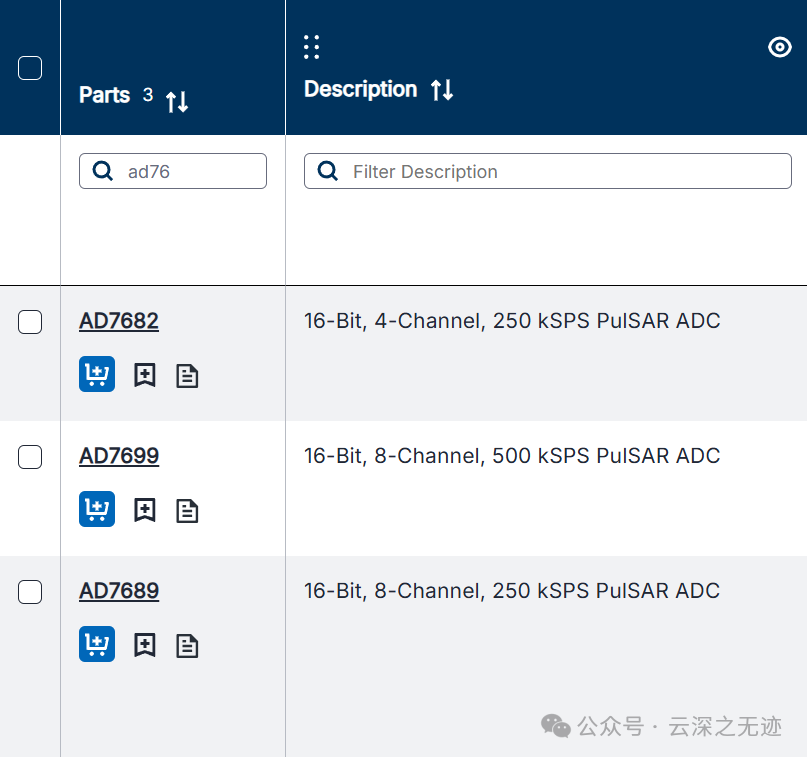

其实82和89是一样的,但是89通道更多

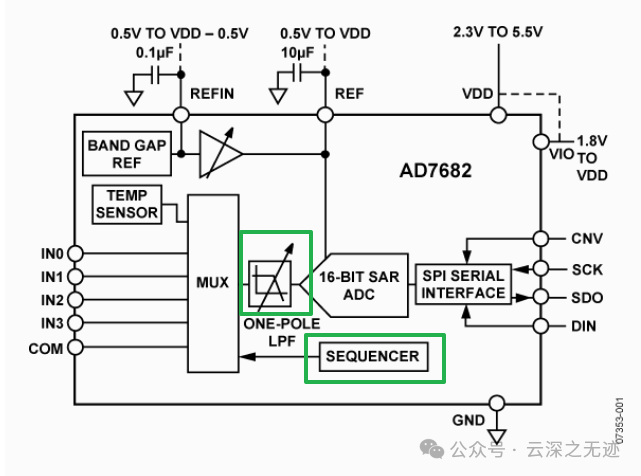

构架上面来说有灵活的参考和一个输入端的滤波器,非同步

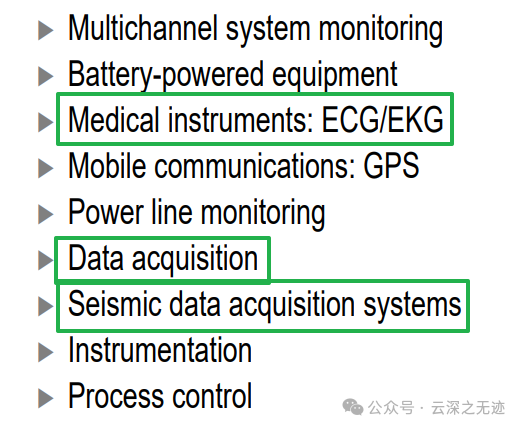

应用呢,就比较全面了,因为是uV的LSB,所以ECG也是没有问题的。甚至地震仪器也是可以的。

因为里面对输入级的设计,可以支持正差分电压输入

接下来就是一些数据手册里面有趣的东西:

这个是滤波器的性能

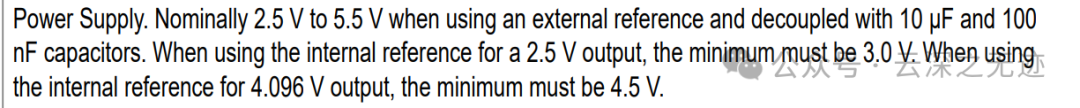

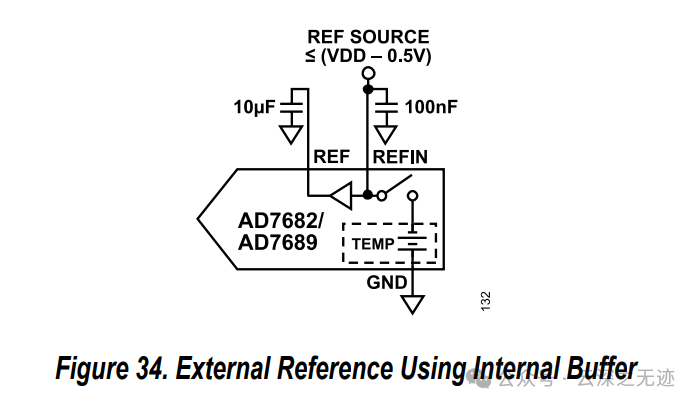

需要注意的是,在使用两个参考电压的时候,对外部供电有要求,即使是宽电压的ADC器件

寄存器是14位的,CNV和传统的中断引脚还不一样,功能更加的丰富

这个是说分辨率最小怎么算

信噪比的定义是什么,分母是奈奎斯特下包括谐波和直流的均方根

这个是测试有效位的方法,使用SIN法,直接带入,信号注入是满量程的

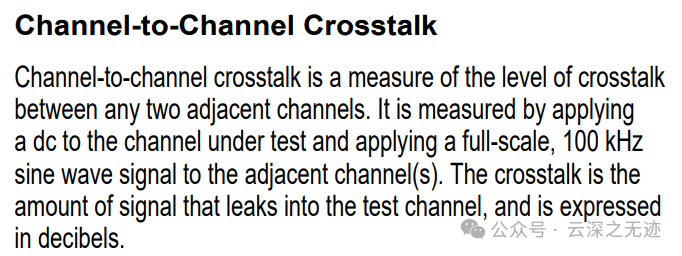

因为不是同步的采集,所以这个通道之间有串扰,怎么测量呢?一个通道直流,旁边是100Khz的SIN满幅度信号,学会了

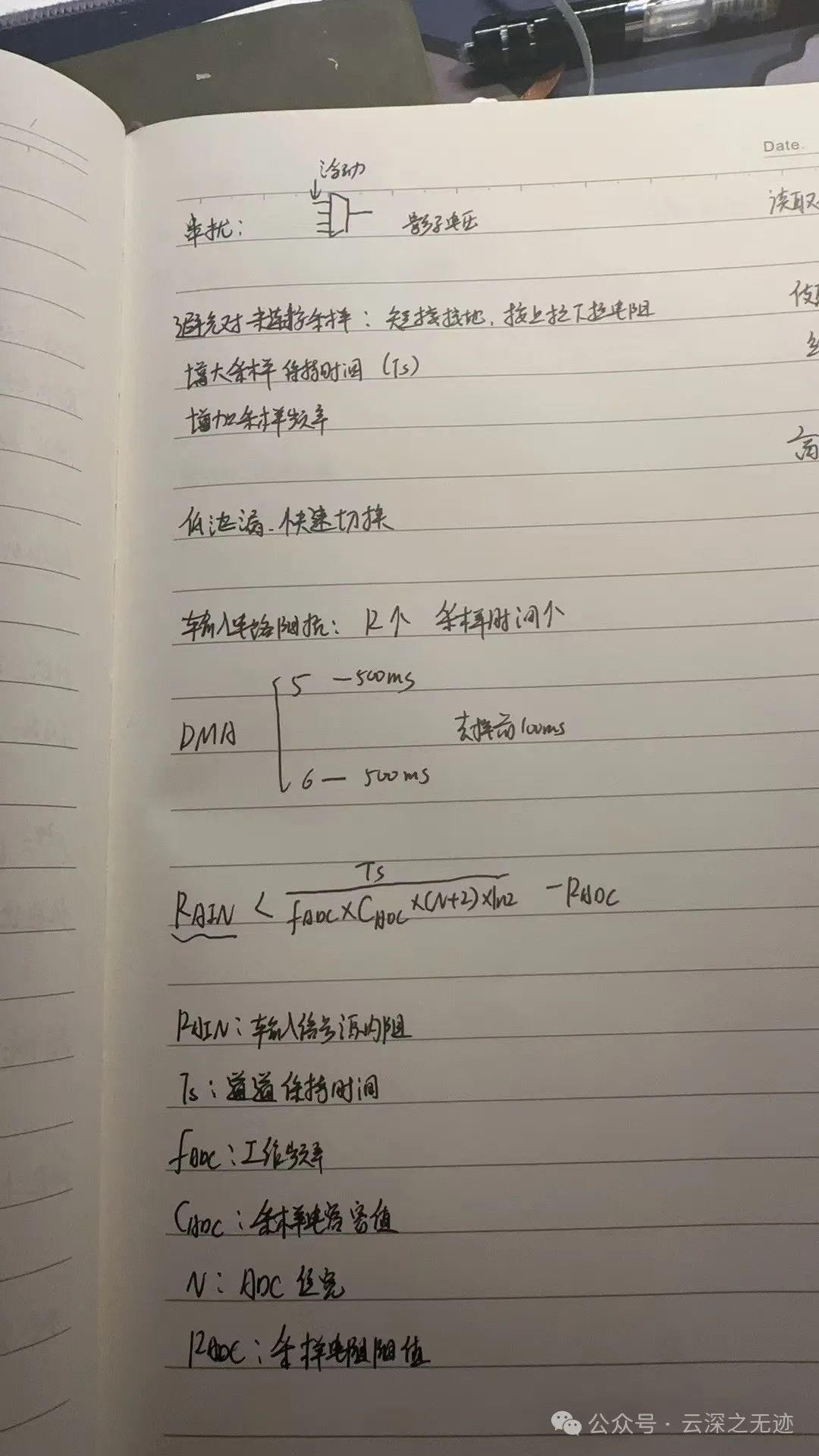

这是串扰整改的一个笔记,我就不解释了,有缘人应该是可以看懂的

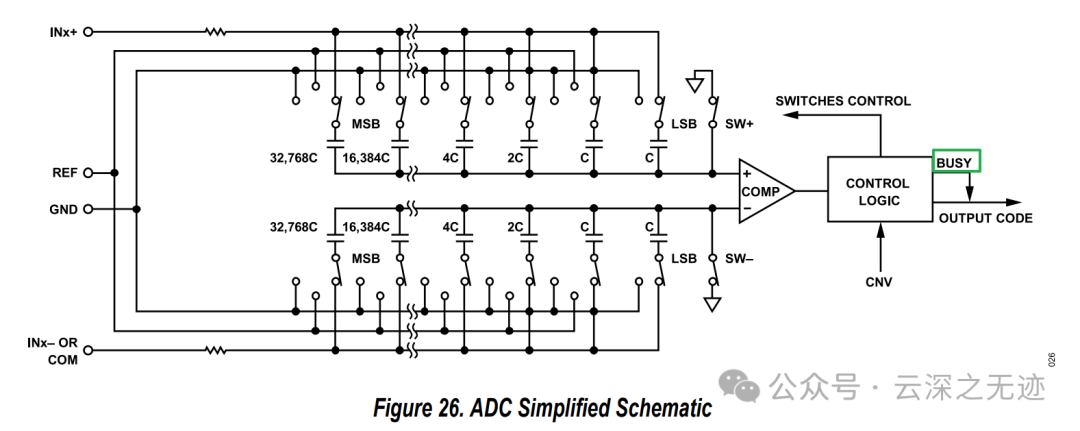

然后这个构架自己有一个时钟在里面,不需要外部引入,然后这个BUSY信号是一个在使用过程中非常有用的标志位,代码里面需要不停的判断这里

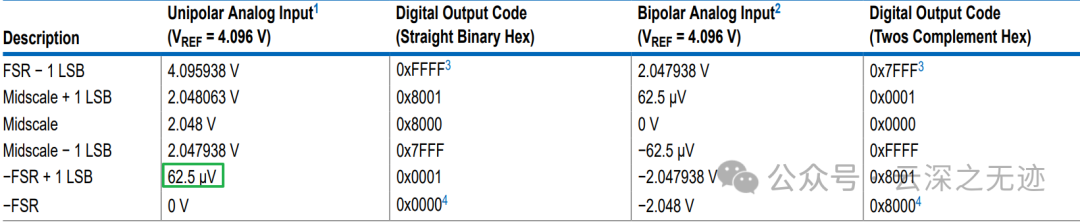

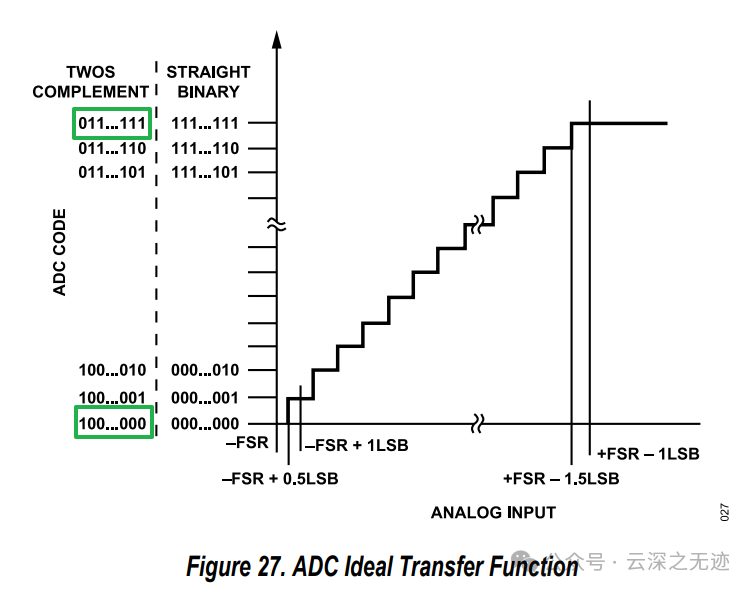

然后差分输出的代码是对偶的,看我标的地方

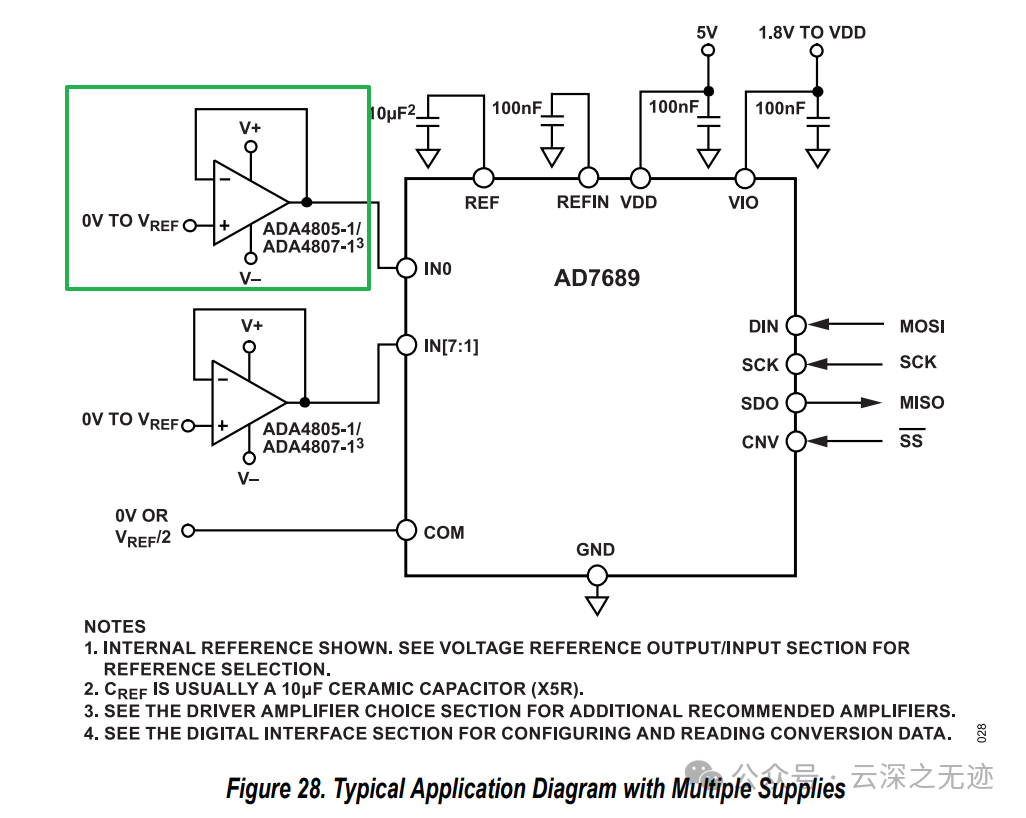

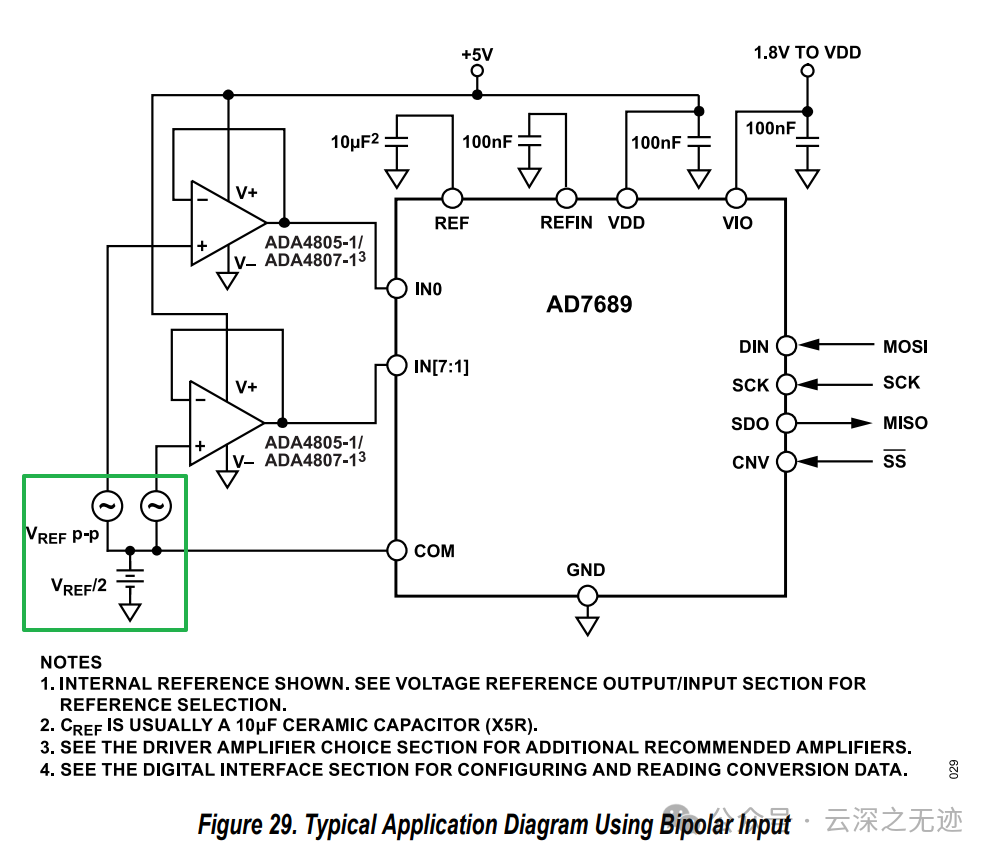

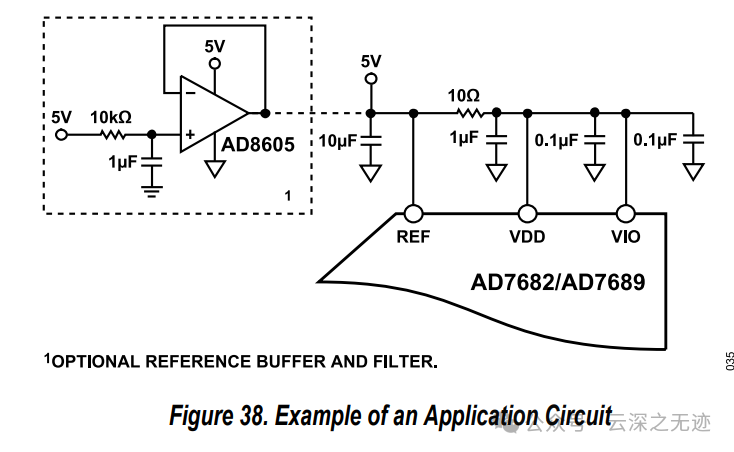

因为这个ADC我没有找到输入阻抗的参数,所以就有了驱动级,直接缓冲,一般的应用可以在输入的时候加个电容,构成一个低通滤波器,也可以使用,精密应用就可以加运放

也可以这样的应用在差分测量上

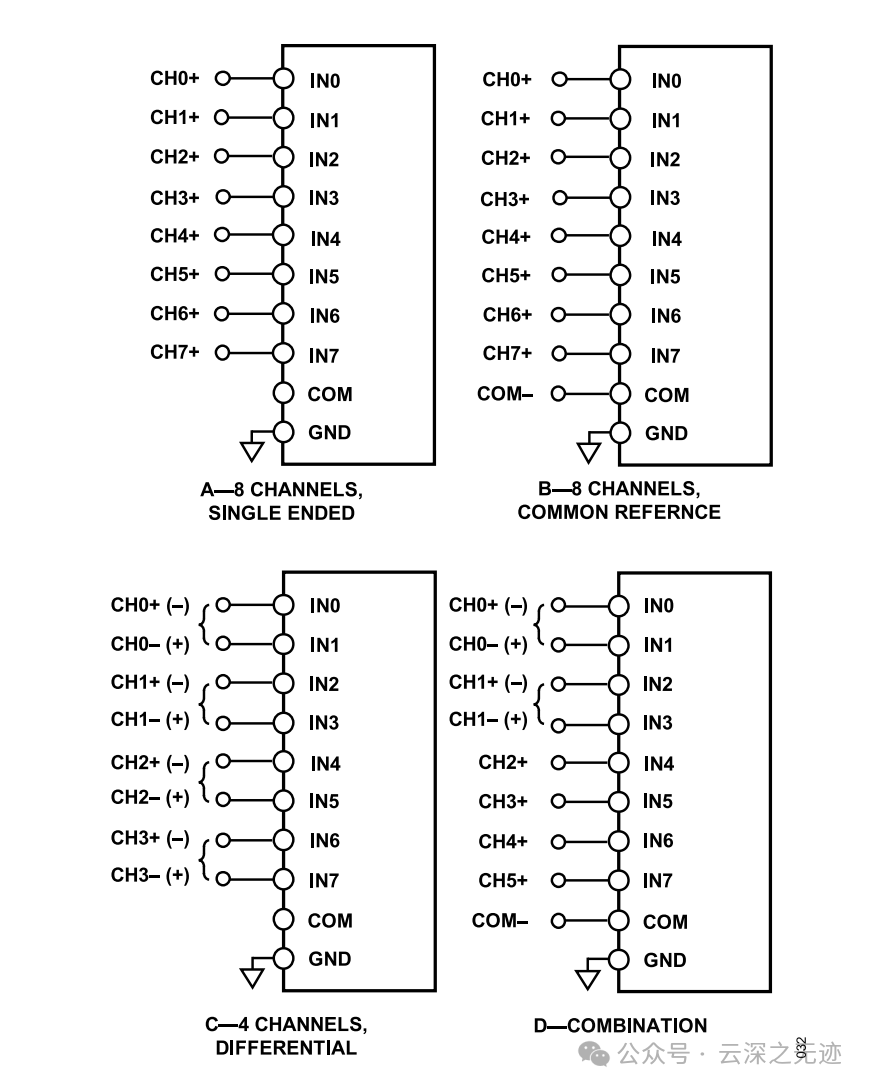

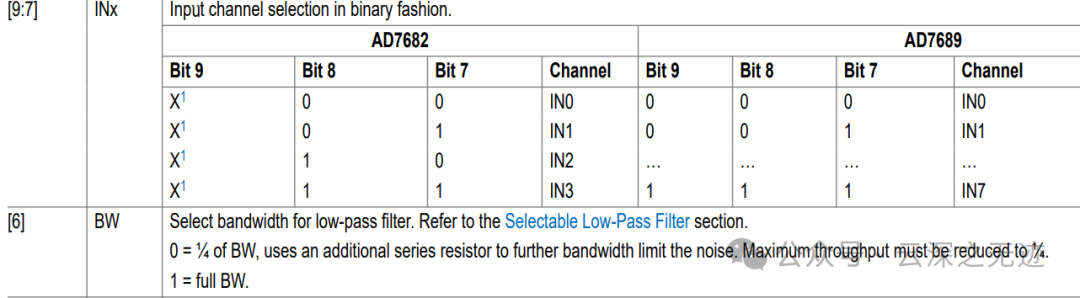

因为通道很多,所以可以选择使用什么样的测量方式

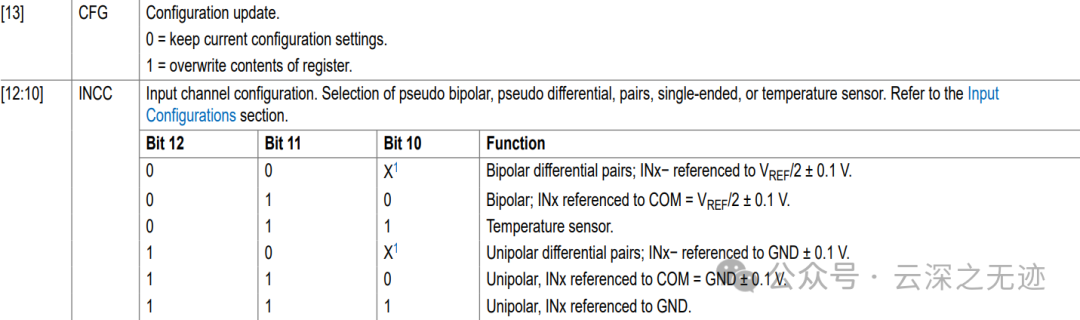

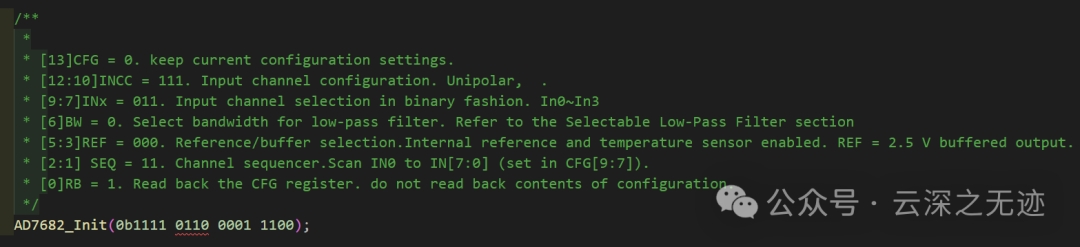

可以遇到下面的10-12寄存器来设置,13位是一个标志位来告诉ADC配置参数要不要改,如果要改,3个时钟周期内是不要读取的,因为生效要2个周期(第一个转换周期: 上电后,前三个转换周期产生的结果是无效的,因为CFG寄存器需要两个转换周期才能生效。)

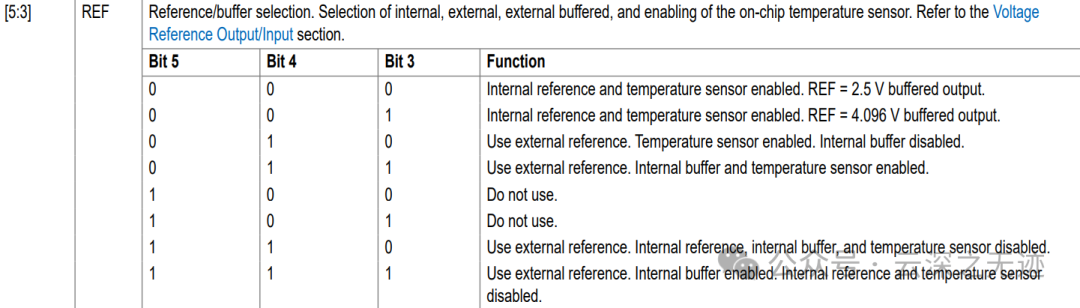

一共有6个参考的方式,直接缓冲+内部,注意寄存器里面也可以控制

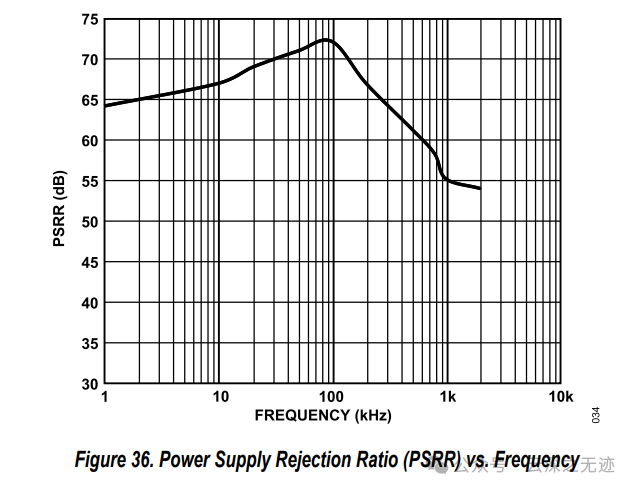

这个ADC对电源不敏感,可以电源脏一点

参考缓冲器,如AD8605,也可以对系统电源进行滤波,这个是一个新鲜的用法,第一次见到。

9-7是对通道的开闭控制,6是个滤波器

这个是我说的上面的参考方式

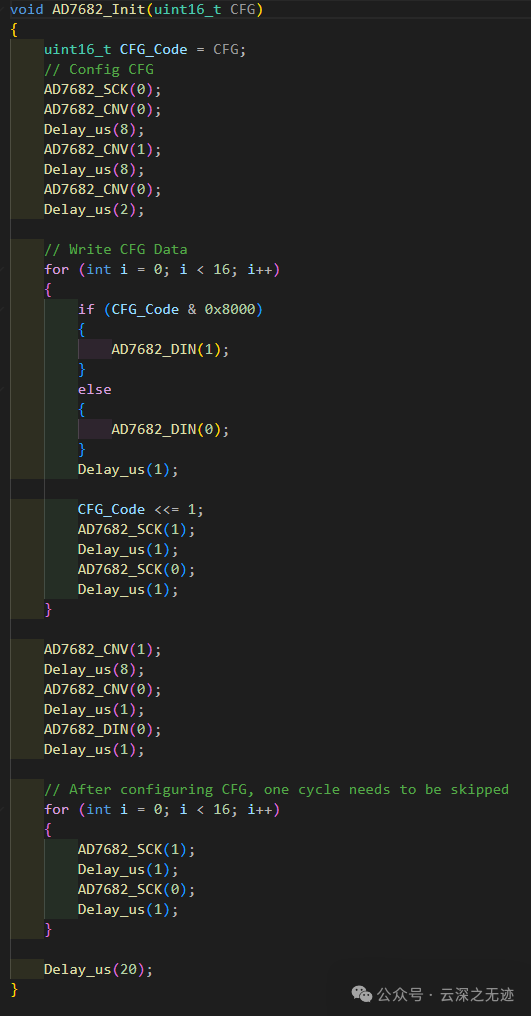

这个就是一个初始化的函数,配置成了稳定的参数形式

配置代码准备:

CFG_Code = CFG;:将外部传入的配置参数复制到本地变量CFG_Code中,方便后续操作。

开始配置序列:

AD7682_CNV(0) 和 AD7682_CNV(1):这两个函数控制转换开始信号。通过先置低后置高,将设备置于配置状态。

写入配置数据:

内层判断当前位是否为1,如果是,则将数据输入引脚置高;否则置低。

每次写入一位数据后,通过AD7682_SCK时钟信号将数据锁存。

外层循环遍历16位配置数据:

结束配置序列:

再次操作AD7682_CNV信号,完成配置序列。

跳过一个周期:

连续写入16个时钟周期,相当于跳过一个转换周期,这是AD7682的配置序列要求。

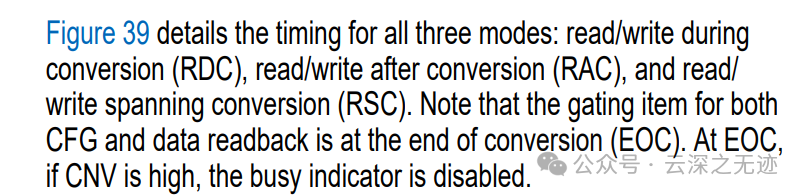

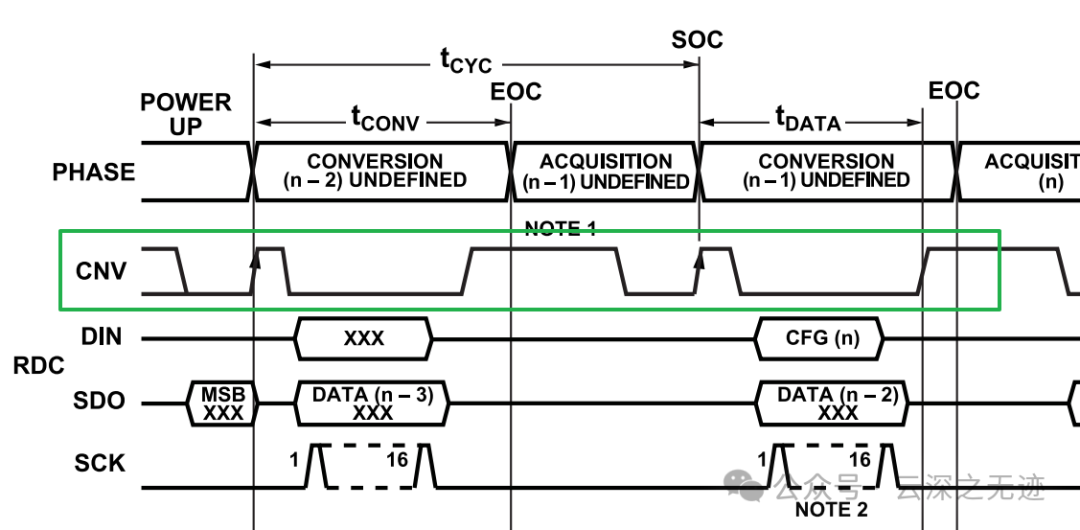

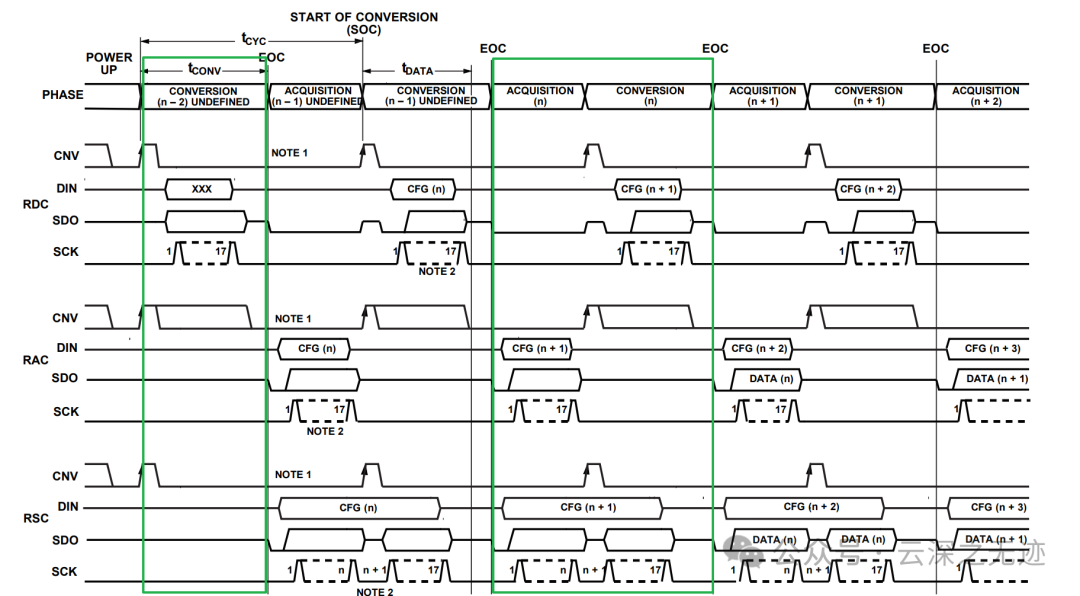

ADC的每次转换都是要读取一次CFG的,就是看看转条件是什么样的,有三种,就是还在转换的时候,就读寄存器读写,这个就是最苛刻的应用了。第二种就很轻松,转换完在读写。第三种是综合应用。

配置寄存器写入: 在每次转换开始前,需要确保CFG寄存器中的配置信息是正确的。如果在转换过程中修改了CFG寄存器,那么当前转换的结果将被丢弃。

数据读取: 数据读取可以在转换过程中、转换结束后或者跨越多个转换周期进行。读取时序需要满足特定的设置和保持时间要求。

转换过程: 转换过程包括采样、量化和编码等多个阶段。转换时间取决于ADC的采样率和分辨率。

特点: 在ADC进行转换的同时,可以对配置寄存器进行读写操作。

优势: 灵活度高,可以在数据采集过程中动态调整配置。

注意事项: 配置寄存器在转换开始前必须稳定,否则可能导致数据损坏。

应用场景: 需要频繁调整配置参数的应用,例如电机控制、数据采集等。

特点: 只有在转换完成后,才能对配置寄存器进行读写操作。

优势: 实现简单,数据完整性高。

注意事项: 灵活性较低,不能在转换过程中动态调整配置。

应用场景: 对数据完整性要求高,且配置参数不需要频繁更改的应用。

特点: 结合了RDC和RAC的优点,可以在转换过程中更新配置寄存器,但需要保证下一个转换开始前配置稳定。

优势: 灵活性和数据完整性兼顾。

注意事项: 需要仔细协调读写时序,避免数据损坏。

应用场景: 需要在转换过程中进行一些配置调整,但又需要保证数据完整性的应用。

还要在注意这个CNV信号:

CNV信号: 控制转换的开始和结束。当CNV拉低后,SDO输出位开始从MSB(最高有效位)开始移出。

和CS差不多的应用

忙指示器: 当CNV为低电平时,忙指示器被使能。通过检测忙指示器的状态,可以判断ADC是否正在进行转换。

SDO上的LSB: 由于AD7682/AD7689的转换噪声通常是4个LSB峰峰值或更大,因此SDO上的LSB在转换过程中会保持低电平50%的时间。为了确保SDO能回到高阻态,需要在转换结束后发送额外的SCK脉冲。

配置寄存器写入时机: 配置寄存器必须在转换开始前写入,否则当前转换结果将被丢弃。

看起来就很清闲

反正就是要确保信号稳定,写的时候就想想,人家在忙,如何处理你的请求也就OK了。hhh,欢迎大佬再捐两颗给我玩。

今日美图