从平面晶体管(Planar FET),到鳍式场效应晶体管(FinFET,Fin Field-Effect Transistor),再到全环绕栅或围栅(GAA,Gate-all-Around),都是为了减少漏电,降低功耗。

尽管 GAA FET技术还未获得业界大规模采用,但下一代 CFET 技术已被提上日程,这项技术被视为下一代半导体技术的重要发展方向,有望在未来实现进一步的工艺尺寸微缩。

自2004年北京大学博士张盛东在2004年的论文《A stacked CMOS technology on SOI substrate》中完成堆叠互补晶体管(stacked CMOS)的雏形。2018年imec在VLSI技术会议发表的论文《The Complementary FET (CFET) for CMOS scaling beyond N3》中提出互补场效应晶体管(CFET,Complementary FET)概念。目前,有关CFET的研究正在加快进行。

IEDM2024,台积电、IMEC、IBM、英特尔和三星等各大半导体公司的研究人员将汇聚一堂,分享关于垂直堆叠互补场效应晶体管(CFET)技术的最新研究成果。

(台积电)2.1 2nm Platform Technology featuring Energy-efficient Nanosheet Transistors and Interconnects co-optimized with 3DIC for AI, HPC and Mobile SoC Applications

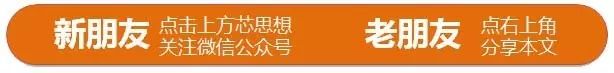

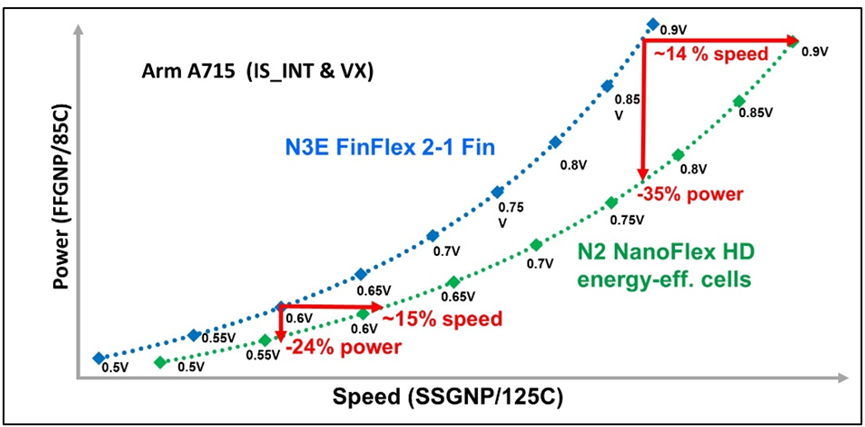

台积电在该论文中介绍了处于风险生产阶段的N2制程,这将是目前世界上最先进的工艺制程。N2表示相较N3,在相同功耗下,速度增快~15%,或在相同速度下,功耗降低~30%,同时集成度达1.15倍。新的N2平台采用GAA纳米片晶体管;具有有史以来最密集的SRAM后端互连(~38Mb/mm2);以及提供巨大设计灵活性的整体系统技术协同优化(STCO)架构。

该架构包括一个可扩展的铜基再分配层和一个平坦的钝化层(用于更好的性能、强大的CPI和无缝的3D集成);以及通过硅通孔或TSV(用于具有F2F/F2B堆叠的电源/信号)。研究人员表示,N2平台目前正在进行风险生产,计划于2025年下半年大规模生产。N2P(N2的5%速度增强版)的目标是在2025年完成资格认证,并在2026年大规模生产。

(台积电)2.5 First Demonstration of Monolithic CFET Inverter at 48nm Gate Pitch Toward Future Logic Technology Scaling

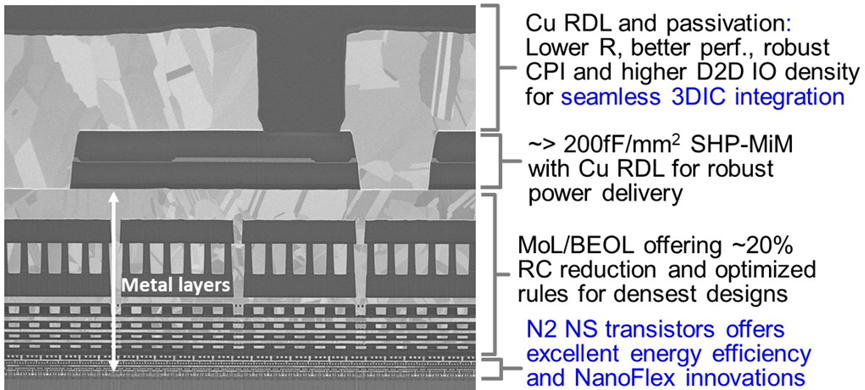

台积电研究人员Sandy Liao在IEDM2023公布了一种用于逻辑技术扩展的实用单片CFET架构方法,今年在该工作基础上。在该论文中介绍mCFET(monolithic complementary field-effect transistor)的技术进展,关键突破包括垂直偶极子图案化、垂直金属化漏极局部互连以及背侧中线接触和互连集成。

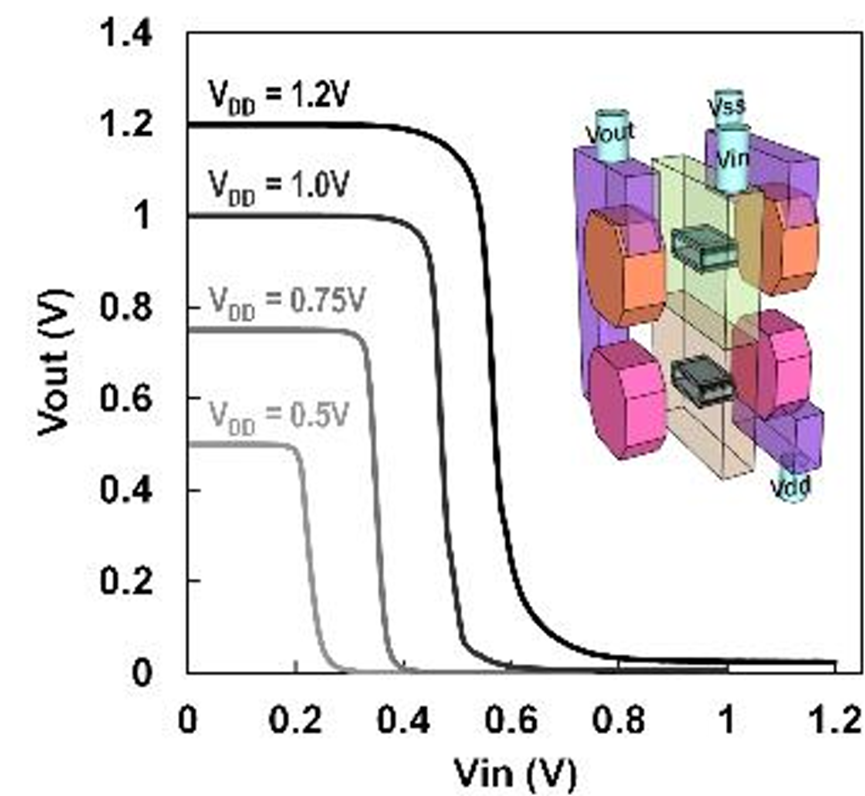

在该论文中以行业领先的48nm栅极间距构建第一个功能齐全的先进CFET反相器。该反相器由堆叠的n-FET-on-p-FET纳米片晶体管制成,现在具有背面接触和互连,以提高性能和增加设计灵活性。该反相器件在高达1.2V的电压传输特性下表现出良好的平衡,n和p器件的亚阈值斜率均为74-76mV/V。研究人员表示,这种完全可操作的CFET逆变器的成功演示标志着CFET技术进步的一个重要里程碑,为未来的逻辑技术扩展以及功率、性能、面积和成本(PPAC)属性的进步铺平了道路

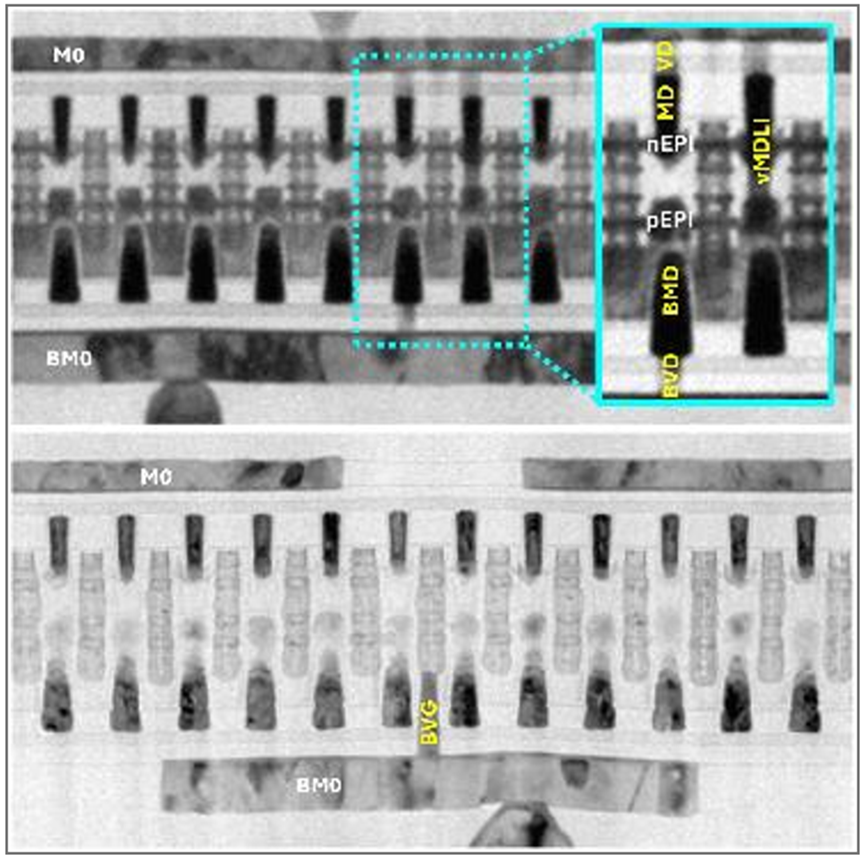

上半部分详细描述了单片CFET触点和局部互连,显示了垂直金属化漏极局部互连(vMDLI);MD和VD来自正面过程,BMD和BVD来自背面过程;下半部分重点介绍了BVG的实现

显示单片CFET逆变器在VDD=1.2 V下的电压传输特性

(英特尔)2.2 Silicon RibbonFET CMOS at 6nm Gate Length

英特尔在该论文中展示了栅极长度(LG)为6nm的RibbonFET CMOS晶体管特性,Nanoribbon的Si层厚度缩放被证明可以改善短沟道效应,而不会对3nm以下的性能造成损失,

为了证明摩尔定律未死,英特尔提出超级缩放晶体管概念。英特尔的研究人员将证明,硅可以继续支持未来技术节点所需的极端栅极长度缩放。他们将描述如何在45nm接触多晶硅间距(CPP,相邻晶体管栅极之间的间距)下构建栅极长度为6nm的RibbonFET CMOS晶体管(英特尔版本的纳米片),而不会降低电子迁移率(电子在材料中的移动速度)。研究人员将证明,电子迁移率在3nm Tsi(硅厚度)之前不会降低,低于3nm时,由于表面粗糙度导致的电子散射成为一个问题。他们将描述他们如何通过巧妙的功函数工程在这些栅极长度下以极低的阈值电压实现良好的短沟道控制(在<4nm Tsi时≤100mV/V)。这项工作表明,3nm是RibbonFET的实际缩放限制。

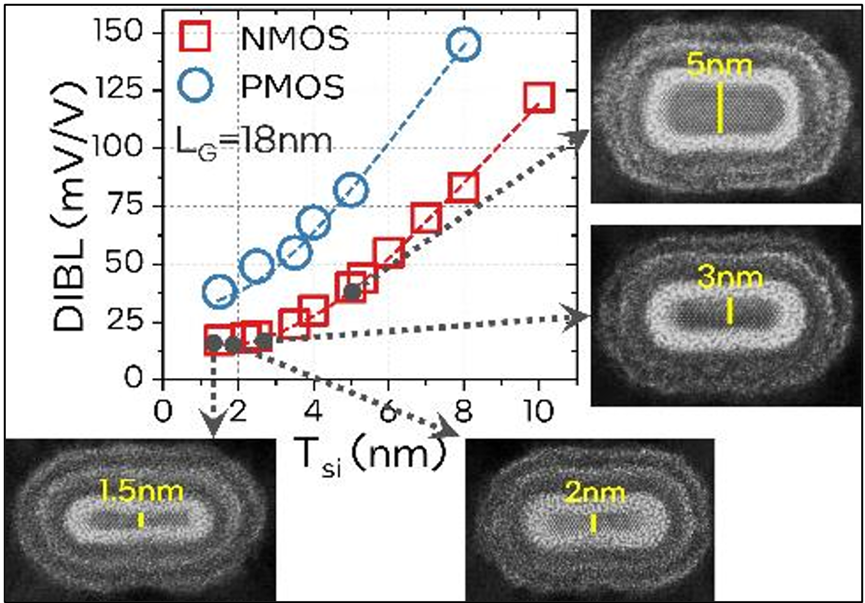

显示了LG=18nm时漏极诱导势垒降低(DIBL)与硅厚度(Tsi)的关系。当Tsi从10nm缩放到1.5nm时,它显示出减少;然而DIBL还原在Tsi<4nm处饱和,低于该值时获得的增益很小。在相同的Tsi下,PMOS DIBL相对于NMOS DIBL升高;显示了具有低至1.5nm的各种Tsi值的1NR晶体管的TEM显微照片

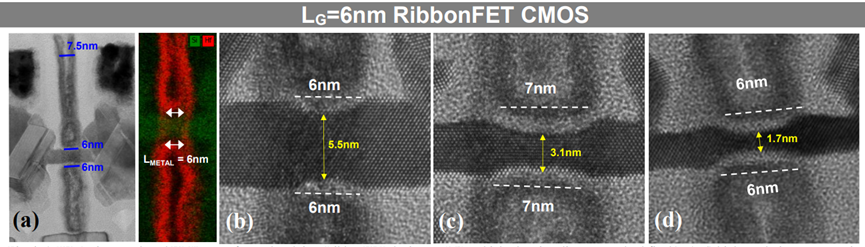

(a)1NR 6nm RibbonFET器件的TEM显微照片和EDX扫描

(b-d)1NR 6nm栅极长度下Tsi=5.5nm、3.1nm和1.7nm的高分辨率横截面TEM

(imec)2.4 Double-Row CFET: Design Technology Co-Optimization for Area Efficient A7 Technology Node

imec在该论文中指出CFET器件架构有望在后FinFET时代实现功率、性能和面积可扩展性,double-row CFET较middle-of-line工艺简单,且有40%的面积和约12%的功率扩展潜力。

(IBM)2.8 Monolithic Stacked FET with Stepped Channels for Future Logic Technologies

IBM在该论文中提出了一种单片堆叠FET架构,其特征是阶梯式沟道结构,其中底部FET沟道比顶部宽。这种设计通过降低总堆叠高度来缓解高纵横比工艺的挑战,并且与相同占地面积下的均匀沟道宽度对应物相比,提供了更好的性能。除了阶梯式沟道外,我们的集成硬件工作还具有上下沟道中介电隔离、上下源极/漏极隔离和双功函数金属的特点。随着先进技术面临着巨大的功率、性能和面积缩放压力,这项工作将狭窄的道路扩展到纳米片架构之外。