大家好,今天我们来聊一聊在电子工程中常常遇到的谐振电路设计及其复杂性。无论你是初学者还是经验丰富的工程师,相信这篇文章都会为你带来一些新的见解。

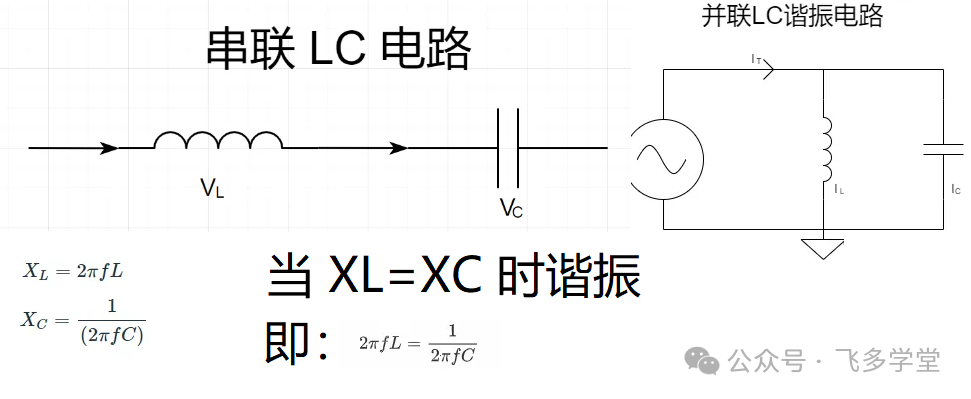

在 LC 谐振电路 一文中,我们了解了电感和电容的性质及其电压和电流之间的相位关系。通过这些基础知识,我们进一步探讨了如何将电感和电容组合成串联和并联电路,并且在谐振频率下会发生什么。在谐振频率(即使得感抗等于容抗时的频率)下,串联谐振电路看起来像是短路,而并联谐振电路理想情况下则看起来像是开路。然而,这一切都只是在“理想情况下”成立。本文将深入探讨,现实世界的非理想因素将会如何影响谐振电路。

在现实中,各种元件都不可避免地有寄生效应。所有电子元器件都会有寄生属性,这是由组件的物理结构和材料决定的。

元件引脚引入电感。

电子元件引脚是一段导线,通常有一定的电感,对于在高频下工作的电路,这可能非常重要.

举个例子,一段 5 厘米长的 0.6 毫米直径(22 AWG)导线大约有 50nH 的电感,只是简单的一段直导线,不需要绕圈。在某些频率下,这可能很重要

导线电感计算:https://www.allaboutcircuits.com/tools/wire-self-inductance-calculator/

元件引脚引入电阻

导线和端子自身的电阻在高频操作时也不能忽略。

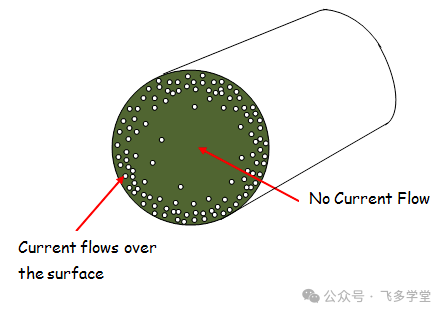

集肤效应(Skin Effect)

当频率升高时,电流会集中在导体的表面,这使得高频下的阻抗比低频下要大。

集肤效应是指当操作频率升高时,电流开始集中在导体的表面或外缘,而离开导体中心。这在导线横截面为圆形或印刷电路板上的导线时尤为明显。

这个现象有多明显?举一个实际数字。在 1MHz 频率下,铜导线的集肤深度约为 0.07 毫米。以 0.6 毫米直径的导线为例,这意味着电流集中在导线外部约10%的区域,这就像导线变细了一样。因此,电阻损耗随频率的增加而上升,这必须在设计高频电路时考虑。

绝缘层并非完美无缺,它们存在泄漏。

可以视之为一个具有较高阻值的电阻。绝缘层也有一些频率相关的损耗。

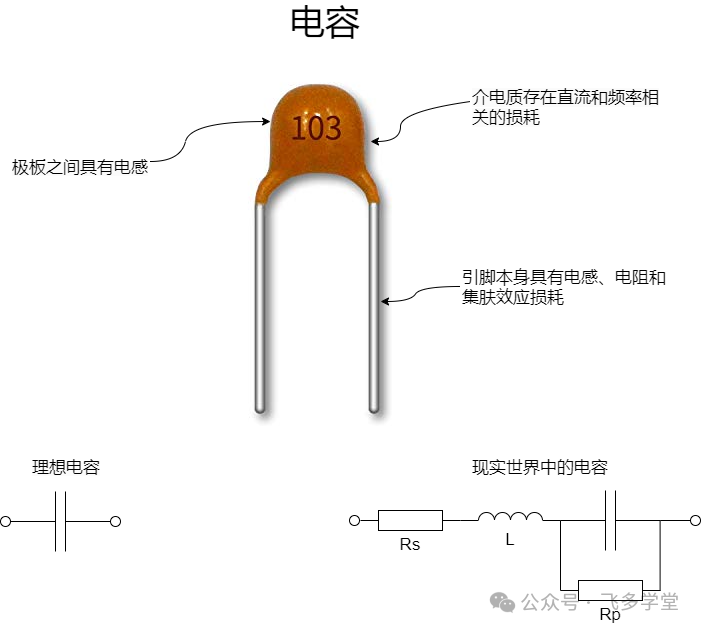

电容和电感等元件的物理结构会影响上面寄生属性的大小。

电容的引脚具有有寄生电感和电阻。电介质可能会有频率相关的损耗和泄漏,可以将其建模为跨接在电容两个极板之间的大阻值电阻。另外,电容的两个极板之间也可能存在电感,这使得真实电容远没有理想模型那么简单。

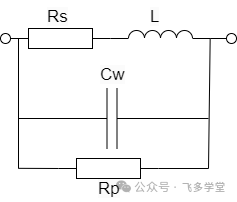

Rp 是一个大阻值的电阻,建模自两个极板之间漏电流以及频率相关的损耗, p来自并联的英文单词 parallel, 。

L 是电容引脚导入的电感,以及两个极板之间的电感。

Rs 建模自引脚电阻以及频率相关的集肤效应损耗,s 来自串联的英文单词 serial, 。

上面这些寄生属性中对电容影响最大的是串联寄生电感 L。当频率上升时,容抗变小,但感抗变大。在频率上升到某一个点,容抗和电感抗相等,导致电容自谐振(self resonance)。当频率高于自谐振频率,电容逐渐失效,表现的越来越像电感。

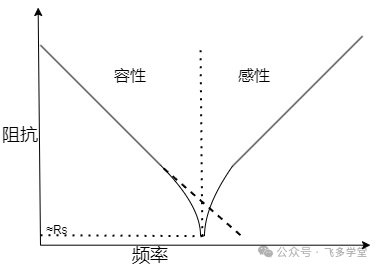

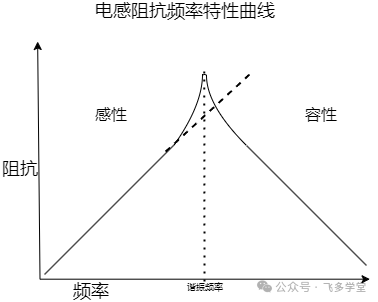

上图是电容的阻抗-频率特性曲线。横轴是频率,纵轴是阻抗。理想情况下,阻抗随着频率的增加而减小。而在实际情况下,随着频率增加,感抗越来越大,容抗越来越小,发生自谐振,导致整体阻抗下降。理想情况下,阻抗会降到零欧姆,但由于频率相关的集肤效应和直流电阻损耗,阻抗不会降到零,而是会先下降再上升,使得电容在其自谐振频率以上时表现的像电感,这家伙叛变了。

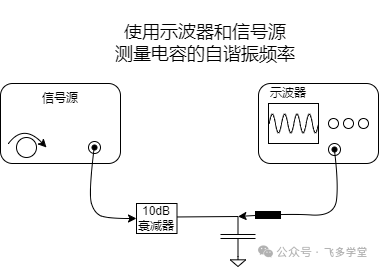

测量自谐振频率的方法很简单。我们需要一个信号发生器,通过一个10 dB或20 dB的衰减器(或者直接连接)将信号发送到电容,然后用示波器测量电容两端的电压。

测量电路如下:

使用衰减器是为了让信号发生器不会受到电容在不同频率信号下阻抗不同的影响,让信号源看到一个恒定的阻抗。然而,你也可以不使用衰减器,直接将信号发生器连接到电容。

在低频时,电容的容抗较高,你会看到较高的峰峰值。随着频率上升,电容的容抗下降,信号的峰峰值会下降。当频率上升到某一点时,峰峰值达到最低,此时的输入信号频率就是自谐振频率。超过自谐振频率后,信号的峰峰值会逐渐变大。

下面是信号源的设置:

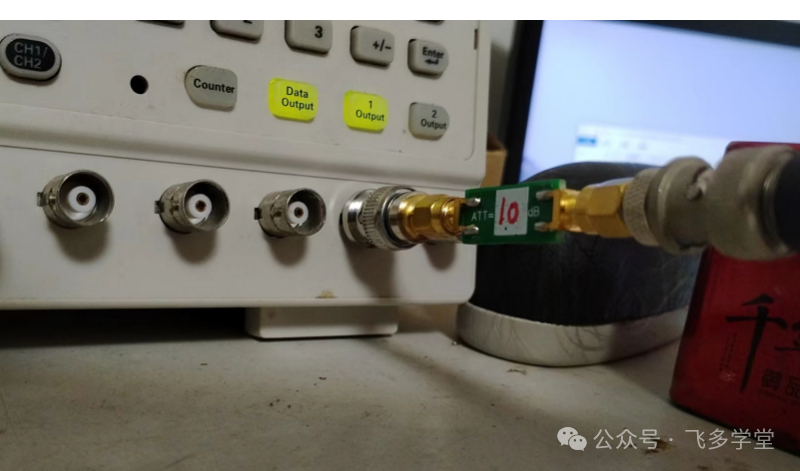

我在信号源的输出位置接了一个 10dB 的衰减器:

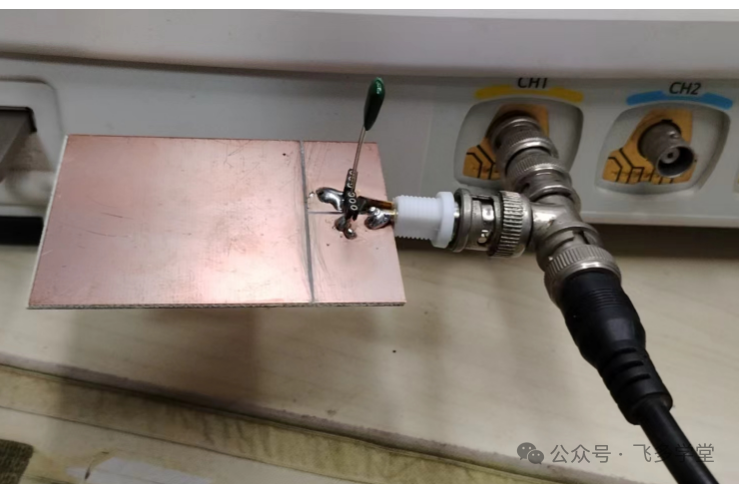

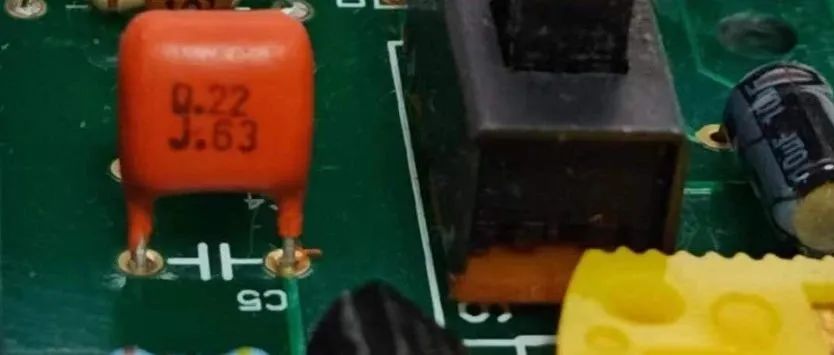

下面是我自己焊接的简单直插器件接口,上面插的是 103 10nF 的涤纶电容:

我们逐步调整信号发生器的频率,观察示波器上的信号变化。

可见,随着输入信号频率的增加,输出信号峰峰值逐渐降低,当频率增加到 8 MHz 左右时,输出信号电压达到最低点,这就是该电容的自谐振频率。之后,我们继续增大信号频率,信号幅度又逐渐增大。这里可以来回反复多次测量以取得最佳结果。

我们实验的电容 10nF 涤纶电容引脚直径为 0.46 毫米, 两个引脚长度合起来为 4 厘米,如果考虑插座等其他因素我们算总的长度为 5 厘米,计算电感为 53 nH。

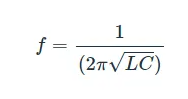

如果我们使用 10nF 和 53nH 这两个参数,用下面的公式:

计算谐振频率为:6.9 MHz。

计算的结果为 6.9 MHz,接近于我们用示波器测量的 8 MHz。

当你用仪器测量出的结果和理论计算的结果相符时,你会发现:冷冰冰的公式是有生命的!

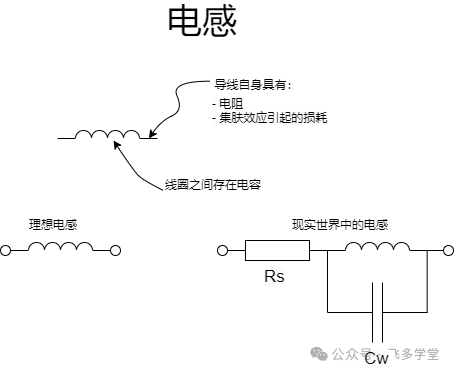

类似地,电感也有现实世界中的问题。电感是一根导线绕在磁芯上,线圈和线圈之间会有电容存在,导线本身也有电阻,还有集肤效应引起的等效电阻。

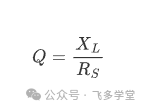

电感的Q值衡量其质量,Q值是电感电抗与串联电阻的比值:

因为串联电阻很小,理想情况下Q值应该很高。

较少的匝数或间距可以减少绕组间电容。使用磁性核心如铁氧体或粉末铁可以减少实现同样电感值所需的匝数。但是,导入磁性核心会增加另一个损耗项,即频率和电流相关的损耗。考虑到新增加的这个损耗,现实世界的电感模型如下:

电感的阻抗频率特性曲线图如下:

简单说,电感的阻抗理想情况下会随着频率增加而增加,但现实世界中,在某个点上,寄生电容与电感并联,形成一个并联谐振电路,阻抗急剧上升。当频率大于谐振频率时,阻抗开始降低,电感看起来像电容,它也叛变了。

总而言之,设计谐振电路远非单纯的公式计算。真实世界的复杂性使得我们必须综合考虑元器件的各种寄生效应和具体应用要求。这需要工程师们具备深入的理解和实际操作经验。希望这篇文章能够为大家在设计电感和电容相关电路时提供一些有用的参考。感谢阅读,我们下次再见!

绝密!双十一电子人买课清单泄露,马上删!

拆解一款测量范围从-50℃到750℃的数字温度表

为什么PCB设计完成后需要放置mark点