我羡慕很多公司,但最羡慕的不是那种巨无霸的公司,而是小而美,在一个高端领域“唯我独尊”的公司,今天说的公司就是:

在侵入式脑机芯片领域可以唯一买到的芯片

不要说什么马克斯的东西牛逼,他的脑机芯片有几个买到的,有几个用到的?

NeuraLink-N1神经网络芯片设计细节

NeuraLink植入式系统解读

我的意思是,说的再厉害,更多的人用不到,当然你说什么都是你对,对对对,你说的对。

这个就是鄙人的榜样了,创始人

当然了,芯片都流片了,就买货就行,当然可以不去再开发

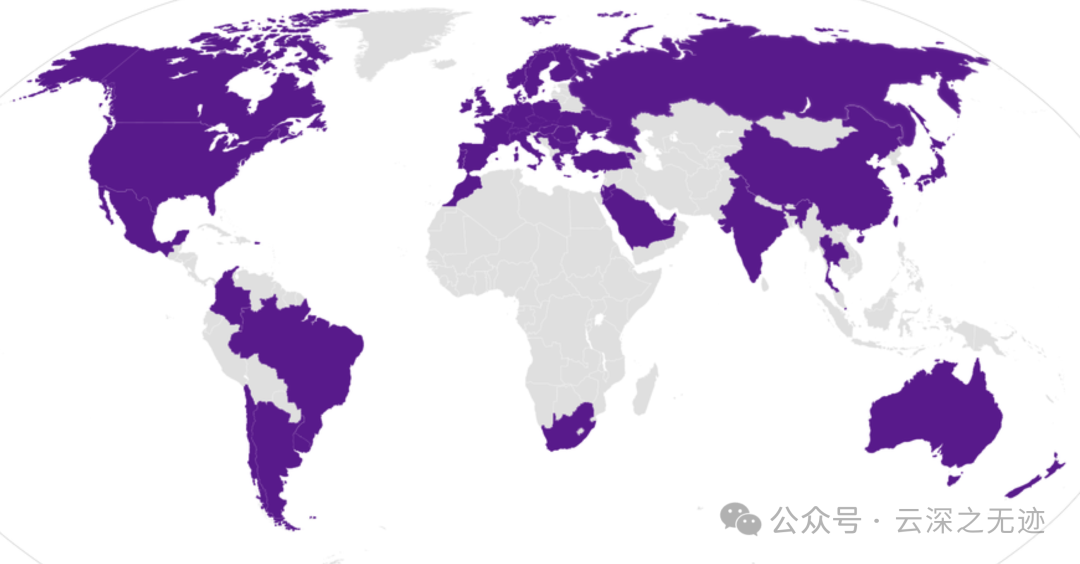

服务了六大洲五十个国家

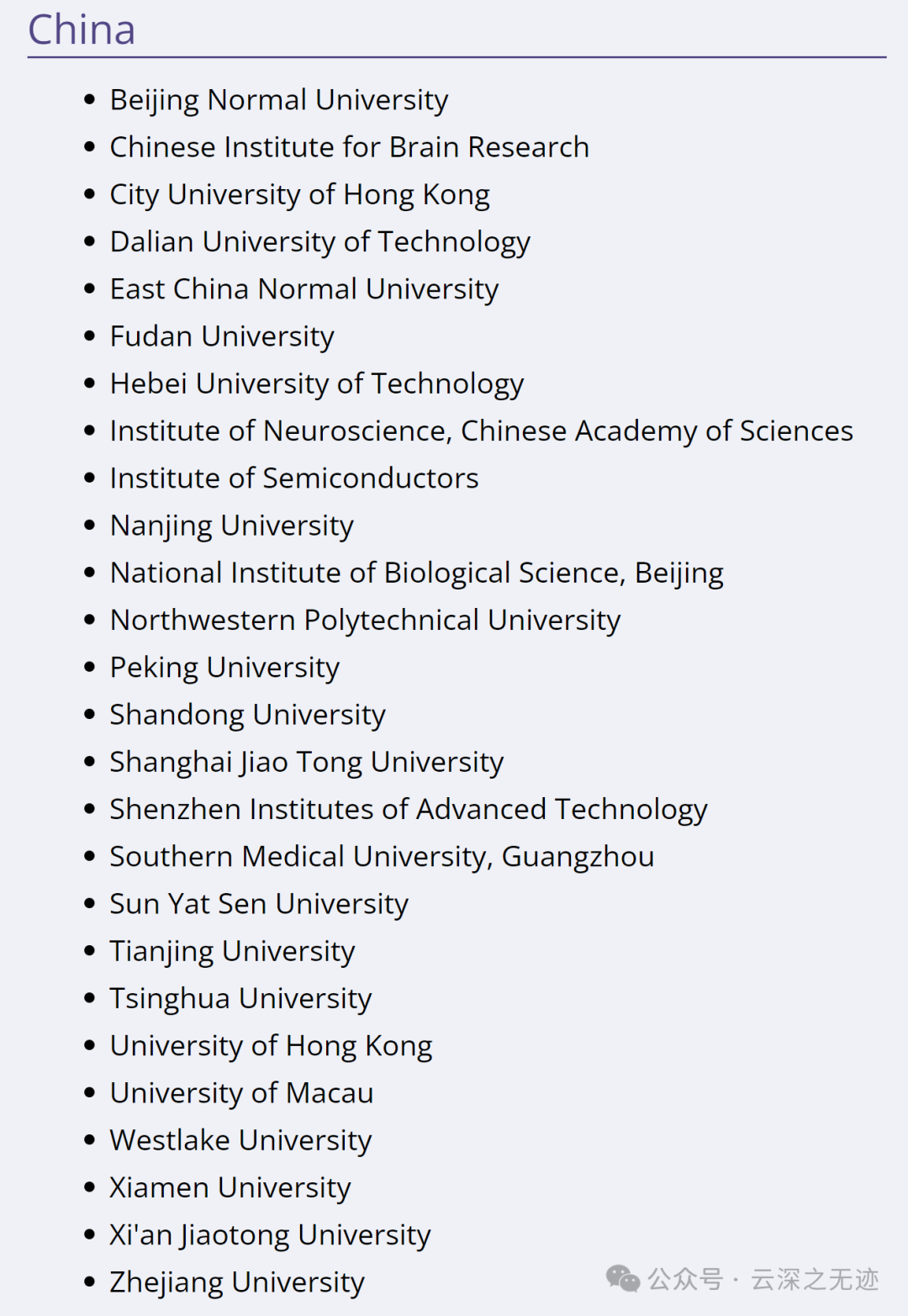

国内也有很多的科研机构在用

我接触也是因为中科院的一位朋友在使用它,然后我也上车了,感觉在里面可以学到的东西有很多。

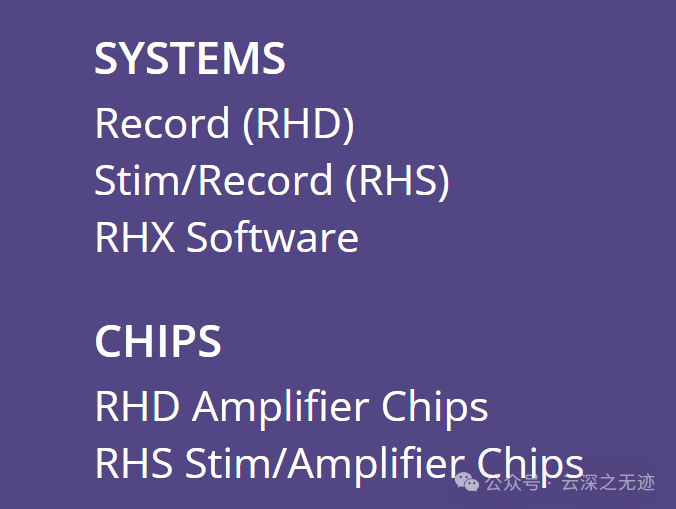

其实它主要就是两个大类,采集和刺激,然后围绕着这个给出了系统的方案。

采集

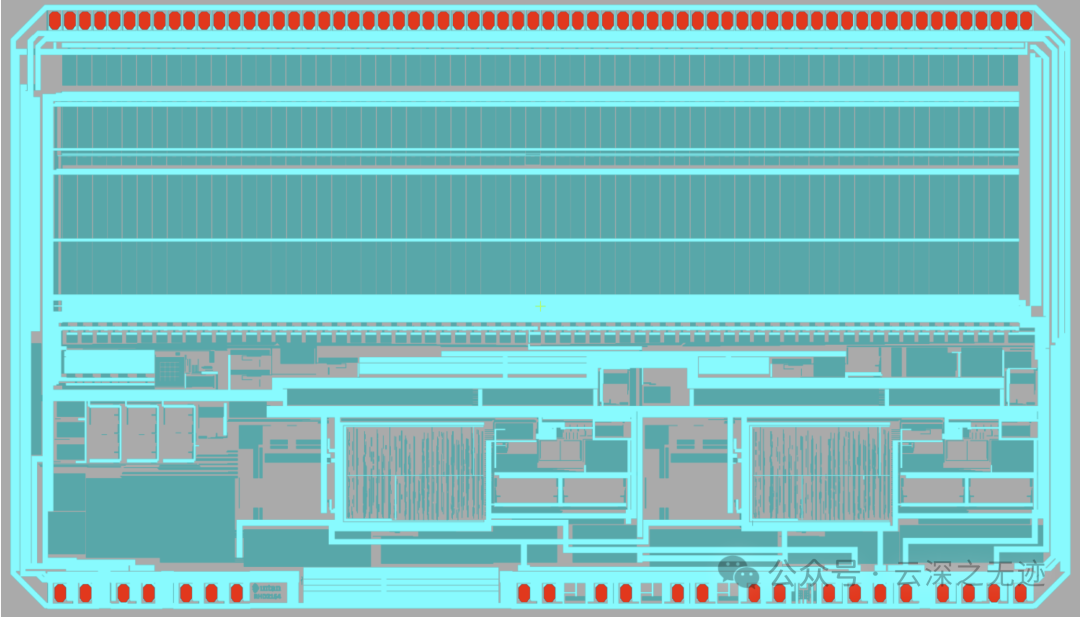

下面应该是数字组件,我也不是很懂芯片

下面应该是数字组件,我也不是很懂芯片

刺激

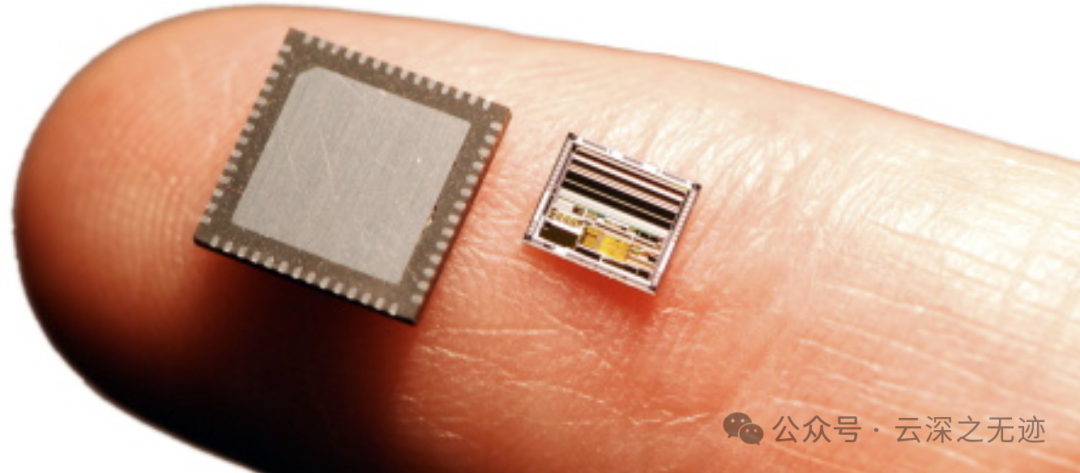

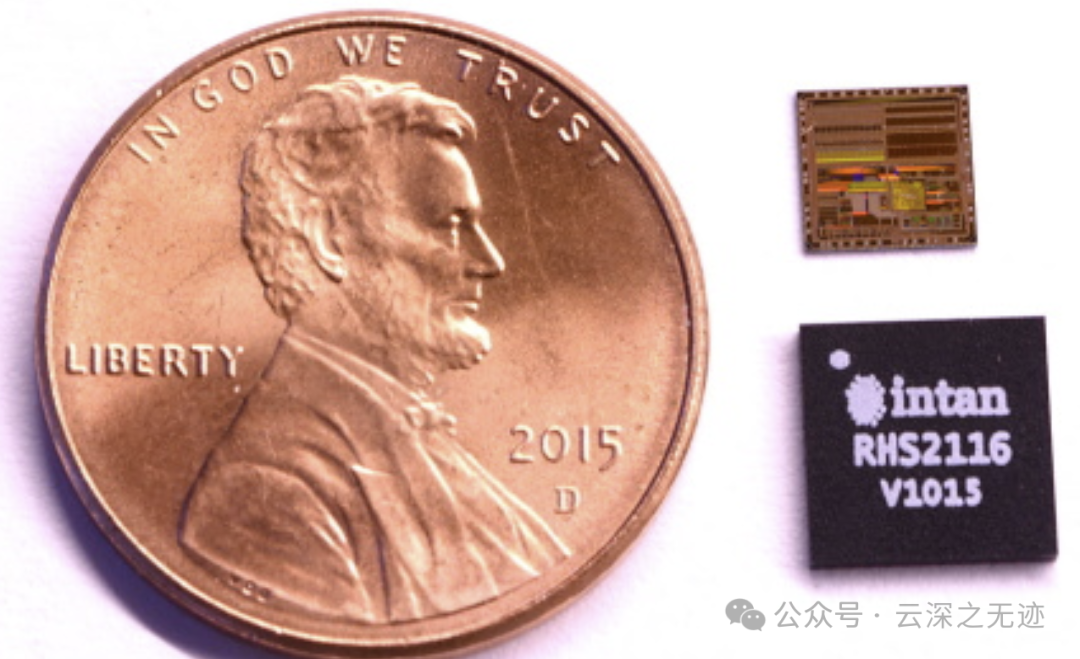

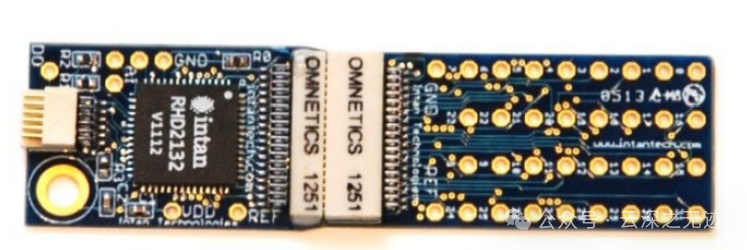

封装很小

采集uV级别的心电信号

使用胸部的 Ag/AgCl 电极。放大器配置为下截止频率为 0.6 Hz,上截止频率为 100 Hz。ADC 采样率为每通道 2 kS/s。

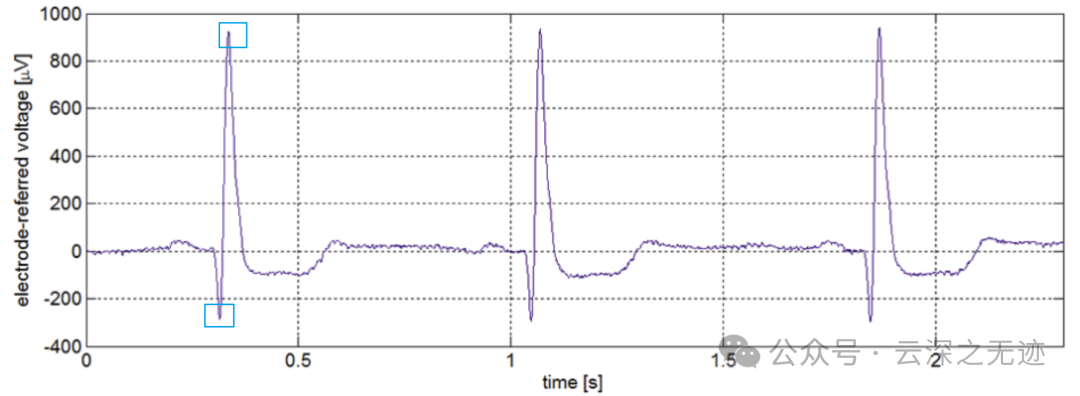

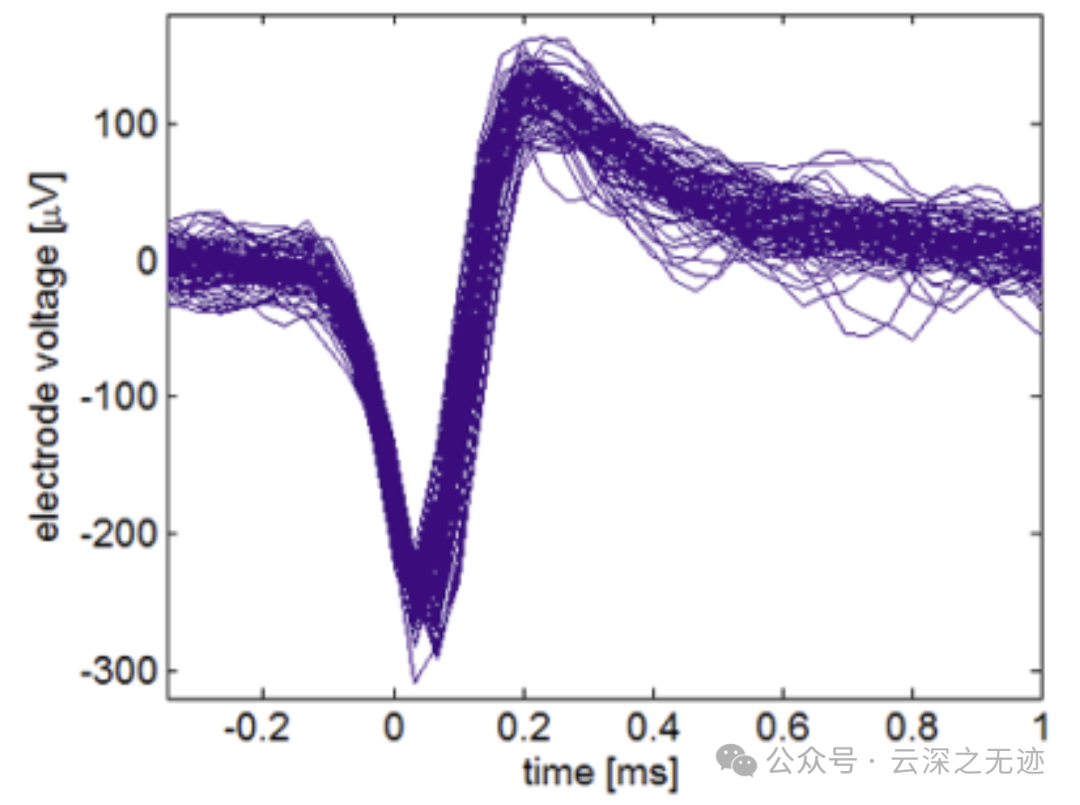

多个时间对齐的皮质动作电位,1s内对齐

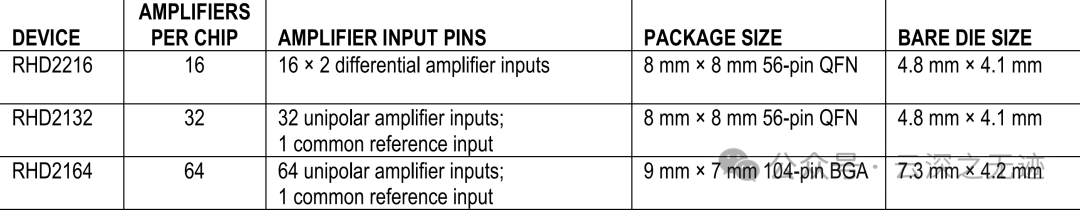

先看一个芯片的数据:

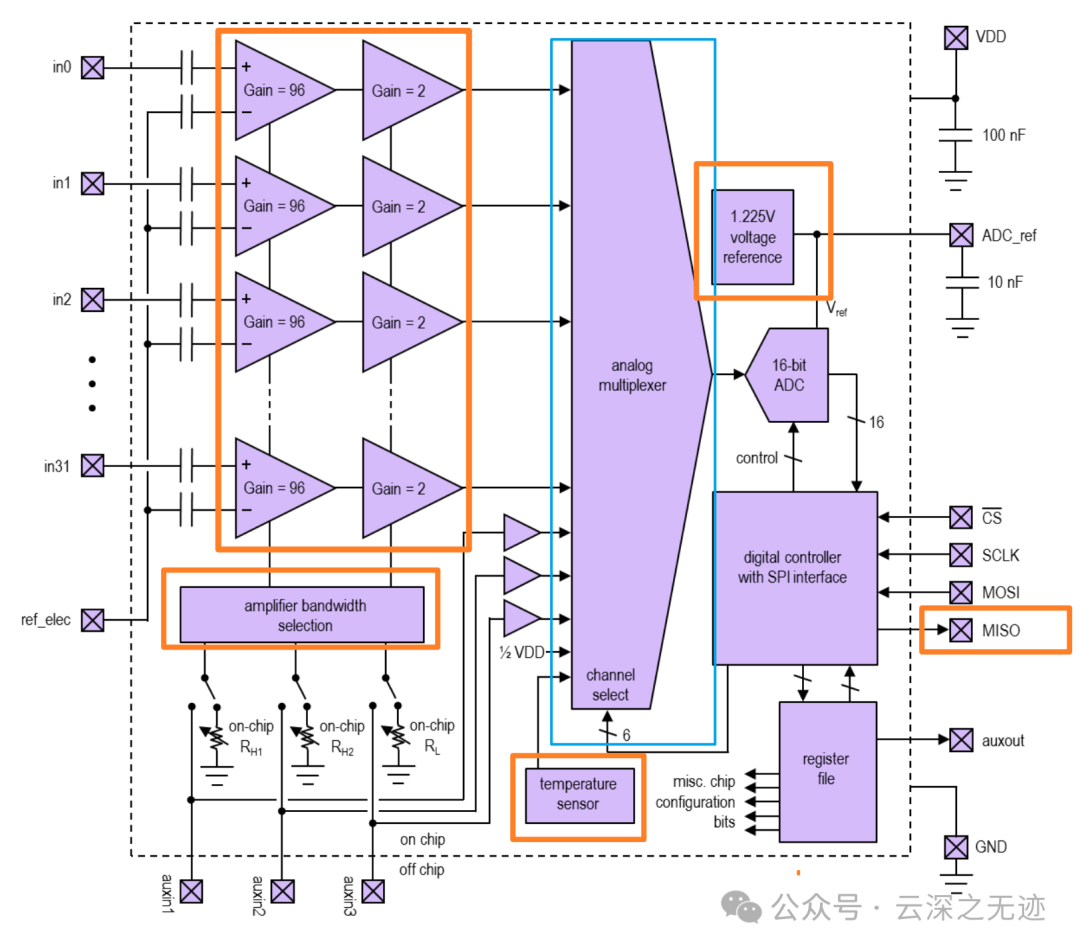

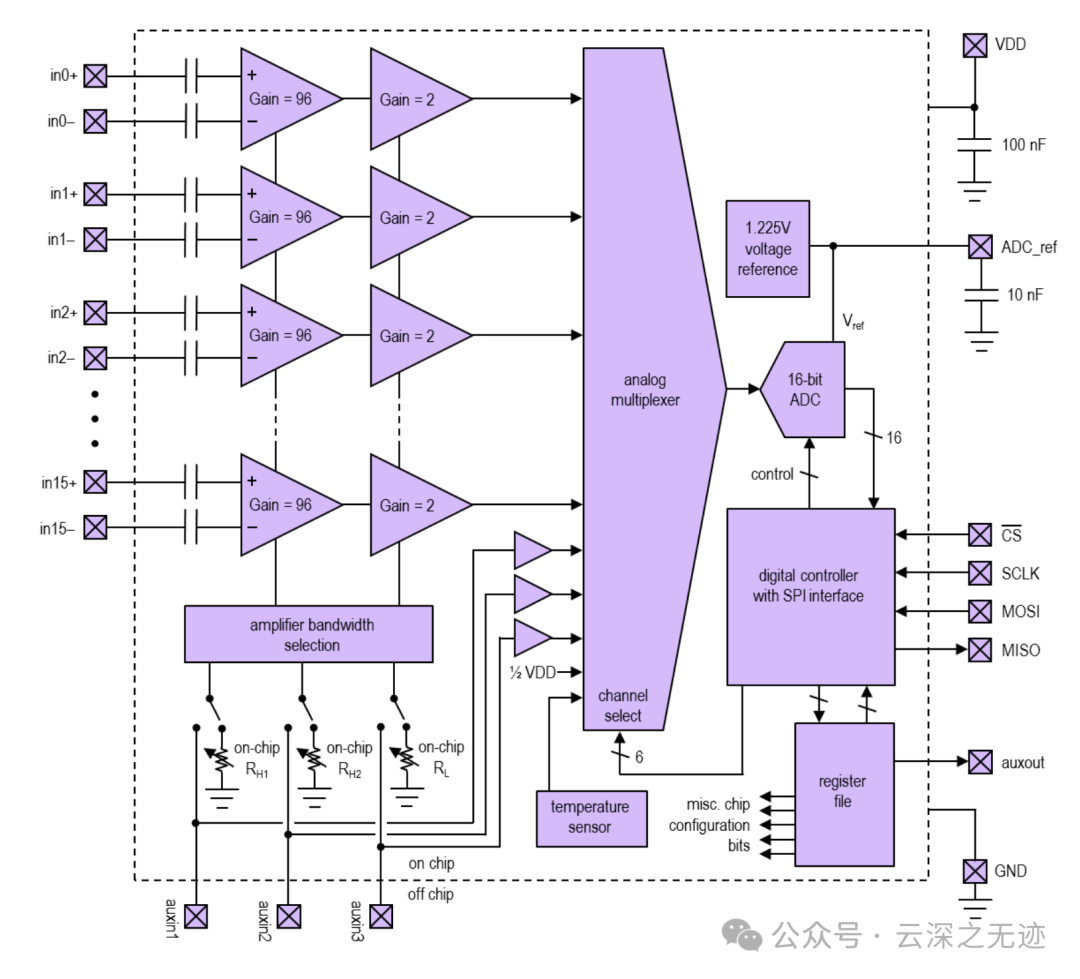

首先是一个俩级放大的OP结构,第一级的放大倍数很大。可以看到是交流耦合,前级电容,后面通过一个MUX转换,非同步采集,我以为是同步捏,滤镜没有了。。。

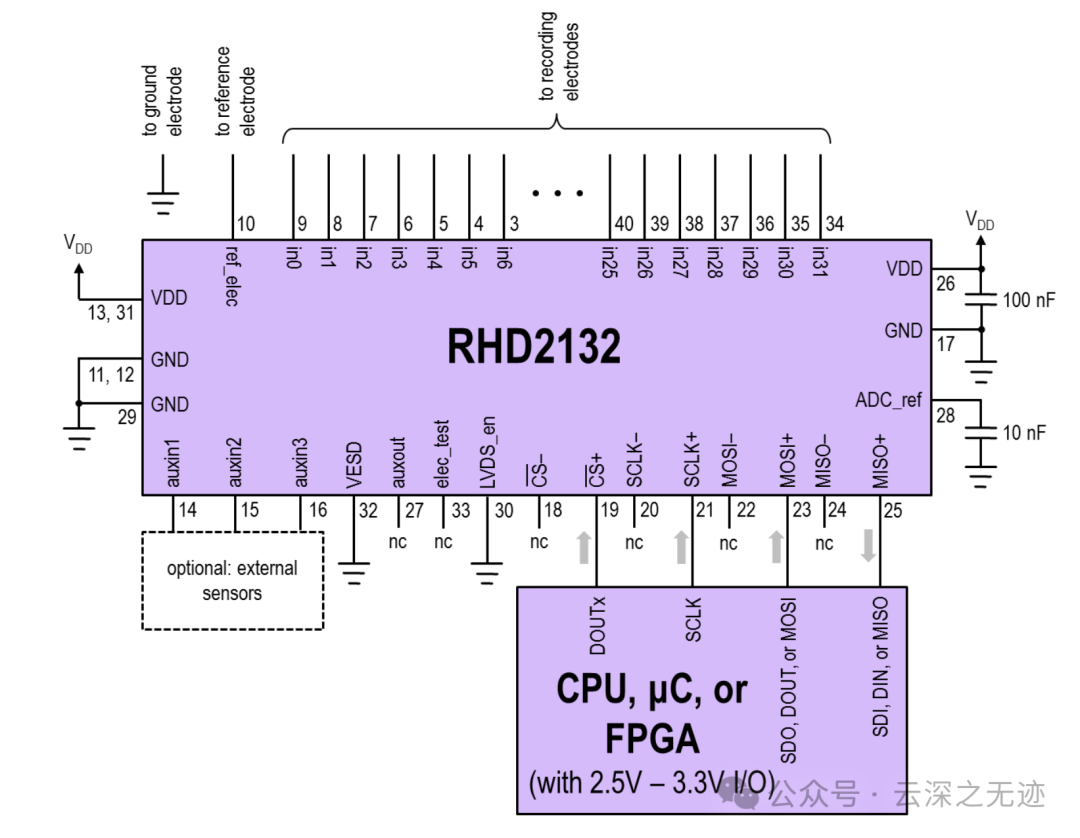

然后还有一个温度传感器,可以看到还有一个1.25的参考,所以这个东西的范围应该就是0~3.3V,然后接的是一个16bit的ADC,去掉一个误差位,那就是15bit,后级就是一个数字模块了,SPI闪亮登场。

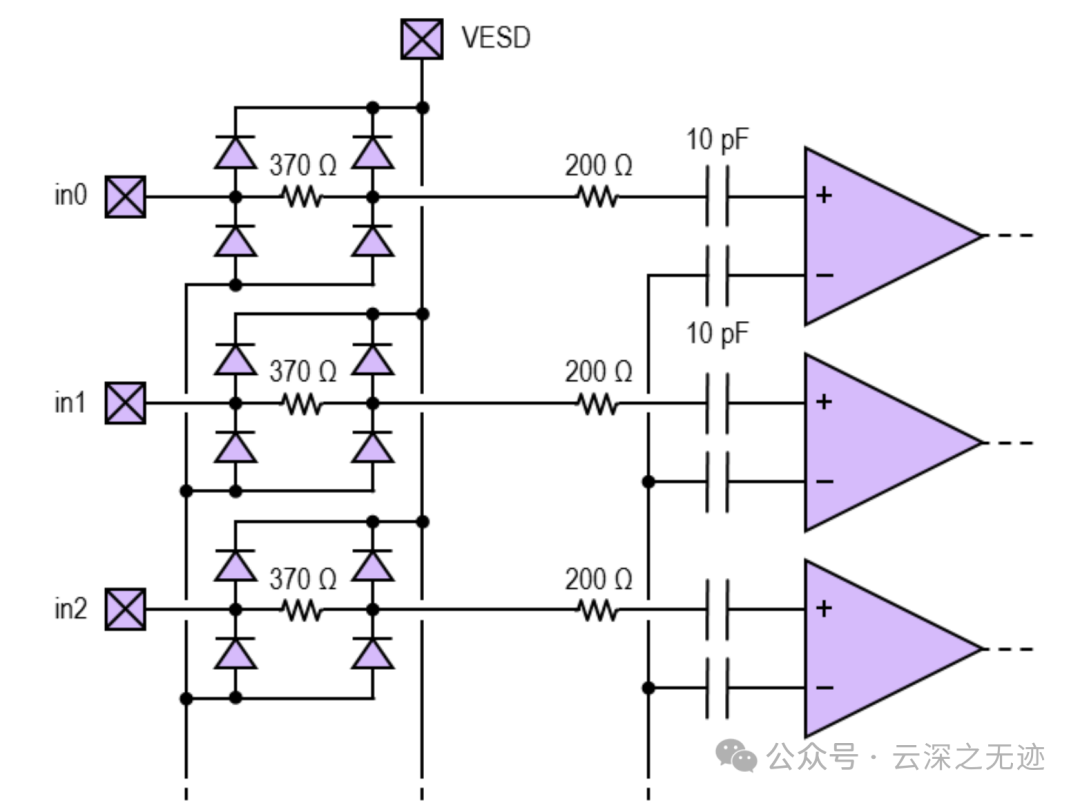

前级有ESD的保护级

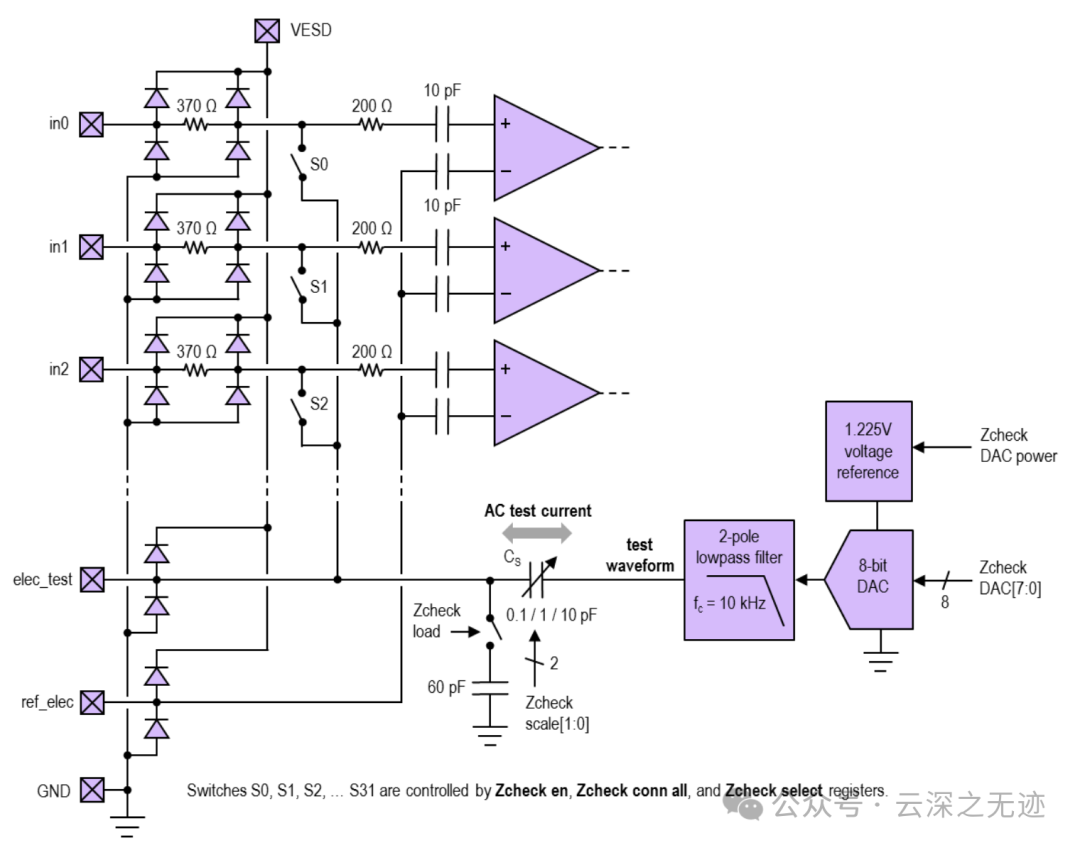

阻抗测试

RHD2000芯片集成了一个用于生成用户指定交流电流波形的电路。这个电路可以向任意选择的电极注入特定的交流电流波形,主要用于阻抗测试等目的。

数字-模拟转换 (DAC): 芯片内部有一个8位DAC,通过SPI接口可以设置其输出电压。

低通滤波器: DAC输出的数字阶梯波形经过一个二阶10kHz低通滤波器,滤除高频噪声,得到相对平滑的模拟信号。

电流转换: 滤波后的模拟信号通过一个可选择的电容(0.1pF, 1pF, 10pF)连接到测试电极。这个电容将电压转换为电流,从而在电极上产生交流电流。

波形控制: 通过SPI接口可以设置DAC的输出电压,从而控制注入到电极的电流幅值和波形。

DAC输出电压范围: 0V至1.22V,步进为4.785mV。

低通滤波器截止频率: 10kHz。

可选择电容值: 0.1pF, 1pF, 10pF。

波形控制: 可以产生近似正弦波、方波等波形。

以上是参数细节

16通道的也是一样的

因为通道很多

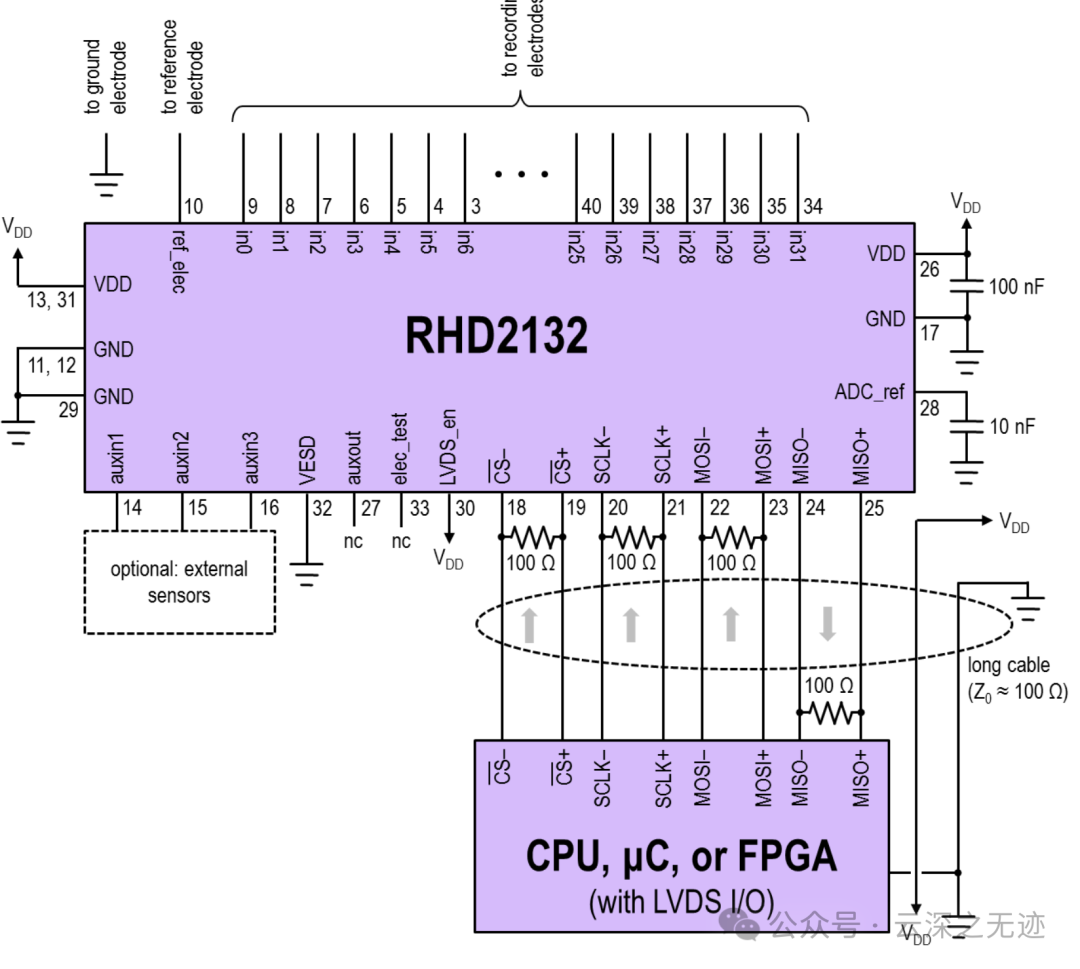

LVDS模式的优势:

高速传输:适合高速数据传输场景。

抗干扰能力强:适用于噪声较大的环境。

长距离传输:适用于长距离通信。

选择模式的考虑因素:

数据传输速率:高速率选择LVDS,低速率选择CMOS。

抗干扰要求:对噪声敏感的场合选择LVDS。

系统复杂度:LVDS实现相对复杂,CMOS更简单

因为精密信号对干扰非常敏感,这里当然不全是这个原因,主要是后端输出的信号有点大,就使用了LVDS了,这种差分信号又快干扰又小。当然为了兼顾开发,也有SPI。

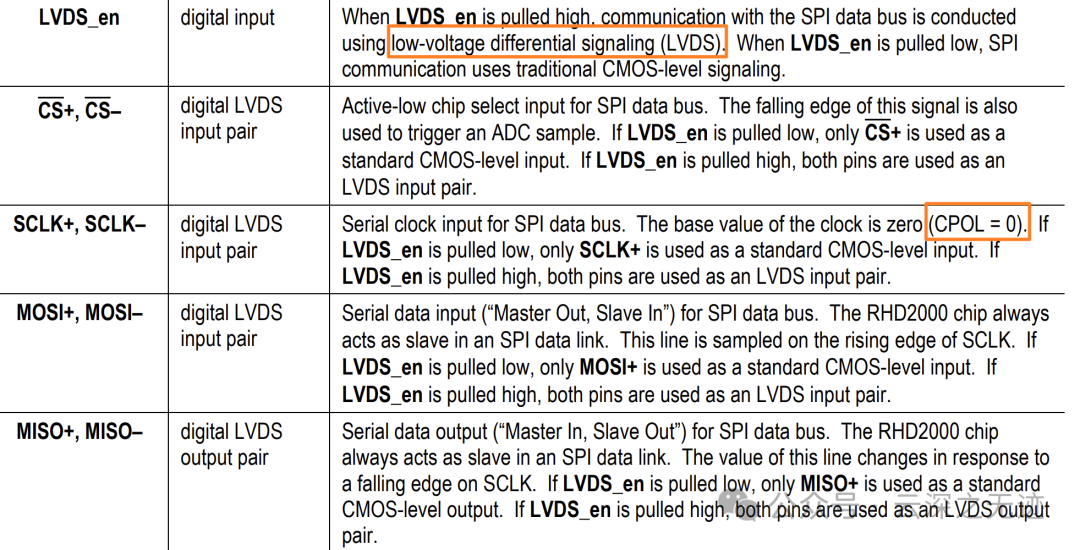

LVDS_en:

功能: 用于控制SPI接口的工作模式。

高电平有效: 当LVDS_en为高电平时,SPI接口采用LVDS模式进行通信。LVDS是一种高速、低功耗的差分信号传输方式,具有抗干扰能力强等优点。

低电平有效: 当LVDS_en为低电平时,SPI接口采用传统的CMOS电平信号进行通信。

CS+、CS-:

功能: 芯片选择的输入信号,用于激活SPI器件。

LVDS模式: 当LVDS_en为高电平时,CS+和CS-构成一个LVDS差分对,共同作为芯片选择的输入。

CMOS模式: 当LVDS_en为低电平时,仅使用CS+作为标准的CMOS电平输入。

SCLK+、SCLK-:

功能: SPI接口的串行时钟信号。

LVDS模式: 当LVDS_en为高电平时,SCLK+和SCLK-构成一个LVDS差分对,作为串行时钟输入。

CMOS模式: 当LVDS_en为低电平时,仅使用SCLK+作为标准的CMOS电平输入。

MOSI+、MOSI-:

功能: 主机向从机发送数据的串行数据输入。

LVDS模式: 当LVDS_en为高电平时,MOSI+和MOSI-构成一个LVDS差分对,作为串行数据输入。

CMOS模式: 当LVDS_en为低电平时,仅使用MOSI+作为标准的CMOS电平输入。

MISO+、MISO-:

功能: 从机向主机发送数据的串行数据输出。

LVDS模式: 当LVDS_en为高电平时,MISO+和MISO-构成一个LVDS差分对,作为串行数据输出。

CMOS模式: 当LVDS_en为低电平时,仅使用MISO+作为标准的CMOS电平输出。

CPOL=0: 表示时钟的空闲状态为低电平。

RHD2000 chip always acts as slave: 表示该芯片在SPI通信中始终作为从机。

LVDS差分信号: LVDS信号通过一对差分信号线传输,通过比较两条线的电压差来恢复数据,从而提高抗噪声能力。

俩种传输

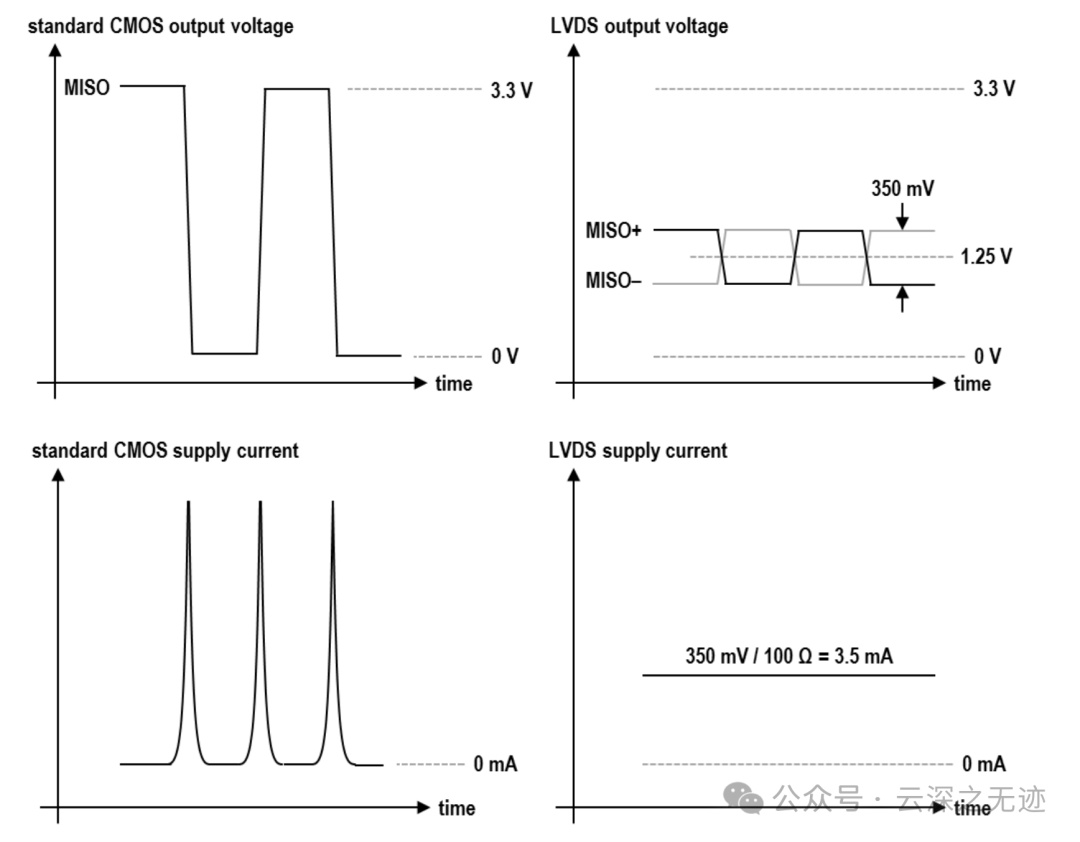

电压波形:

标准CMOS: 输出电压在高低电平之间切换,幅度接近电源电压。

LVDS: 输出电压是差分信号,即MISO+和MISO-之间存在一个固定差值(350mV)。每个信号的绝对值较低,通常在电源电压的1/2左右。

电流波形:

标准CMOS: 输出电流在高低电平切换时会有较大的变化,导致较高的功耗。

LVDS: 由于采用差分信号,输出电流相对较小且稳定,功耗较低。

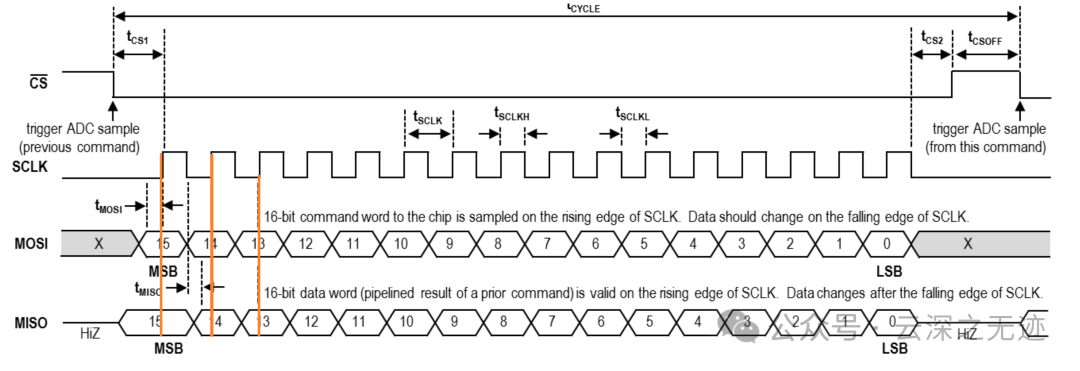

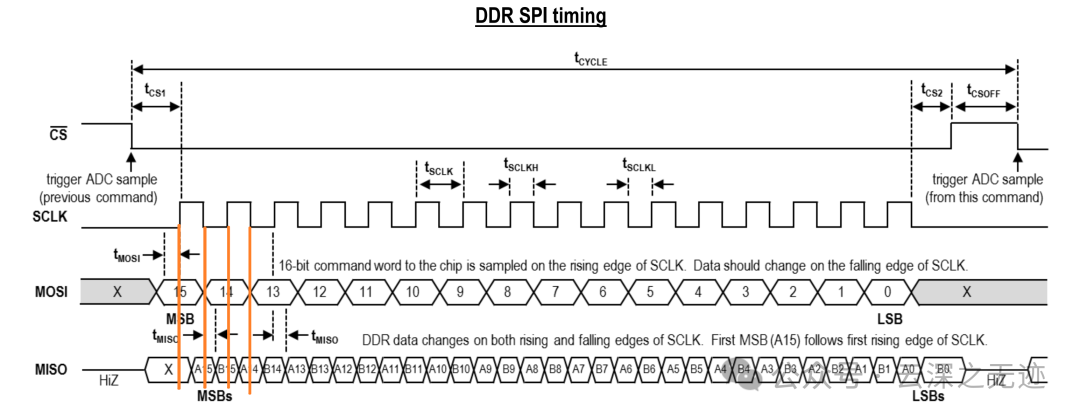

这里需要注意一点是,这个SPI不是我们平常使用的SPI,而是DDR,叫双倍率模式,在一个时钟沿采样两次,比如CLK-10Mhz,现在就是20Mhz了。其实这种做法在flash,内存里面很常见。

在标准SPI中,MISO数据只在SCLK的上升沿或下降沿被采样一次。

DDR SPI为了提高数据传输速率,在SCLK的一个周期内,MISO数据会在上升沿和下降沿各被采样一次。

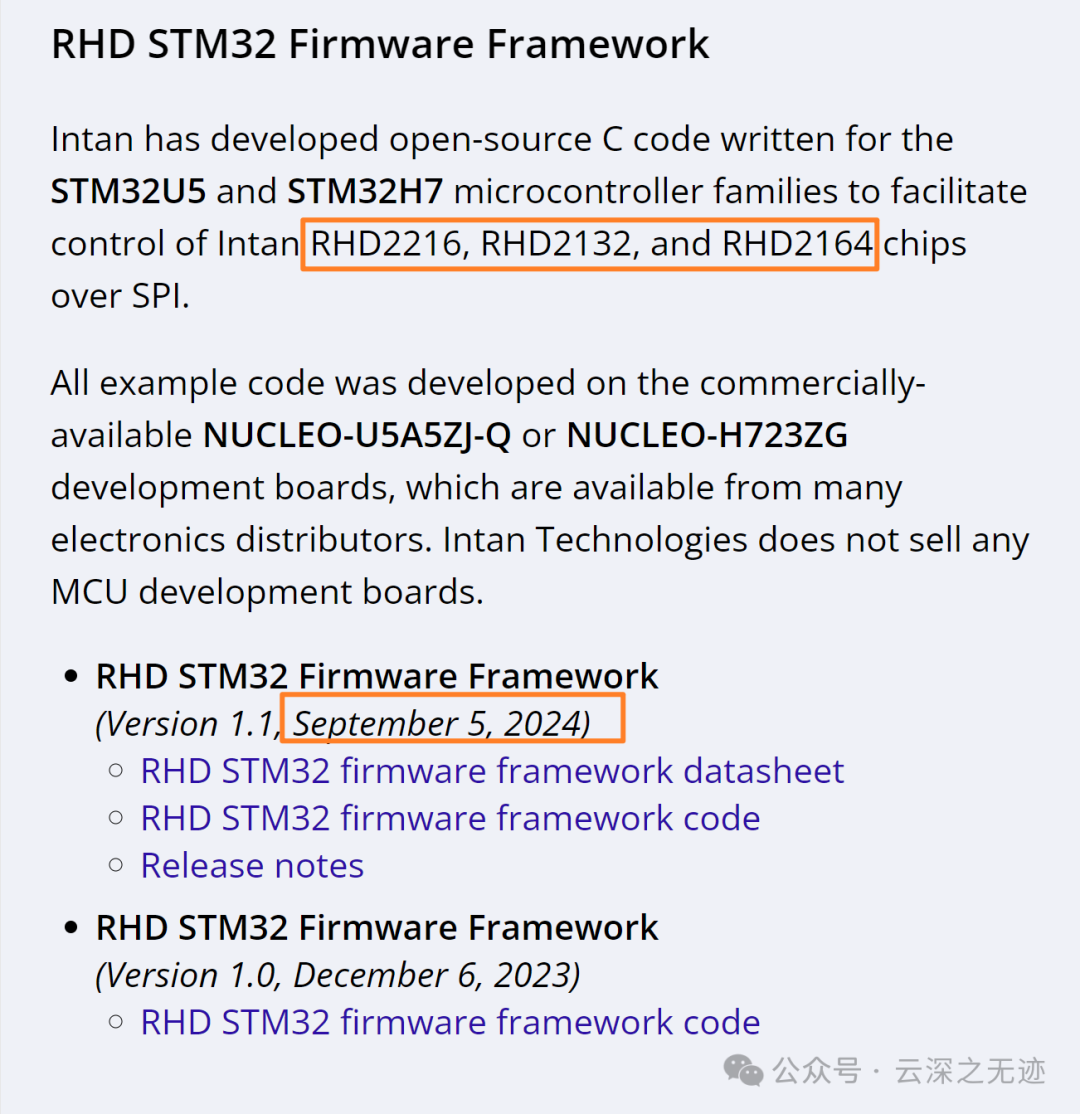

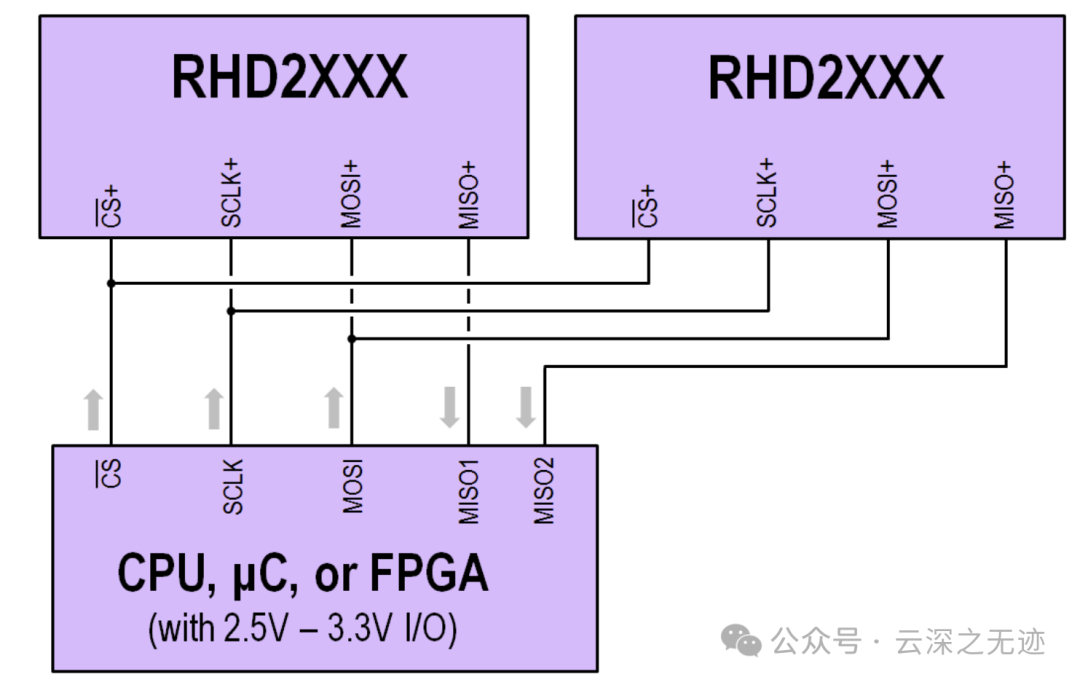

连接示意图,但是MCU来连接不太好,就是不灵活

我前几个看64的还没有MCU版本,现在全系列芯片都可以使用MCU控制了。

OK,一会儿看

对于一个标准的协议来说,就是CLK一个Edge才采样一次

SPI协议详解以ADS1118为例 可以看这个学习一下。

DDR就是上下都会采样

下面这段内容,全网都没有,你能看到就有福气了。

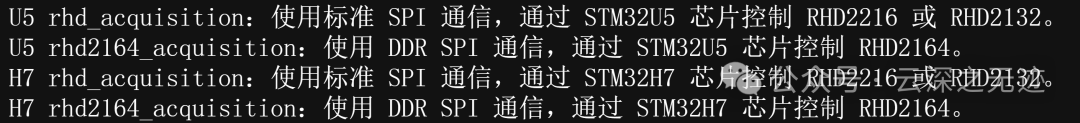

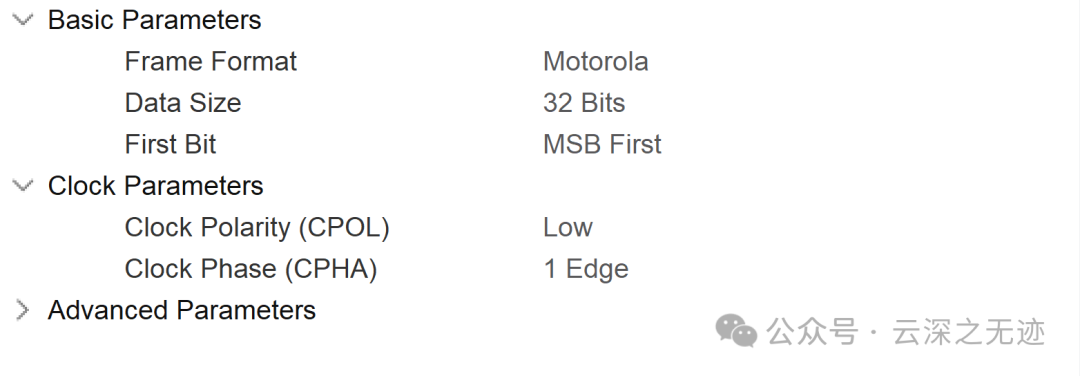

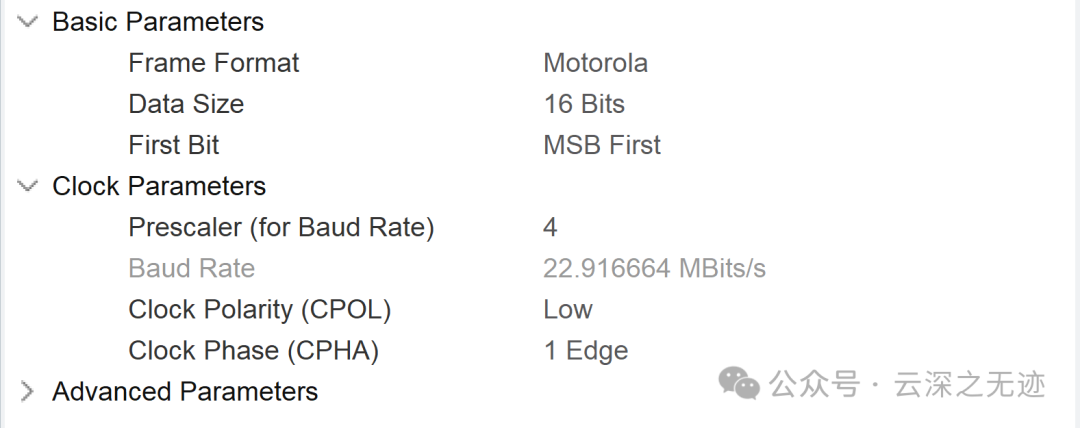

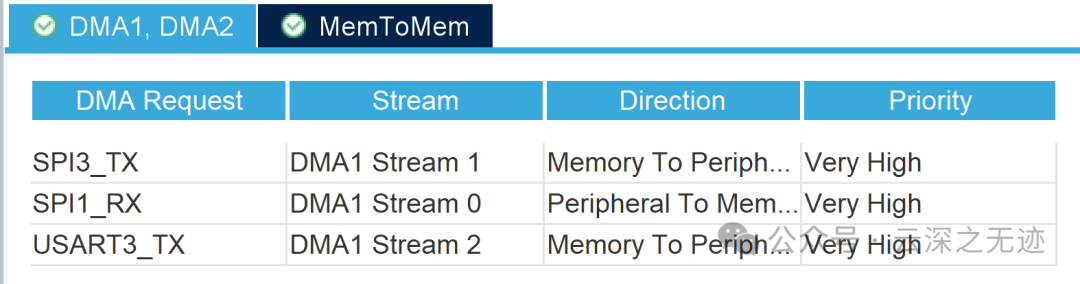

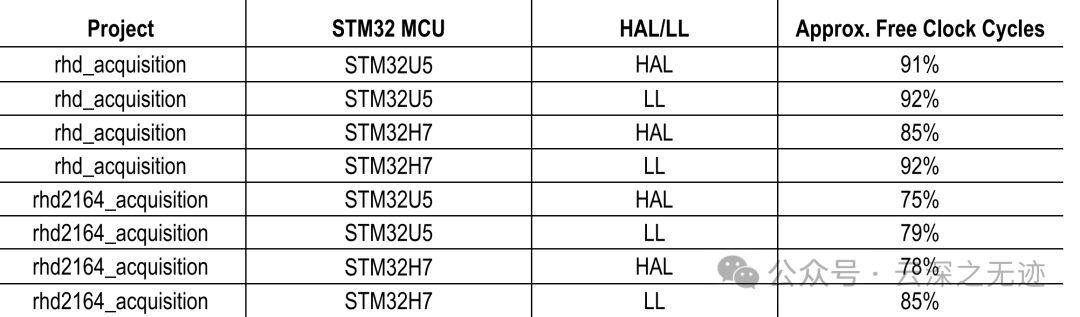

在使用单片机(如STM32 U5或H7)实现DDR(Double Data Rate,双倍数据速率)SPI通信时,由于标准SPI外设不支持32位MISO接收,而需要采用两个SPI外设来实现这一功能的配置方法。

问题: 标准SPI外设通常不支持MOSI传输16位数据,MISO接收32位数据的模式。

解决方案:

两个SPI外设: 分别用一个SPI外设负责16位MOSI数据的发送(TRANSMIT_SPI),另一个SPI外设负责32位MISO数据的接收(RECEIVE_SPI)。

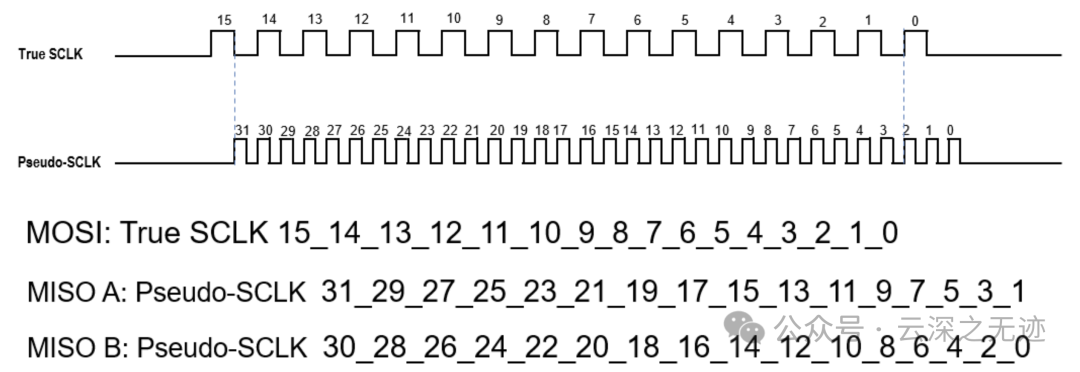

伪SCLK信号: 由于RECEIVE_SPI需要在SCLK的上升沿和下降沿都对MISO进行采样,因此需要生成一个频率是SCLK两倍的伪SCLK信号。

时序同步: 伪SCLK的产生需要与真实的SCLK进行同步,确保MISO数据的采样时刻正确。

SPI1

SPI3

配置TRANSMIT_SPI:

作为主设备,负责输出CS、SCLK和MOSI信号。

只发送16位数据。

配置RECEIVE_SPI:

作为从设备,只负责接收MISO信号。

接收32位数据。

使用生成的伪SCLK信号作为时钟。

生成伪SCLK信号:

利用定时器产生一个频率为SCLK两倍的信号。

调整伪SCLK的相位,使其与真实的SCLK保持同步。

利用微控制器的定时器模块,通过PWM模式和重复计数器,生成一个频率为SCLK两倍的方波信号。通过调整定时器的参数,可以精确控制伪SCLK的相位,使其与SCLK保持同步。

True SCLK: 标准的SPI时钟信号。

Pseudo-SCLK: 由定时器生成的伪时钟信号,频率是True SCLK的两倍。

MOSI: 主机发送的数据,以True SCLK为时钟。

MISO A, MISO B: 从机接收的数据,分别在Pseudo-SCLK的奇数和偶数上升沿采样。

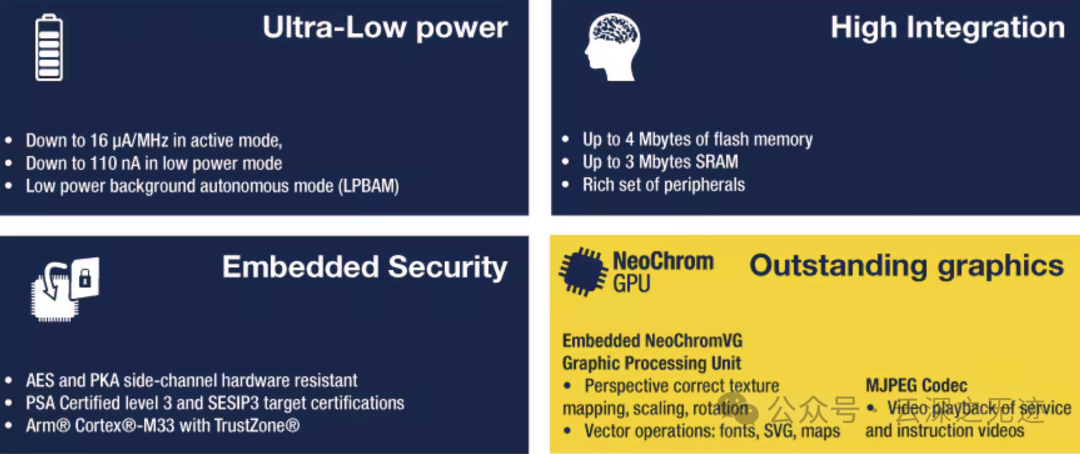

U5强哇

U5:

定时器配置恰好满足时序要求,无需额外调整。

H7:

运行速度更快,需要引入额外的延迟,以确保伪SCLK与True SCLK的相位关系正确。

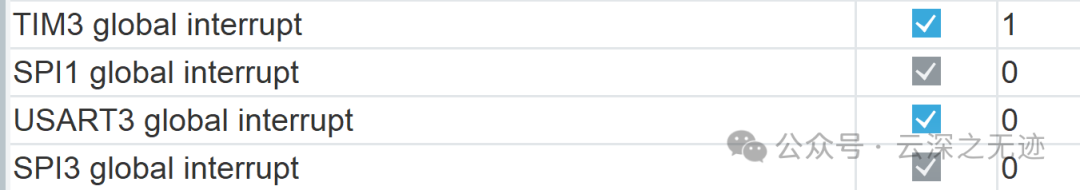

为了速度,DMA全开

依靠中断进行通讯

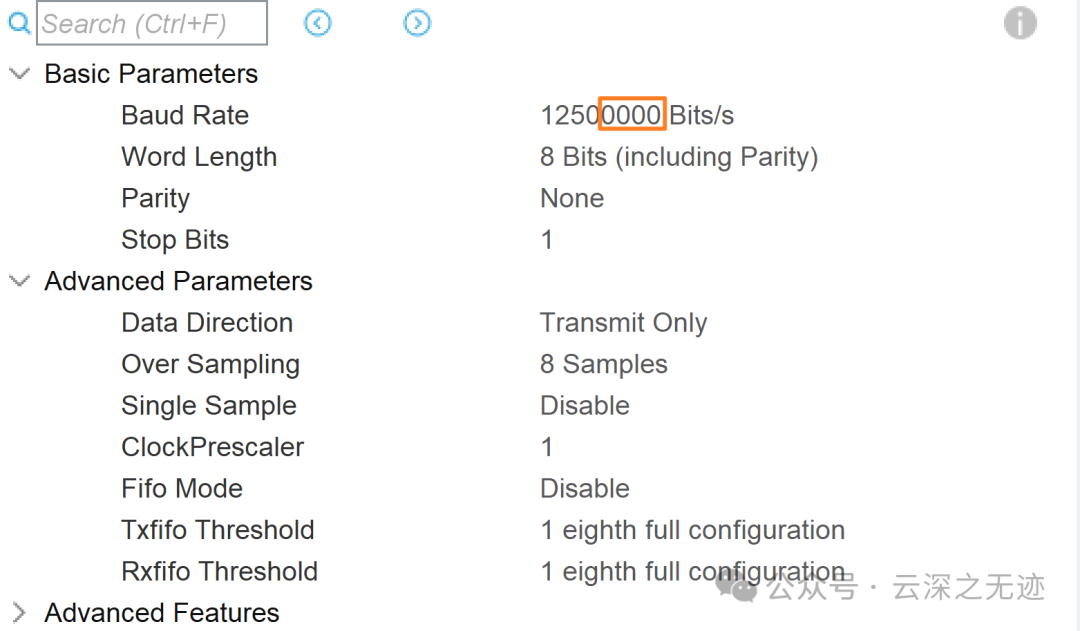

牛的,波特率这么高

剩下的细节就不写了。

不过LL确实很快

级联的就算了,FPGA来了

LVDS的连接是这样的

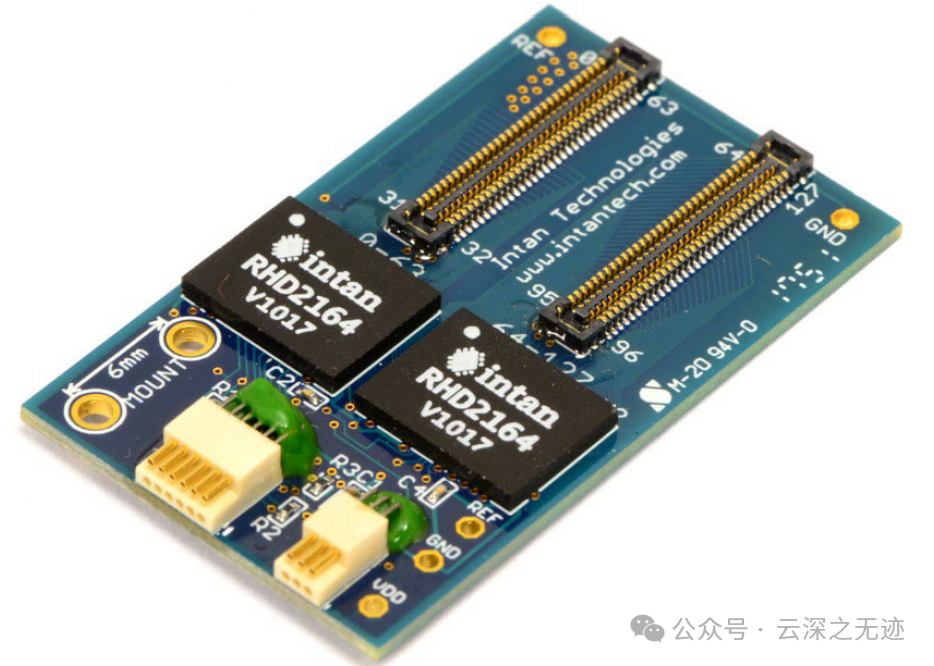

一种板子是这样的,上面的金点都镀金了

双芯片,128位通道

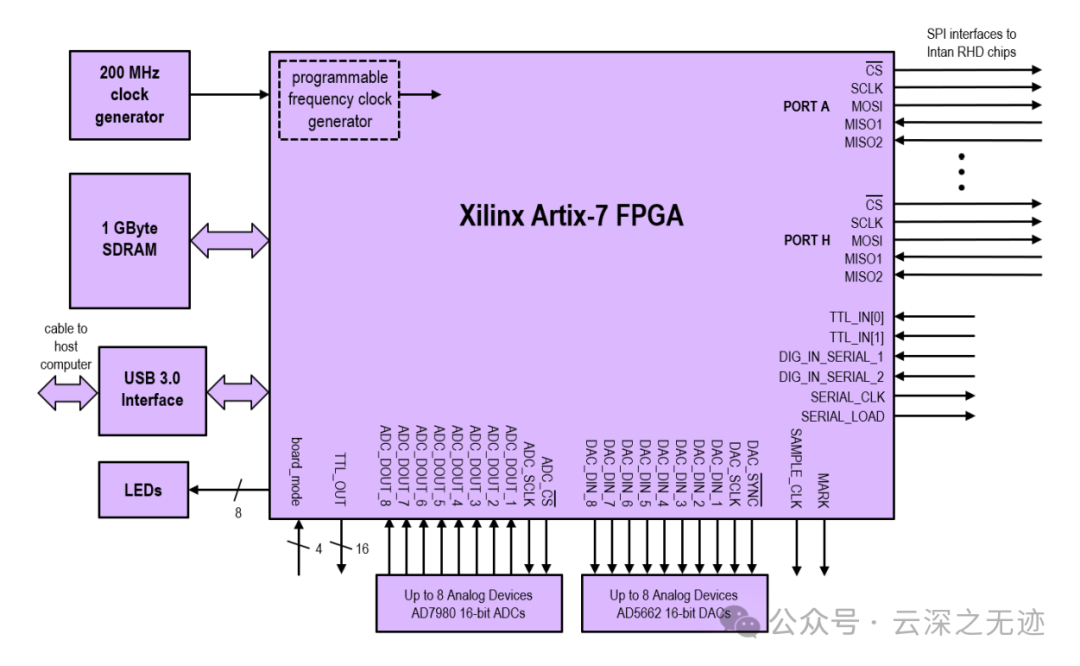

FPGA的框图,等我学会FPGA再看

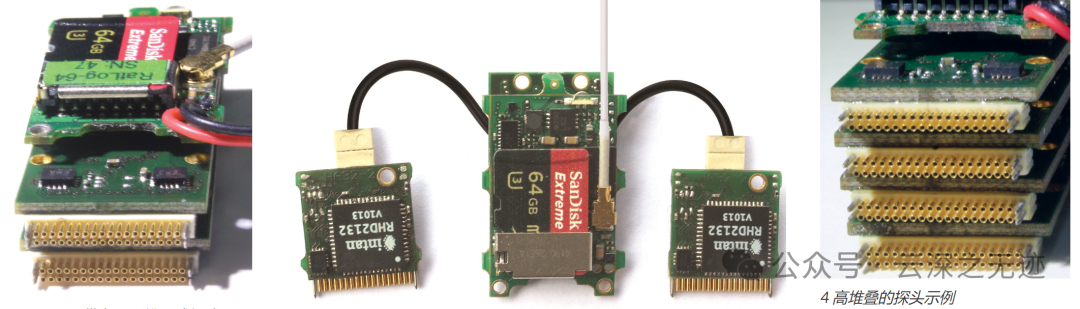

当然了一些厂家也设计了很多有趣的设计,我感觉我也可以设计。

总之很棒,但是脑机接口也路途遥远。

https://intantech.com/signals_RHD2000.html