存储器子系统的主要功能是在云计算和人工智能 (AI)、汽车和移动等广泛应用中尽可能快速可靠地为主机(CPU 或 GPU)提供必要的数据或指令。片上系统 (SoC) 设计人员可以选择多种类型的存储器技术,每种技术都具有不同的特性和高级功能。双数据速率 (DDR) 同步动态随机存取存储器 (SDRAM) 已成为主系统存储器最主流的存储器技术,因为它使用电容器作为存储元件来实现高密度和简单架构、低延迟和高性能、无限存取耐力和低功耗。

选择正确的存储器技术通常是实现最佳系统性能的最关键决策。本文介绍了不同的存储器技术,旨在帮助 SoC 设计人员选择最适合其应用要求的正确存储器解决方案。

下载链接:

《2024年中国AI Agent研究合集》

1、2024年中国AI Agent研究:创新驱动,智能技术革新

2、中国AI Agent行业研究:智能体落地千行百业,引领智能化革命的新引擎

AI Agent在解决大模型应用难题中的关键作用

AI Agent行业词条报告:驱动智能交互变革,重塑服务生态

AI Agent在企业生产中的技术实践

《AI Agent技术应用合集》

1、面向办公自动化领域的 AI Agent 建设思考与分享

2、AI Agent 在企业经营分析场景的落地

3、LLM和Multi-Agent在运维领域的实验探索

700+份重磅ChatGPT专业报告

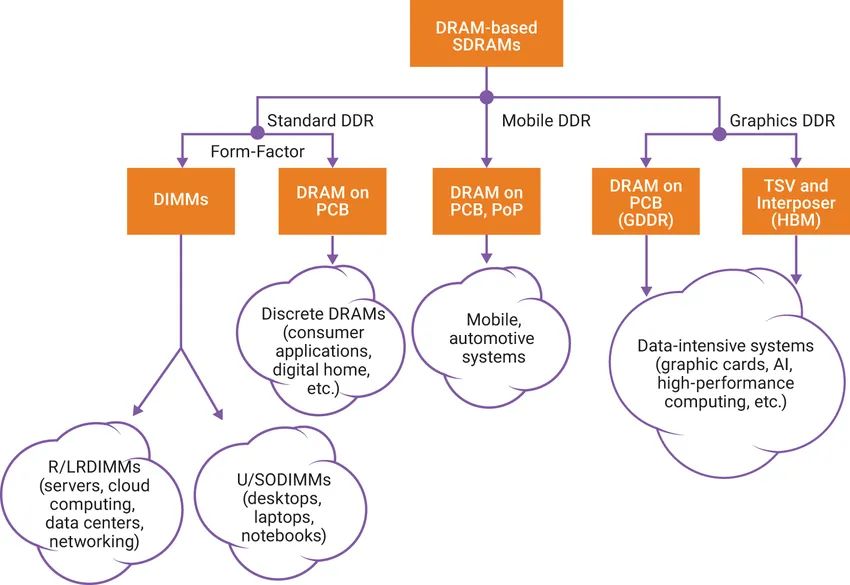

设计人员不断为他们的 SoC 添加更多内核和功能;然而在保持低功耗和较小硅尺寸的同时提高性能仍然是一个至关重要的目标。DDR SDRAM(简称 DRAM)通过在双列直插式存储模块 (DIMM) 或分立式 DRAM 解决方案中提供密集、高性能和低功耗的存储器解决方案,以满足此类存储器要求。JEDEC 定义并开发了以下三种 DRAM 标准类别,帮助设计人员满足目标应用的功耗、性能和规格要求:

上述三种 DRAM 类别使用相同的 DRAM 阵列进行存储,以电容器作为基本存储元件。但是,每个类别都提供独特的架构功能,旨在最好地满足目标应用程序的要求。这些功能包括数据速率和数据宽度自定义、主机和 DRAM 之间的连接选项、电气规格、I/O(输入/输出)端接方案、DRAM 电源状态、可靠性特性等。图 1 展示了 JEDEC 的三类 DRAM 标准。

标准 DDR DRAM 在企业服务器、数据中心、笔记本电脑、台式机和消费类应用等应用领域随处可见,可提供高密度和高性能。DDR4 是这一类别中最常用的标准,与其前代产品 DDR3 和 DDR3L(DDR3 的低功耗版本)相比具有多项性能优势:

正在 JEDEC 开发的 DDR5 预计将在 1.1V 的工作电压下将运行数据速率提高到 4800Mbps。DDR5 新增多种架构和 RAS 特性,可有效处理这些高速运行,同时尽量缩短因存储器错误导致的系统停机时间。模块上的集成稳压器、更好的刷新方案、旨在提高通道利用率的架构、DRAM 上的内部纠错码 (ECC)、用于提高性能的更多存储体组以及更高的容量只是 DDR5 的一小部分关键特性。

与标准 DDR DRAM 相比,移动 DDR(也称为低功耗 DDR (LPDDR) DRAM)具有一些可以降低功耗的附加功能,而降低功耗正是移动/电池供电应用(如平板电脑、移动电话和汽车系统,以及 SSD 卡)的核心要求。LPDDR DRAM 可以比标准 DRAM 运行得更快,以实现高性能并提供低功耗状态,帮助提高电源效率和延长电池寿命。

与标准 DDR DRAM 通道(64 位宽)相比,LPDDR DRAM 通道通常为 16 位或 32 位宽。与标准 DRAM 产品一样,每个连续的 LPDDR 标准产品都瞄准了比其前代产品更高的性能和更低的功耗目标,并且任何两个 LPDDR 产品都不会彼此兼容。

LPDDR4 是这个类别中最常用的标准,在 1.1V 的工作电压下的数据速率最高可达 4267Mbps。LPDDR4 DRAM 通常是双通道设备,支持两个 x16(16 位宽)通道。各个通道都是独立的,因此具有自己的专用命令/地址 (C/A) 引脚。双通道架构为系统架构人员提供了灵活性,同时将 SoC 主机连接到 LPDDR4 DRAM。

LPDDR4X 是 LPDDR4 的一种变体,与 LPDDR4 完全相同,只是能够通过将 I/O 电压 (VDDQ) 从 1.1 V 降低到 0.6 V 来额外降低功耗。LPDD4X 设备也可以实现高达 4267Mbps 的速率。

LPDDR5 是 LPDDR4/4X 的后续产品,预计运行速率高达 6400Mbps,并且正在 JEDEC 进行积极开发。LPDDR5 DRAM 有望提供许多新的低功耗和可靠性特性,使其成为移动和汽车应用的理想选择。其中一种重要特性就是用于延长电池寿命的“深度睡眠模式”,有望显著节省空闲条件下的功耗。此外,还有一些新的架构特性使 LPDDR5 DRAM 能够以低于 LPDDR4/4X 的工作电压在此类高速条件下无缝运行。

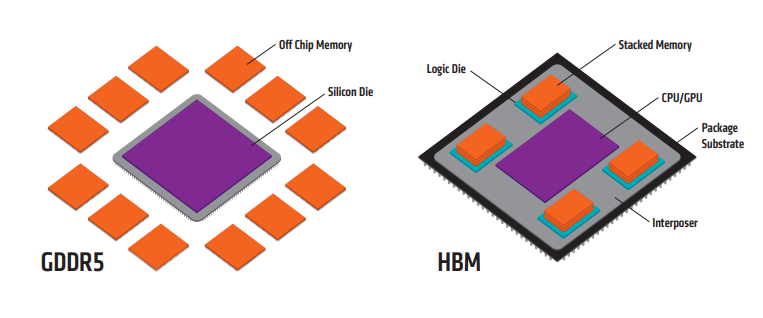

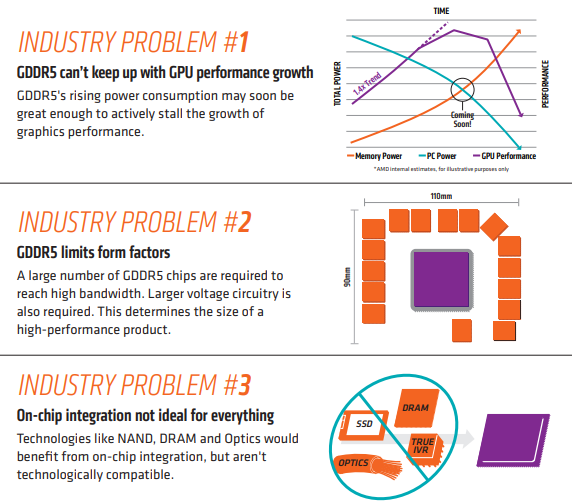

针对高吞吐量应用(例如显卡和 AI)的两种不同的存储器架构是 GDDR 和 HBM。

GDDR DRAM 是专为图形处理器 (GPU) 和加速器设计的。数据密集型系统(如显卡、游戏控制台和高性能计算,包括汽车、AI 和深度学习)是 GDDR DRAM 设备常用的一些应用。GDDR 标准 (GDDR6/5/5X) 被架设为点对点 (P2P) 标准,能够支持高达 16Gbps 的速率。GDDR5 DRAM 一直用作离散的 DRAM 解决方案,能够支持高达 8Gbps 的速率,经过配置后可在设备初始化期间检测到的 ×32 模式或 ×16(折叠)模式下运行。

GDDR5X 的目标是每个引脚的传输速率为 10 到 14Gbps,几乎是 GDDR5 的两倍。GDDR5X 和 GDDR5 DRAM 的主要区别在于 GDDR5X DRAM 拥有的预加载为 16N,而不是 8N。与 GDDR5 每个芯片使用 170 个引脚相比,GDDR5X 每个芯片使用 190 个引脚。因此,GDDR5 和 GDDR5X 标准需要不同的 PCB。GDDR6 是最新的 GDDR 标准,支持在 1.35V 的较低工作电压下运行高达 16Gbps 的更高数据速率,而 GDDR5 需要 1.5V 才能达到该速率。

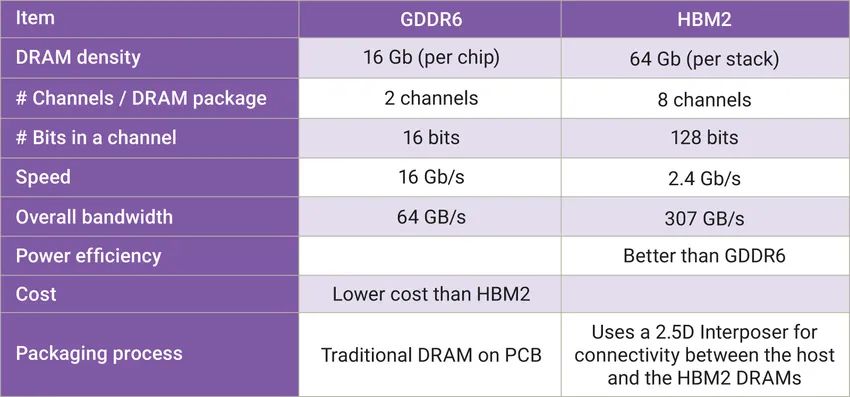

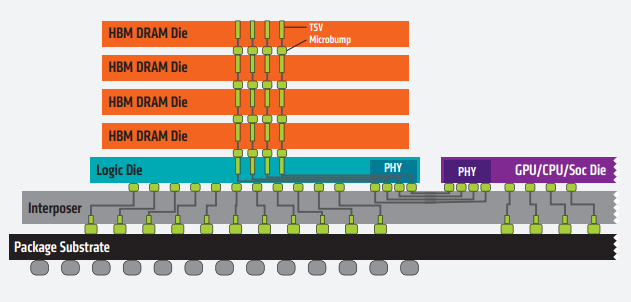

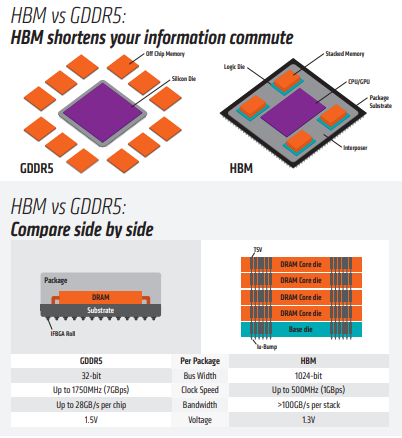

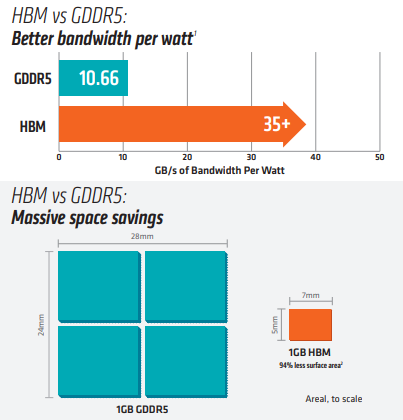

HBM 是 GDDR 存储器的替代品,可用于 GPU 和加速器。GDDR 存储器旨在以较窄的通道提供更高的数据速率,进而实现必要的吞吐量,而 HBM 存储器通过 8 条独立通道解决这一问题,其中每条通道都使用更宽的数据路径(每通道 128 位),并以 2Gbps 左右的较低速度运行。因此,HBM 存储器能够以更低的功耗提供高吞吐量,而规格上比 GDDR 存储器更小。HBM2 是目前该类别中最常用的标准,支持高达 2.4Gbps 的数据速率。

HBM2 DRAM 最多可叠加 8 个 DRAM 晶圆(包括一个可选的底层晶圆),可提供较小的硅片尺寸。晶圆通过 TSV 和微凸块相互连接。通常可用的密度包括每个 HBM2 封装 4 或 8GB。

除了支持更多的通道外,HBM2 还提供了一些架构更改,以提高性能并减少总线拥塞。例如,HBM2 具有“伪通道”模式,该模式将每个 128 位通道分成两个 64 位的半独立子通道。它们共享通道的行和列命令总线,却单独执行命令。增加通道数量可以通过避免限制性时序参数(例如 tFAW)以在每单位时间激活更多存储体,从而增加整体有效带宽。标准中支持的其他功能包括可选的 ECC 支持,可为每 128 位数据启用 16 个错误检测位。

预计 HBM3 将在几年内上市,并提供更高的密度、更大的带宽 (512GB/s)、更低的电压和更低的成本。表 1 显示了 GDDR6 和 HBM2 DRAM 的高级别比较结果:

NAND、DRAM和Optics等技术将受益于片上集成技术,而且在技术上并不兼容。HBM是一种低功耗、超宽带通信通道的新型存储芯片。它使用垂直堆叠的存储芯片,通过被称为“硅透”(TSV)的线相互连接,HBM突破了现有的性能限制。

此外,HBM相比GDDR5,减少了通信成本,单位带宽能耗更低,制作工艺更高,所以极大减少晶元空间。

2024中国物联网安全行业概览:解除网络威胁,物联网的智能守护

《2024 ODCC ETH-X超节点技术合集》

1、2024 ODCC ETH-X超节点AI 整机柜设计规范 2、2024 ODCC ETH-X互联报告 3、2024 ODCC ETH-X计算节点参考设计 4、2024 ODCC ETH-X交换节点硬件规范

2024 ODCC 面向AI东西向流量的高性能以太网络测试

2024 ODCC 通用算力交付验收技术规范

2024 ODCC AI数据中心网络建网参考报告

2024 ODCC PUE与WUE双优型数据中心构建方法技术报告

《2024 ODCC Raid Card技术报告合集》

1、2024 ODCC Raid Card性能测试技术报告 2、2024 ODCC NVMe SSD Raid 性能测试技术报告

2024 ODCC 边缘计算AI推理技术场景与挑战

2024 ODCC 基于DPU的高性能存储网络技术报告

2024 ODCC OTII-E模块化服务器技术规范

2024 ODCC S3IP-风扇及电源模组设计规范

《HotChips 2024大会技术合集(1)》

《HotChips 2024大会技术合集(2)》

《HotChips 2024大会技术合集(3)》

《HotChips 2024大会技术合集(4)》

《HotChips 2024大会技术合集(5)》

《HotChips 2024大会技术合集(6)》

《HotChips 2024大会技术合集(7)》

《HotChips 2024大会技术合集(8)》

机器人专题研究:产业发展概览(2024)

《算力网络:光网络技术合集(1)》

1、面向算力网络的新型全光网技术发展及关键器件探讨

2、面向算力网络的光网络智能化架构与技术白皮书

3、2023开放光网络系统验证测试规范

4、面向通感算一体化光网络的光纤传感技术白皮书

《算力网络:光网络技术合集(2)》

1、数据中心互联开放光传输系统设计

2、确定性光传输支撑广域长距算力互联

3、面向时隙光交换网络的纳秒级时间同步技术

4、数据中心光互联模块发展趋势及新技术研究

面向超万卡集群的新型智算技术白皮书

面向AI大模型的智算中心网络演进白皮书

《半导体行业系列专题合集》

1、半导体行业系列专题:刻蚀—半导体制造核心设备,国产化典范

2、半导体行业系列专题:碳化硅—衬底产能持续扩充,加速国产化机会 3、半导体行业系列专题:直写光刻篇,行业技术升级加速应用渗透 4、半导体行业系列专题:先进封装—先进封装大有可为,上下游产业链受益

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。