台积电HBM4内存的推出将带来多项重大变革,其中最引人注目的就是其内存接口的大幅扩展。第四代内存技术接口从1024位扩展到2048位,这标志着HBM4内存的设计和生产将面临新的挑战,为了适应这一变化,芯片制造商必须采用更新、更高级的封装技术。

在2024年的欧洲技术研讨会上,台积电透露了其为HBM4制造的base die一些细节,这些芯片将采用逻辑工艺制造,台积电计划利用其N12和N5工艺的改进版本来生产这些芯片。这将使台积电在HBM4的生产领域占据优势,因为现有的内存制造设施均无法做到经济高效地生产这种先进逻辑芯片。

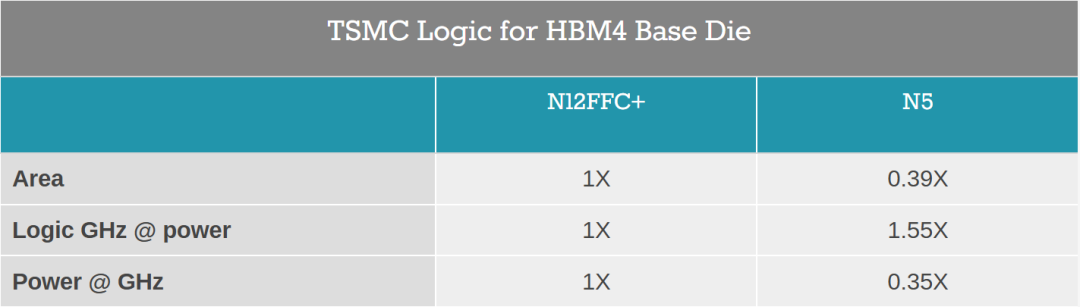

对于HBM4的首批产品封装,台积电将采用N12FFC+和N5两种不同的制造工艺。尽管这两种工艺都是为了将HBM4E内存与新一代的AI和高性能计算处理器相结合,但它们在连接AI和高性能计算应用的高性能处理器的内存方面发挥着不同的作用。

台积电的设计和技术平台高级总监透露:“公司正与美光、三星和SK海力士等主要HBM内存供应商合作,利用先进的工艺节点推进HBM4内存技术的全面整合。N12FFC+工艺的基础芯片在成本效益上具有优势,能够满足HBM的性能需求,而N5工艺的基础芯片则能在保持HBM4速度的同时,提供更复杂的逻辑功能并大幅降低能耗。

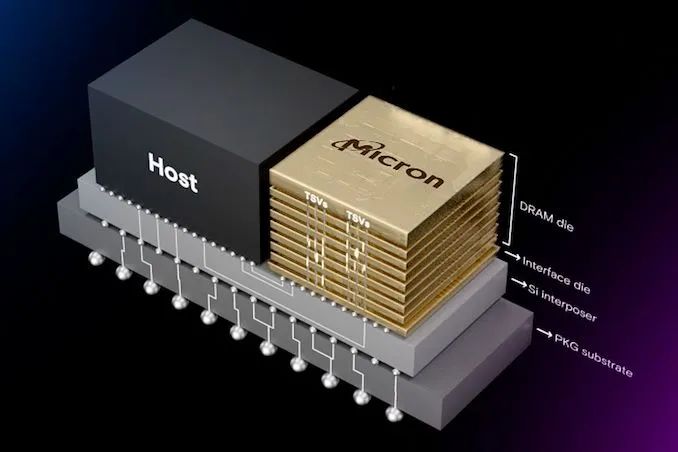

台积电的N12FFC+工艺(12纳米FinFET Compact Plus,虽然归类于12纳米技术,但技术基础源自其成熟的16纳米FinFET生产线)生产的基础芯片,将用于在系统级芯片(SoCs)旁的硅中介层上安装HBM4内存堆栈。台积电相信,其12FFC+工艺非常适合实现HBM4的性能,使内存制造商能够构建12-Hi(48GB)和16-Hi(64GB)堆栈,每个堆栈的带宽超过2TB/秒。

台积电高级总监提到:“我们也在为HBM4优化CoWoS-L和CoWoS-R技术,CoWoS-L和CoWoS-R技术都采用超过八层的布线设计以确保HBM4超过2000个的互连和信号完整性。”

使用N12FFC+工艺的HBM4基础芯片对于采用台积电CoWoS-L或CoWoS-R先进封装技术构建系统级封装(SiPs)至关重要,这些技术提供的中介层面积可达8倍光罩尺寸,足以容纳多达12个HBM4内存堆栈。据报道,HBM4能够以 14mA的电流实现6GT/s的数据传输速率。

台积电还与Cadence、Synopsys和Ansys等EDA公司合作,确保HBM4通道的信号完整性、IR/EM和热准确性。

与此同时,内存制造商还可以选择使用台积电的N5工艺来生产HBM4 base die。N5工艺制造的基础芯片将集成更多逻辑功能,减少功耗并提供更高的性能。最重要的是,这种先进的工艺技术将实现非常小的互连间距,约为6到9微米,这将使N5基础芯片能够与直接键合技术结合使用,允许HBM4直接3D堆叠在逻辑芯片上从而大幅提升内存性能,这将为不断追求更高内存带宽的AI和HPC芯片带来巨大的提升。

据悉,台积电与SK海力士在HBM4 base die上已有合作,并且台积电也可能为美光生产HBM4 base die。至于三星拥有自己的先进逻辑生产线,台积电与其合作的可能性相对较小。

原文链接:https://www.anandtech.com/show/21395/tsmc-readies-hbm4-base-dies-at-12nm-and-5nm

高端微信群介绍 | |

创业投资群 | AI、IOT、芯片创始人、投资人、分析师、券商 |

闪存群 | 覆盖5000多位全球华人闪存、存储芯片精英 |

云计算群 | 全闪存、软件定义存储SDS、超融合等公有云和私有云讨论 |

AI芯片群 | 讨论AI芯片和GPU、FPGA、CPU异构计算 |

5G群 | 物联网、5G芯片讨论 |

第三代半导体群 | 氮化镓、碳化硅等化合物半导体讨论 |

存储芯片群 | DRAM、NAND、3D XPoint等各类存储介质和主控讨论 |

汽车电子群 | MCU、电源、传感器等汽车电子讨论 |

光电器件群 | 光通信、激光器、ToF、AR、VCSEL等光电器件讨论 |

渠道群 | 存储和芯片产品报价、行情、渠道、供应链 |

< 长按识别二维码添加好友 >

加入上述群聊

带你走进万物存储、万物智能、

万物互联信息革命新时代