一、 概述

数字上下变频是雷达系统中两个重要的模块。在雷达发送端,由于天线的长度有限会影响到电磁波的波长,而波长与信号的频率成反比,故在发送端需要使用数字上变频提高信号的频率;而在雷达的接收端若不进行下变频处理,根据奈奎斯特采样定理,需要使用信号频率2倍的采样率才能准确无误的将信号还原出来,对AD采样速率以及后续FPGA处理信号的速率要求非常高,不利于系统设计,故在接收机端先将射频信号下变频到中频信号,再将中频信号下变频到零中频信号,方便后续对信号的处理。

本次设计同样是通过在simulink搭建模型并通过matlab仿真得到正确设计后生成IP核的形式来实现数字下变频的功能。

二、 原理

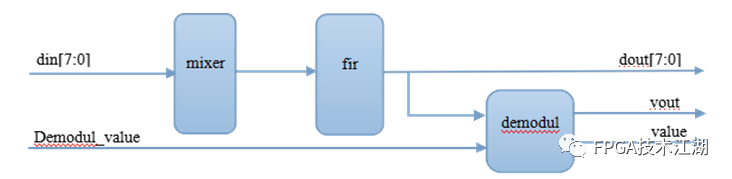

数字下变频的基本原理如下图所示:

数字下变频主要包括下混频和滤波抽取两部分,下面分别介绍:

1、 下混频:

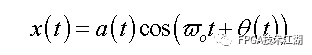

现实中,信号是一个实的窄带信号,可表示为,如下表达式:

经AD采样后,变成数字信号:

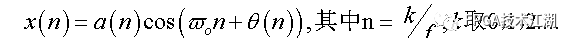

通过混频技术,可得到信号的正交变量,数字信号正交混频可表示为:

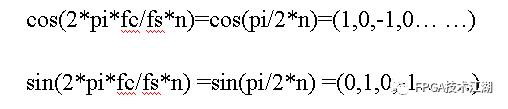

频率变换是一种常用的数字信号处理算法,对于1/4信号采样率频率变化,有一种简单的实现方法,下面结合实例进行介绍:

首先,原始信号进入FPGA后,得到4路数据,分别用d0,d1,d2,d3表示,然后对信号进行下变频。

这里采样率fs=1.2GHz,本振频率fc=300M,满足fc=fs/4的关系,可以采用下面高效方式进行混频的实现:

所以混频可做如下简化处理:

通过下混频我们分别得到I路和Q路两路实数据,分别表示如下:

将I路和Q路分别用I0,I1,I2,I3,和Q0,Q1,Q2,Q3来表示,I路混频后得到如下序列:

I0 = d0*(1);I1 = d1*(0);I2 = d2*(-1);I3 = d3*(0)

Q路混频后得到如下序列:

Q0 = d0*(0);Q1 = d1*(-1);Q2 = d2*(0);Q3 = d3*(1)

最后我们得到了2路300M的复数据即

I0*(1),Q1*(-1),I2*(-1),Q3*(1)。

2、多相滤波

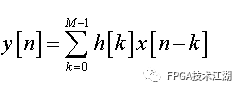

正交混频后经过低通滤波,滤除掉多余的频率,避免抽取造成的频谱混叠。这里将滤波和抽取同时进行。对于因果的FIR系统,其方程可简化为:

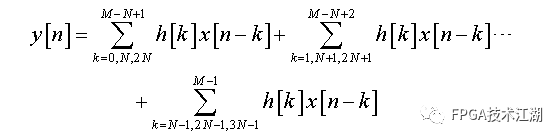

其中M为滤波器系数的长度。如果采用多路并行处理,设N为FIR滤波并行的路数,则:

其中滤波采用并行滤波结构,单路实现采用多相结构,8路并行多相滤波结构如下图所示:

三、 实现

结构框图如下图所示:

其中din为输入的8路有效数据,输出为8路的dout。

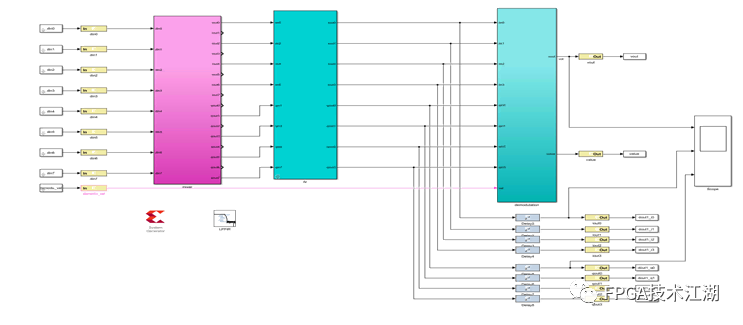

模型搭建的框图如下图

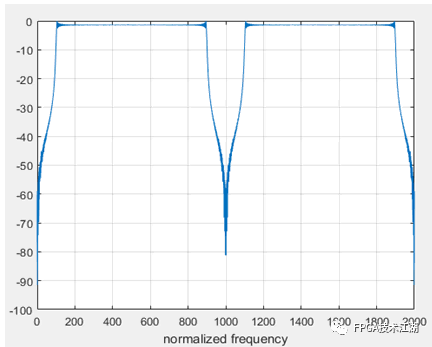

然后对模型进行仿真,我们在matlab中生成一个中心频率为500M,带宽800M的chirp信号作为模型的输入,输入信号频谱如下图:

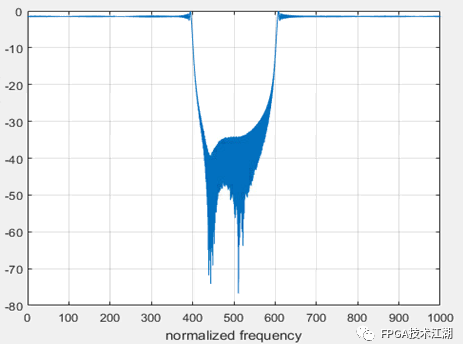

然后对输入信号进行下变频,其中采样率为2G,输入信号通过模型之后得到一个零中频信号,中心频率为0M,带宽为800M,信号频谱如下图:

- THE END -

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群