前面我们分享了文章编写代码的方式操作IO来确认IO引脚的对应关系:https://mp.weixin.qq.com/s/biR6j9wt7YxQ2GSXs-UpbQ 《基于“矿板”低成本学习FPGA》逆向扫描插座所有IO引脚映射。

该方法必须要先知道时钟引脚,而且操作效率低。 实际上我们还有更高效直接的方法,即使用Jtag边界扫描,Jtag设计的目的就是为了该类测试需求。

我们需要JTAG硬件(比如Jlink),上位机工具,BSDL文件,我们以下就详细介绍整个过程。

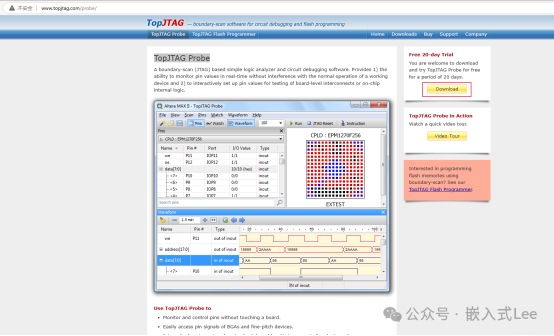

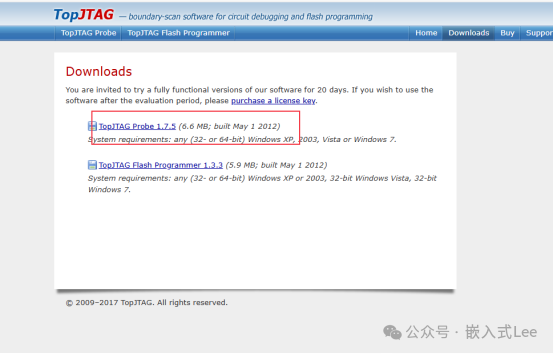

这里使用TopJTAG Probe,可以官网下载试用,如果需要可以购买。

http://www.topjtag.com/probe/

双击TopProbe-Setup-1.7.5.exe开始安装

弹出对话框点击是

Next

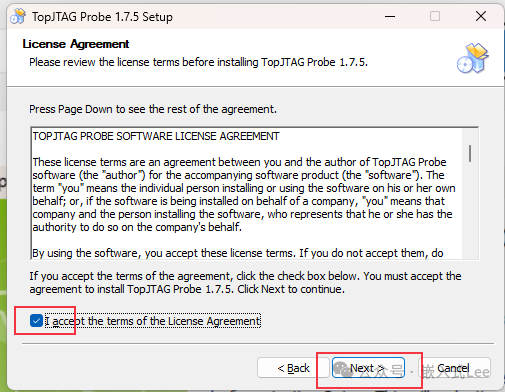

勾选,Next

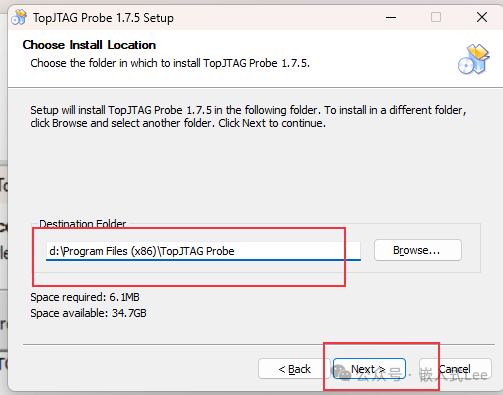

指定安装路径,Next

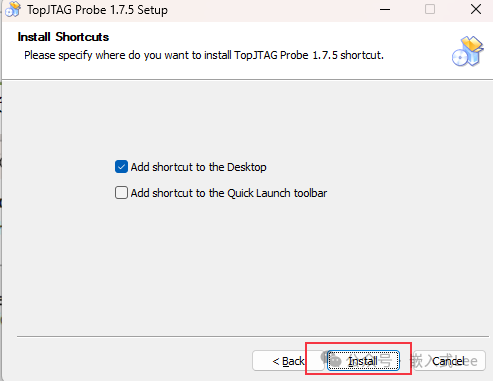

安装

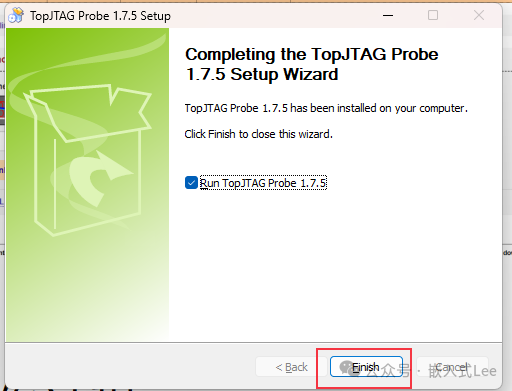

完成

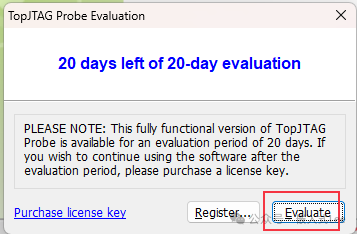

点击评估

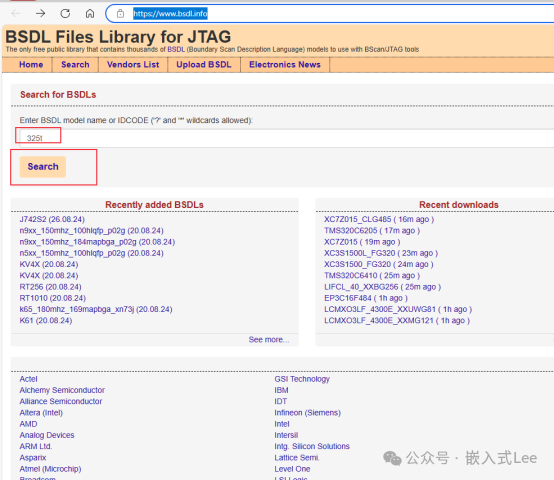

https://www.bsdl.info/

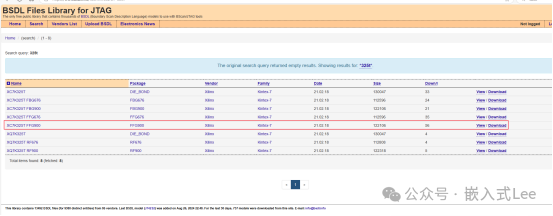

搜索325t

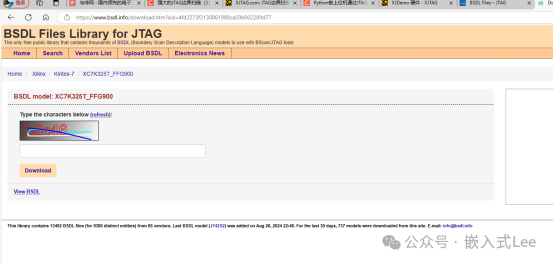

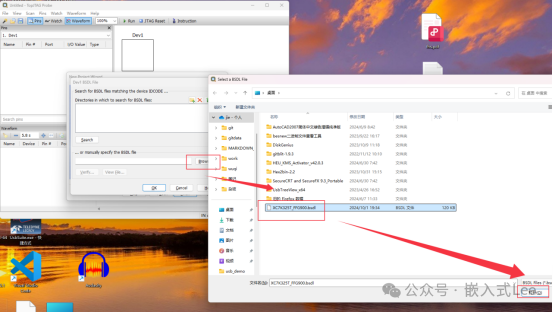

点击Download,输入验证码下载指定型号的BSDL文件

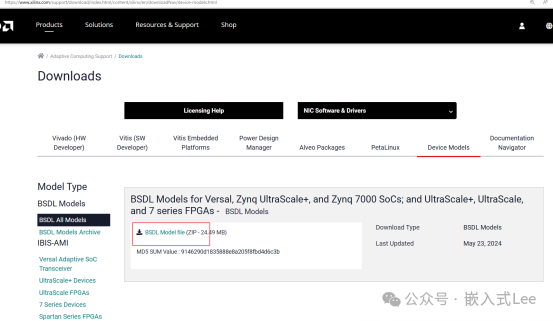

Xilinx的也可以从官网下载

https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/device-models.html

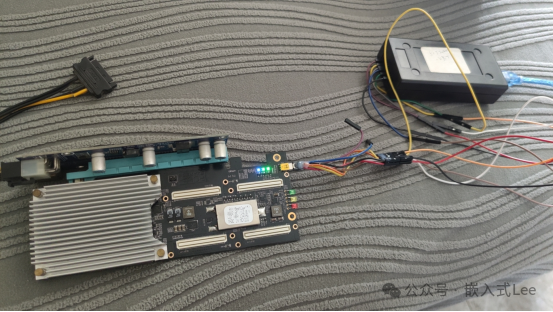

TopJTAG Probe支持不同的硬件,最常见的就是我们的Jlink仿真器,这里用的就是Jlink V9。

接线如下

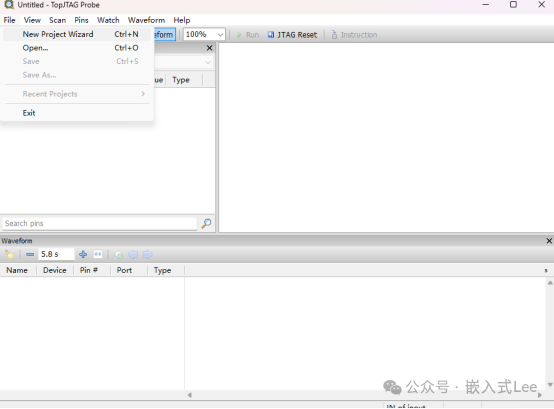

我们打开软件TopJTAG Probe

点击菜单栏

File->New Project Wizard

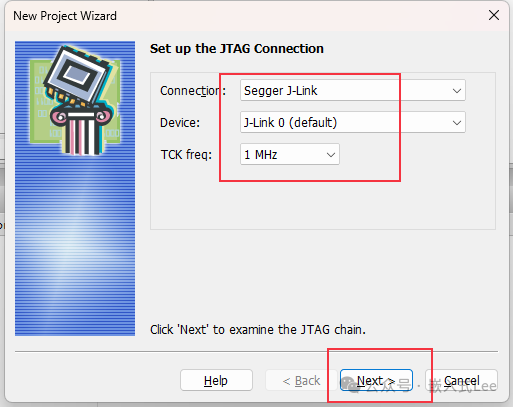

选择Jlink,Next

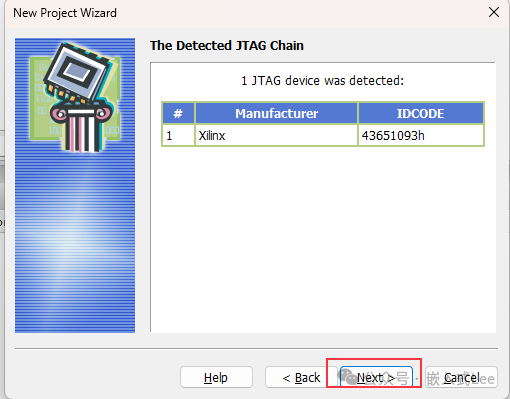

识别到芯片会显示IDCODE,继续点击Next

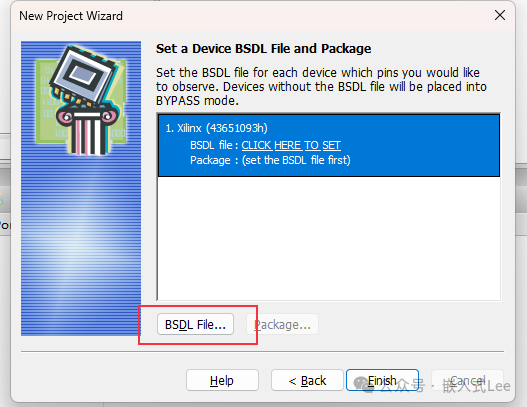

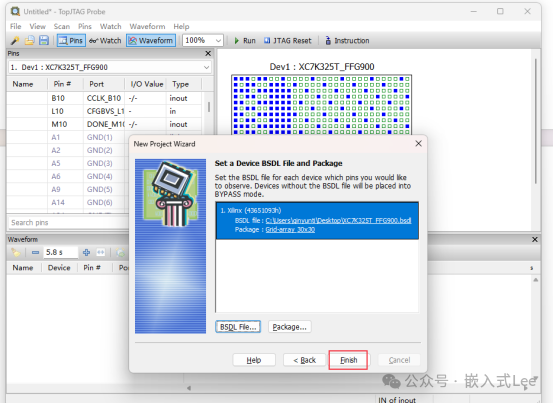

点击BSDL File...选择前面下载的BSDL文件

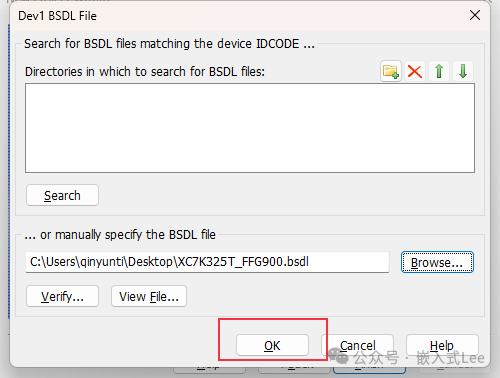

继续点击OK

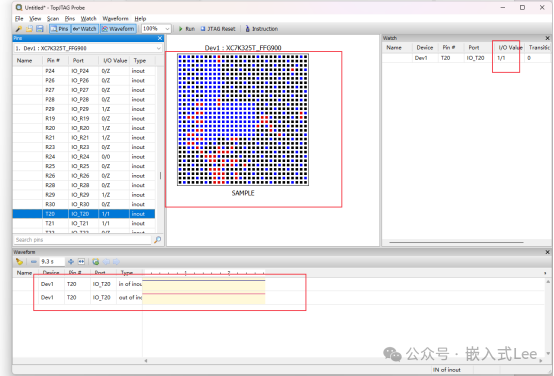

此时就会显示芯片的引脚图

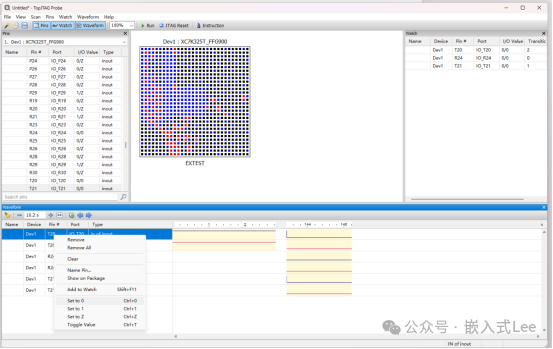

添加观测

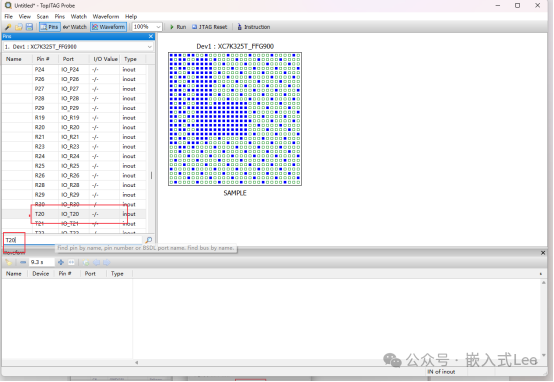

如下位置输入引脚名字回车搜索

比如这里输入T20

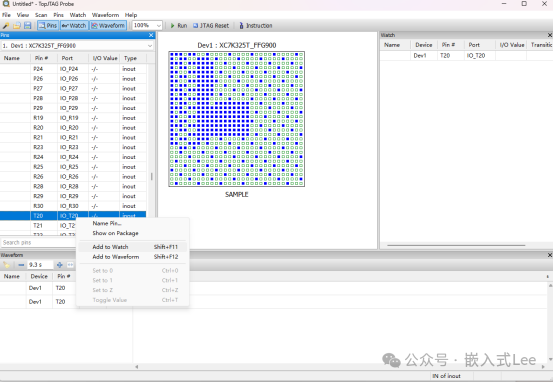

右键点击T20,添加到观测Add to Qatch和添加到波形Add to Waveform

设置采样,run

可以看到引脚状态和波形,中间的引脚图颜色代表不同状态

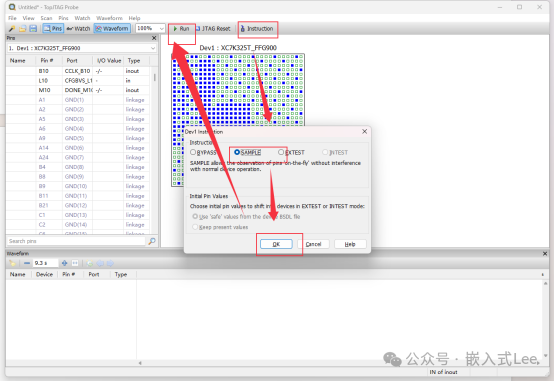

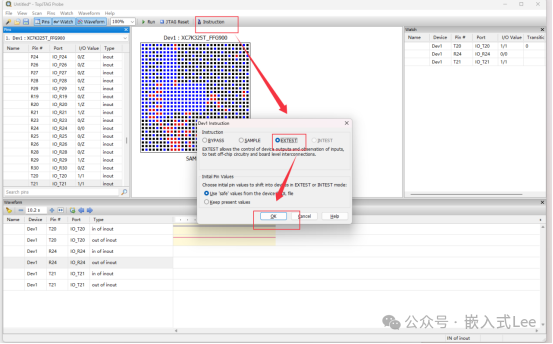

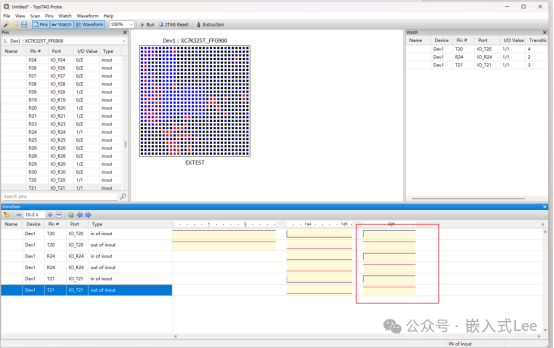

按照如下将采样模式,设置为执行模式

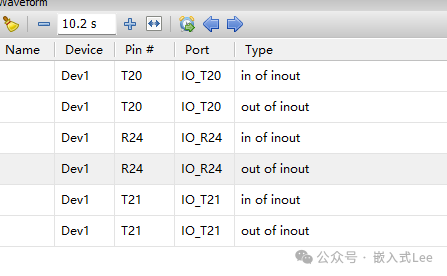

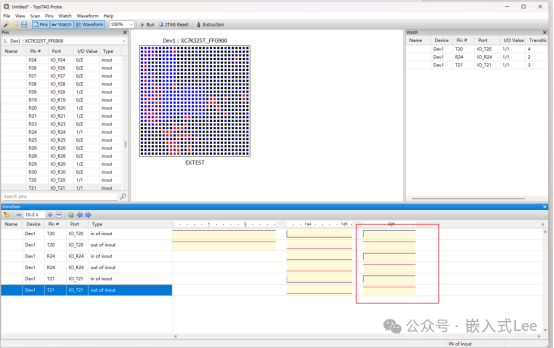

添加R24 T20 T21到观测和波形

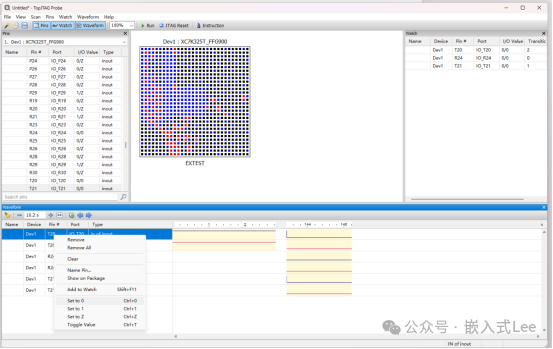

右键点击引脚名字Set to 0,将引脚设置输出0,点击Run ,可以看到波形变低

可以看到LED熄灭

再设置为set to 1

可以看到波形拉高,LED点亮

以上演示了引脚的输入输出操作,这样就可以控制任意引脚的输出,通过示波器或者逻辑分析仪查看哪个引脚对应,即可知道硬件上引脚的对应关系,完成IO引脚映射的逆向。

以上演示了如何通过JTAG进行FPAG引脚的映射关系逆向,这样淘到FPGA板子,就可以第一步确认引脚,方便后面测试设计扩展版等。

实际我们通过JTAG对任意引脚进行操作,那么连接到板子上的其他外设我们也可以进行操作了,比如直接通过控制引脚模拟SPI时序去烧写SPI FLSH(比如TopJTAG Flash Programmer工具)。我们也可以开发自己的上位机,能操作任意引脚,实际上我们就能为所欲为了, 开发烧录工具,测试工具等等,我们就可以尽情发挥开发各种有意思实用的工具了。比如嵌入式文件系统开发,一般在PC端开发测试仿真时,只能用写本地文件方式替代FLASH的操作,有了JTAG我们可以直接操作真实的SPI FLASH芯片,完全就是真实环境。