引言

原型验证是一种在FPGA平台上验证芯片设计的过程,通过在FPGA上实现芯片的设计原型,使得开发人员可以在硬件完成之前提前开始软件开发和系统验证。然而,如何快速确保在原型验证平台上开发的软件能够顺利移植到最终芯片上,并完成"bring-up"(即系统启动并正常运行),成为了开发团队面临的一个重要挑战。

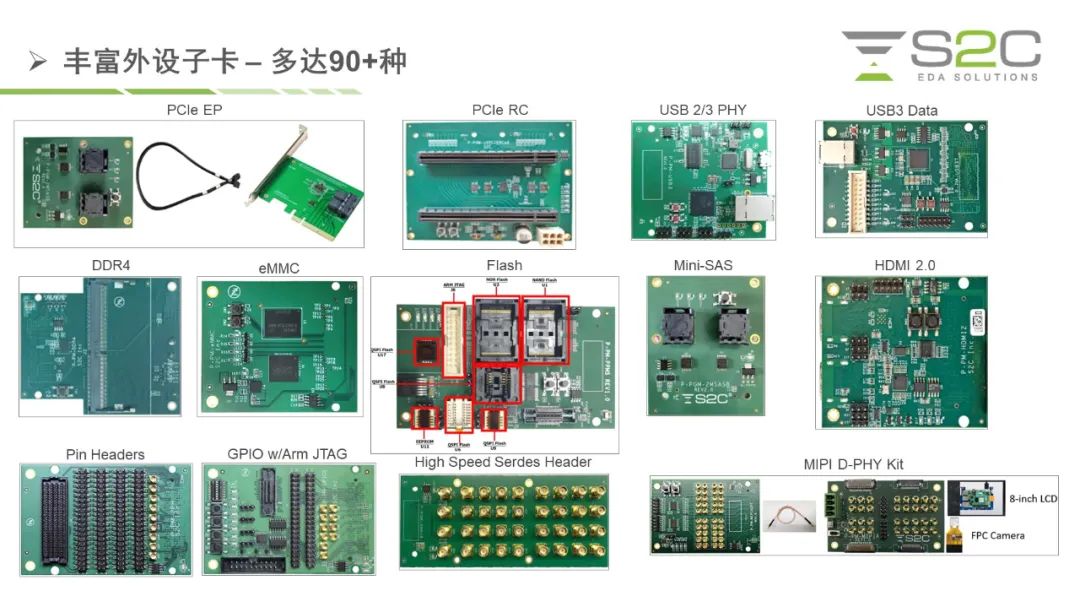

为了实现这一目标,虽然原型验证具备高性能,能够快速模拟真实芯片的运行环境,但要进一步满足客户对快速开发和验证的需求,缩短开发周期,还必须依赖于灵活的子卡(Daughter Boards)、降速桥(Speed Bridge)方案、AXI协同仿真软件以及优化的I/O分割(Partition)设计。这些工具不仅为软件开发提供了真实的数据交互环境,还显著加快了软硬件的bring-up过程。因此,在选择商用原型验证平台时,资源的多样性与灵活性成为提升验证效率的关键因素。

【预约直播】