二维半导体材料在超越硅基晶体管极限的逻辑器件缩放上具有巨大潜力。然而,目前缺少被广泛接受的比较两种技术的方式。因此,需要建立适当的标准来对比二维晶体管和硅基晶体管,为二维晶体管的未来发展提供指引。

近日,北京大学电子学院吴朋研究员、彭练矛院士应邀对建立二维晶体管与硅基晶体管基准测试标准进行评述,相关成果以题为“Setting a standard for benchmarking 2D transistors with silicon”的评论文章,于9月12日在线发表于电子学顶级期刊《Nature Reviews Electrical Engineering》。北京大学电子学院吴朋研究员为第一作者,电子学院毕业生、麻省理工学院博士后姜建峰博士为第二作者,彭练矛院士为通讯作者。

文章提出,随着二维晶体管的发展和成熟,其与商用硅基器件的直接比较是走向产业化的先决条件。逻辑器件基准测试的主要标准为性能(Performance),功耗(Power)和面积(Area),应在这三个方面对二维晶体管进行协同优化和基准测试。逻辑器件的性能可以通过其内在延迟τ=CV/I来衡量,其中C是栅极电容,V =VDD是供电电压,I=Ion是导通状态电流。C可以通过缩短栅极长度和减少寄生电容来减小,这将在后面的“面积”和“功耗”部分以及VDD缩放中进一步讨论。

二维晶体管与硅晶体管进行比较 来源:论文

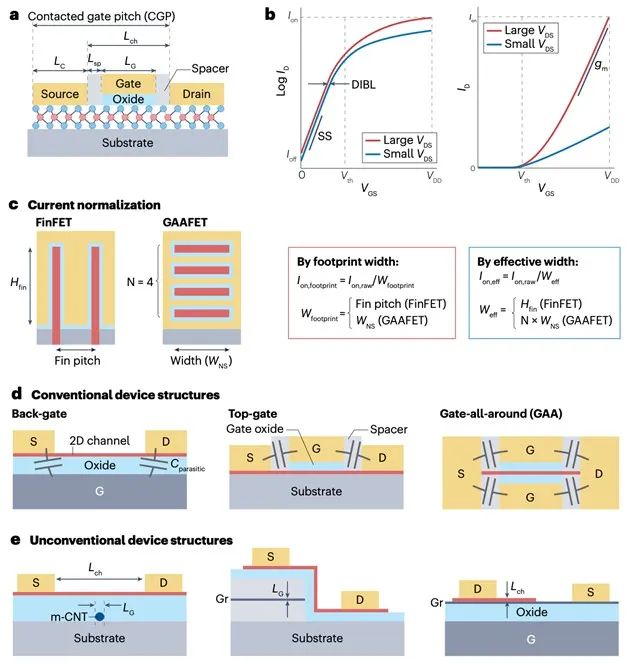

在性能方面,推荐使用本征门延迟τ和开态电流ION作为基准指标,并且应在给定供电电压VDD和关态电流IOFF目标的前提下比较ION,为了公平比较不同器件结构,建议使用有效宽度Weff(图c)进行电流归一化。

对于VDD缩放,栅极电压VG和漏极电压VD都需要降低,理想情况下应低于0.7V,这对于三维集成电路尤为重要,因为它需要更高的功率密度和更大的热耗散。这就需要高度缩放的沟道长度Lch和有效的栅极控制,以便在关态时实现陡峭的亚阈值摆动和较小的漏极致势垒降低(DIBL),在导通态时实现较高的跨导gm(图b)。虽然陡峭的亚阔值摆动对降低VDD和功耗很重要,但对于给定的ION和IOFF目标,它必须转化为较低的VDD,尤其是当陡峭的亚阈值摆动仅持续在有限的ID范围内或伴有较大的滞后时。值得注意的是,对于二维晶体管,欧姆触点对于增加导通电流和降低VDD非常重要,因为肖特基势垒的热场发射会导致更大的亚阀值波动。

栅极电容可通过缩小栅极长度和器件宽度来降低。为了减少寄生电容,在背栅结构中,栅极与源极和漏极有很大的重叠,导致寄生电容较大,工作频率较低(图d)。在功耗方面,降低VDD和寄生电容(图d)对降低功耗至关重要,推荐使用给定ION、IOFF目标下的VDD,以及能量延迟积(EDP)作为基准指标。

在面积方面,栅极长度LG和沟道长度Lch是重要指标,也应同时考虑接触和侧墙的尺寸,推荐使用接触栅极间距(CGP,图a)作为基准指标,而对于非传统器件结构(图e),应比较器件在芯片上实际占据面积。

这项工作为二维晶体管与硅基晶体管的对比提供了一个全面的基准测试框架,涵盖了性能、功耗和面积等关键方面,为未来二维晶体管技术的发展和产业化应用提供了重要指导。

扫码,立即预报名,了解详情

Carbontech 2024 W1馆部分参展企业:

说明:本文部分素材来自网络公开信息,由作者重新编写,转载请备注来源,本平台发布仅为了传达一种不同视角,不代表对该观点赞同或支持。