(本文编译自Semiconductor Engineering)

CXL已经从众多互连标准中脱颖而出,成为将内存连接到各种处理单元以及在数据中心内共享内存资源的一种可预测方式。

Compute Express Link(CXL)建立于PCIe基础上,目前几乎所有主要芯片公司都支持该技术。它通过串行通信连接CPU、GPU、FPGA 和其他专用加速器,同时它还允许跨设备池化内存,以提高资源利用率和高效利用率。

尽管CXL经常会被拿来与英伟达的NVLink进行比较,但它们的发展道路却不尽相同。“几年前,我们都认为许多加速器都会使用CXL作为一种廉价的、简单的方式来访问主机内存,”新思科技解决方案事业部PCIe控制器IP高级技术产品经理Richard Solomon表示,“但我们没有看到太多这样的情况。人们的兴趣不如我们的预期。我们只是看到,人们对CXL作为连接内存技术的兴趣非常浓厚。”

事实上,CXL从未打算覆盖所有应用。Rambus高级产品营销经理Zaman Mollah表示:“CXL早期主要用于内存扩展,增加容量和带宽、内存重用和智能内存分层应用。这些解决方案很容易使用现有的即插即用PCIe物理接口集成。CXL将与其他类似的互连技术共存,它拥有其独特的应用场景。CXL可能无法为以GPU为中心的AI应用提供所需的带宽,但它在加速器和基于CPU的AI用例中很有用。它允许可组合的数据中心架构,并提供一种灵活且经济高效的方式来增加内存容量和带宽,同时具有可接受的延迟性。”

此外,西门子数字工业软件VIP产品线高级总监Christopher Browy表示,CXL可能会被用于主机和相干加速器之间的内存池化和共享,并通过UALink和UltraEthernet结构进行远程横向扩展。“支持CXL和UALink的交换机很可能会面世。CXL还将考虑先进的多级内存、存储级内存和缓存解决方案以及优化计算存储。现在的CXL比几年前更适用于现实应用,它将在未来最新的新兴AI和HPC连接标准中占有一席之地。CXL是最好的选择,因为它以独特的方式实现了基于内存和缓存的扩展。虽然UCIe将根据多芯片设计重新定义芯片和IP市场,但CXL是它们如何在模块和机架级别协同工作的关键。”

CXL3.1规范增加了功能,包括增强的安全性

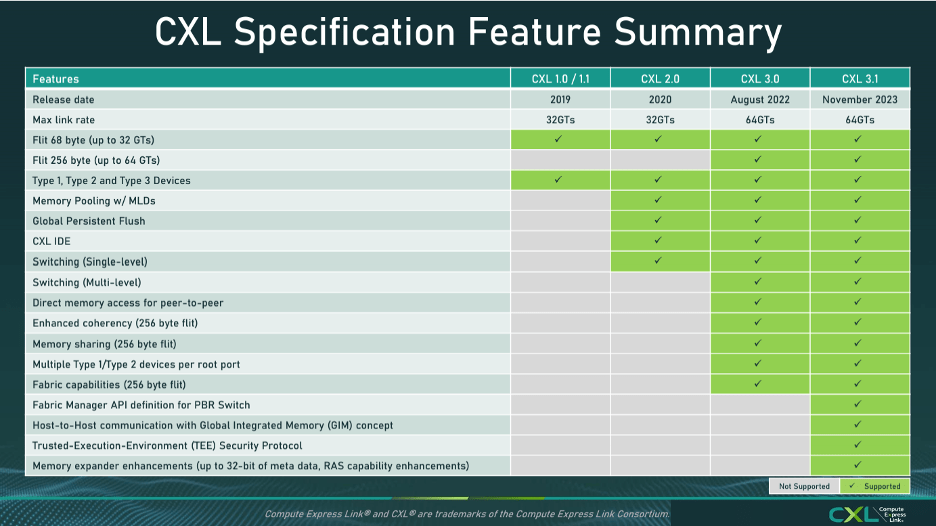

CXL标准最初于2019年3月发布,在过去几年中经历了多次修订。CXL3.0于2022年发布,最新的CXL3.1规范于2023年11月发布。3.0版中添加了许多新功能,3.1版中则添加了一些ECN(工程变更通知),以增强新功能的功能性,以实现结构功能。

CXL有三个子协议:CXL.io、CXL.cache和CXL.memory。其中,CXL.memory引起了设计人员的极大兴趣,因为他们意识到它能为数据中心和高级AI拓扑结构实现内存扩展。内存的构建依赖于来自英特尔、AMD和基于Arm的超大规模计算平台的基于CXL2.0的处理器。

据CXL联盟称,3.1规范“改进了结构可管理性,使CXL超越了机架并实现分离内存系统。CXL3.1规范以之前的迭代为基础,优化资源利用率,根据需要创建可信计算环境,扩展内存共享和池化以避免内存滞留,并促进加速器之间的内存共享。”

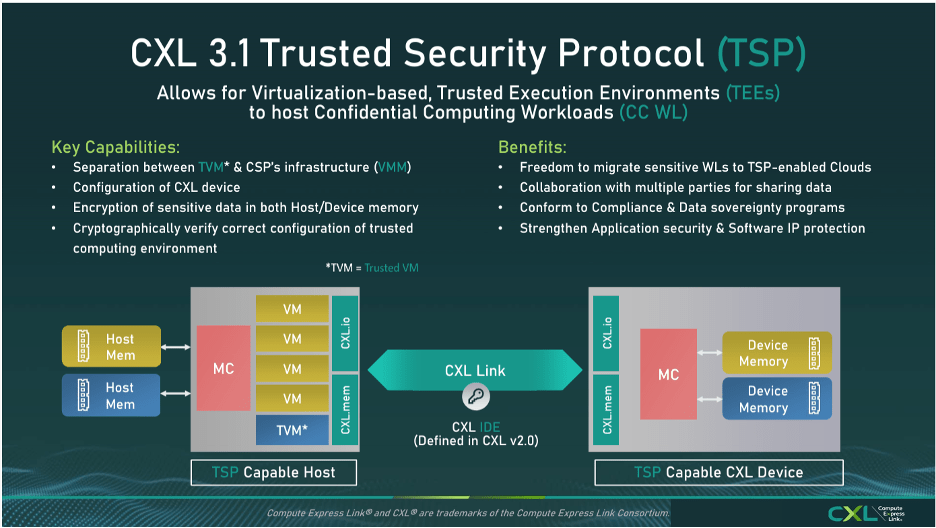

CXL3.1还包含其他功能,可进一步减少CXL结构中连接的端点和主机的延迟,以及新的安全协议。Rambus硅IP产品营销高级总监Lou Ternullo表示:“这些功能包括CXL.io对等(P2P)、无序I/O(UIO)、CXL.mem P2P,以及添加可信执行环境(TEE)操作代码以扩展PCIe传输层的完整性和数据加密(IDE)支持,通过路径中的交换机和重定时器在主机和端点之间提供受保护的路径。P2P允许PCIe/CXL设备直接访问flex总线上其他PCIe/CXL设备中的内存,而无需主机处理器。UIO允许事务通过传输层,而无需管理排序规则。”

图1:TSP增强了安全性。

图源:CXL联盟

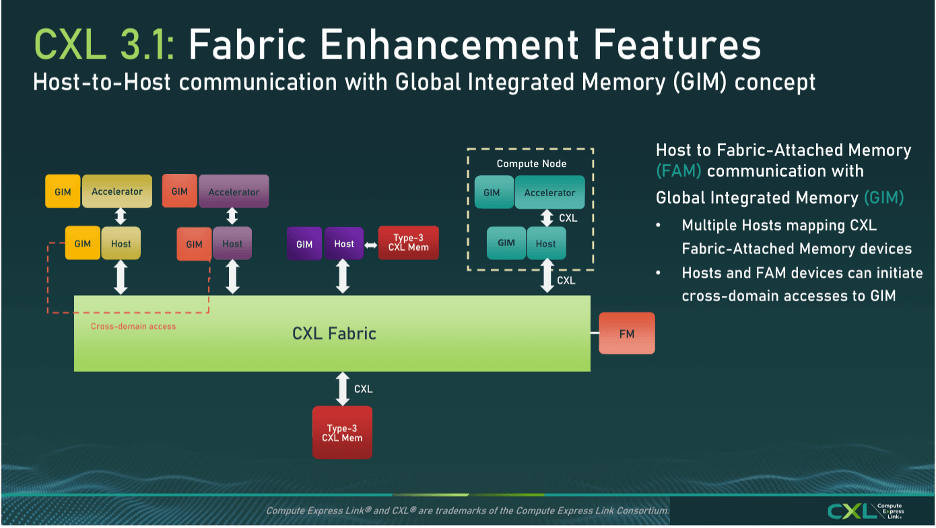

CXL3.1最大的变化是交换结构功能的改进。“现在它可以处理基于端口的路由,从而实现横向扩展部署。交换结构不受传统基于树的层次结构的约束,”Ternullo表示,“它允许主机和设备进行跨域访问,其中一台设备最多可以访问4,096台主机或其他设备。因此,设计人员可以实现大型系统或拓扑以及任意对任意通信。”

图2:CXL版本3.0和3.1扩展了协议的功能。

图源:CXL联盟

CXL3.1规范还进行了其他改进。“例如,使用全局集成内存(GIM)概念进行结构连接内存访问的主机间通信,”Rambus的Mollah说道,“CXL3.1还引入了可信安全协议以增强安全性。借助横向扩展部署功能,许多虚拟机将通过结构连接,因此安全性是一个非常重要的因素,需要加以考虑。CXL3.1中的扩展元数据功能(最多34位元数据)允许监控更多诊断数据和信息。所有这些都是横向扩展大型拓扑部署的重大突破。”

图3:新型全局集成内存(GIM)。

图源:CXL联盟

CXL联盟营销工作组联合主席、英特尔至强产品规划与营销部高级营销经理Anil Godbole解释说,按照最初的设想,CXL主要针对异构计算。CXL主要由英特尔开发。

Godbole表示:“CXL与PCIe的主要区别是一致性,因为CXL与PCIe在相同的I/O上运行。两种协议的基本PHY是相同的。但在连接时,CXL设备将作为CXL进行连接,主机将通过CXL与其通信,而PCIe设备(如果放在主板上的同一插槽中)将作为PCIe出现。当进行连接时,设备会说,‘我必须从这里使用CXL。’PCIe永远无法提供一致的内存。因此,展望未来,增加内存占用是CXL的最大用例。”

另一方面,他表示,“如果你不需要一致性,那么最好不要额外购买协议,你可以简单地将数据从一个点传递到另一个点。”

针对CXL无法与GPU配合使用的反对意见,Godbole指出,GPU需要CPU。“我们必须了解GPU是如何获得其工作负载的。最终,总是CPU开始执行神经网络工作负载。GPU没有自己的大脑,它只是一个由CPU提供数据的庞大矩阵乘法器。之前,总有人问我们能做些什么来从CPU中获取更多带宽?这是我们将在下一个规范中需要通过聚合CXL链路解决的问题。”

Cadence高级产品营销部总监Arif Khan表示,CXL如何处理内存池也受到了质疑。“从规范发布到支持1.1标准的初始OEM平台,该规范已经取得了长足的进步。尽管如此,实施者仍然对它产生了浓厚的兴趣,因为他们希望构建内存扩展器和池化设备。Levis等人在ACM论文中对内存池提出了批评,主要集中在成本、软件复杂性和实用性上。可供比较的公开数据集有限,这使得这篇文章读起来很有意思。然而,市场仍然对这个标准有需求,因为实施者正在围绕它构建解决方案。”

即使数据稀缺,内存池的经济性似乎也特别有吸引力。“未来,CXL将继续用于容量和带宽扩展,以及通过压缩内存进行内存分层,”Mollah表示,“随着每字节成本的降低,内存池用例等高级应用程序将变得更具吸引力,并允许以更低的TCO实现分散的数据中心基础设施。”

但CXL并不是唯一的选择。“随着针对特定用例的替代标准的兴起,该标准最近受到了一些质疑,”Khan表示,“自该规范首次公开发布以来的五年中,我们看到了人工智能加速器领域经历了指数级的增长。由于LLM用例在炒作周期中占据主导地位,系统正在针对这些应用进行优化。CXL一致性模型正受到目前正在构思的其他扩展标准的挑战。GPU制造商使用的专有标准已经就绪,并为这些特定应用设定了基准。无论如何,标准领域仍处于萌芽状态,市场需要一些时间来确定哪些标准最适合哪些细分市场。通常,商业动态会发挥巨大作用。”

Solomon表示,最好将CXL视为选择之一,就像内存多种产品种类来满足特定需求一样。“显然,有些应用不需要追求最快速度,尤其是考虑到其与价格和容量之间的权衡。如果回顾过去30多年来的每一种现代计算机架构,就会发现即使在缓存中也存在层次结构,因此显然存在非最快速度的内存用途,”他表示,“如果你追求极致速度,CXL可能不够快。但如果你正在构建一款快速、经济的设备,那么CXL可能是你的最佳选择。没有一种技术可以适用于所有领域。关键在于平衡。”

西门子的Browy对此表示同意。“由于CXL基于PCIe SerDes,因此具有更低的错误率、更低的延迟和相应的更低的带宽。NVLink和UALink使用以太网式SerDes会导致高错误率、高延迟和高带宽,因此在最高性能带宽受限的情况(如GPU到GPU)下,它们具有优势。在模块越来越多地基于UCIe连接的芯粒,作为通用和专用计算的基本构建块的世界中,CXL的真正优势在于需要一种强大的、低延迟方法来提供基于智能缓存的层次结构,包括现在的本地主内存、存储类内存以及不断发展的池化/共享和计算存储解决方案。这对于数据库、计算存储、通用计算、科学计算和作为GPU的人工智能(可以视为统一的智能内存)至关重要。”

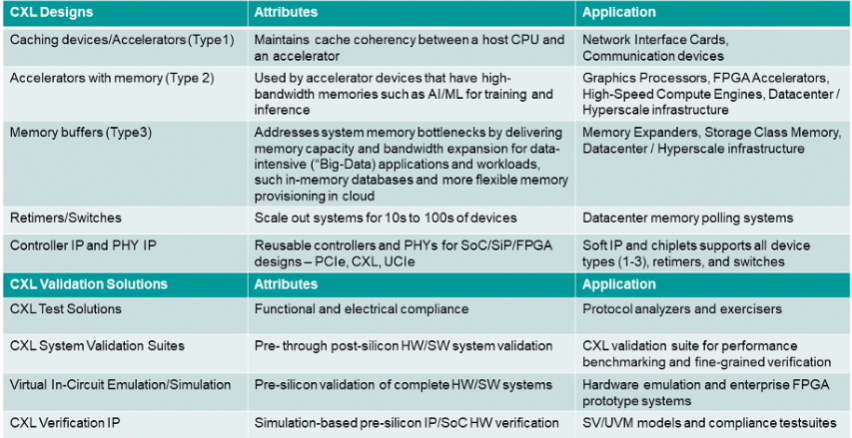

图4:CXL用例和验证解决方案。

图源:西门子EDA

未来展望

Ternullo相信CXL的作用将越来越大,他预计它将继续用于内存扩展。“此外,它将进一步实现异构计算和数据中心分解,帮助最大限度地减少服务器过度配置,并实现对内存、存储、加速等的按需访问。”

展望未来,据Yole Research预测,鉴于CXL在内存利用率、管理和分解以及可组合性访问方面的潜力,到2028年其市场规模将达到160亿美元。

CXL联盟的Godbole表示,这仅仅是个开始。“去年我们在进行测试,因为这是第一次可以添加内存并将其连接到服务器。我们只有有限的SKU支持CXL,这限制了其市场应用。随着我们推出CXL,每个CPU都将具有CXL功能,因此现在它正在成为主流。”

END