2024 年 Semicon Taiwan 国际半导体展完美落幕,先进封装成为突破摩尔定律的关键,尤其以面板级扇出型封装(FOPLP)成为备受关注的下一代技术,同时也是封测厂、面板厂极力布局的方向。

事实上,台湾地区封测厂推动 FOPLP 已有七八年,但因为良率问题未见显著成效,客户也持观望态度,因此没有太多终端应用落地。然而,台积电董事长魏哲家在 7 月 18 日法说会指出,正在研究 FOPLP 技术,预期三年后技术可成熟,无疑是给这项技术「添一把火」,内外地区设备商、封测厂、面板厂全热起来,一起冲刺技术落地。

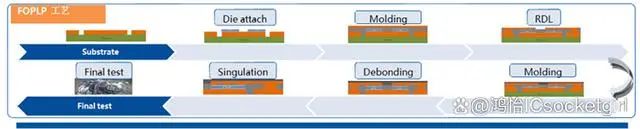

FOPLP 技术是 FOWLP 技术的延伸,以方形基板进行 IC 封装,可使封装尺寸更大、降低生产成本。据经济部说法,以面板产线进行 IC 封装,方形面积相较晶圆有更高的利用率,达到 95%,即相同单位面积下,可摆放更多的芯片数量。然而,因封装尺寸更大,面临面板翘曲、均匀性和良率问题。至于 FOPLP 的 Panel(面板)载板可采用 PCB 或者液晶面板用的玻璃载板,包括台积电在内厂商都开始研究玻璃载板的可行性。

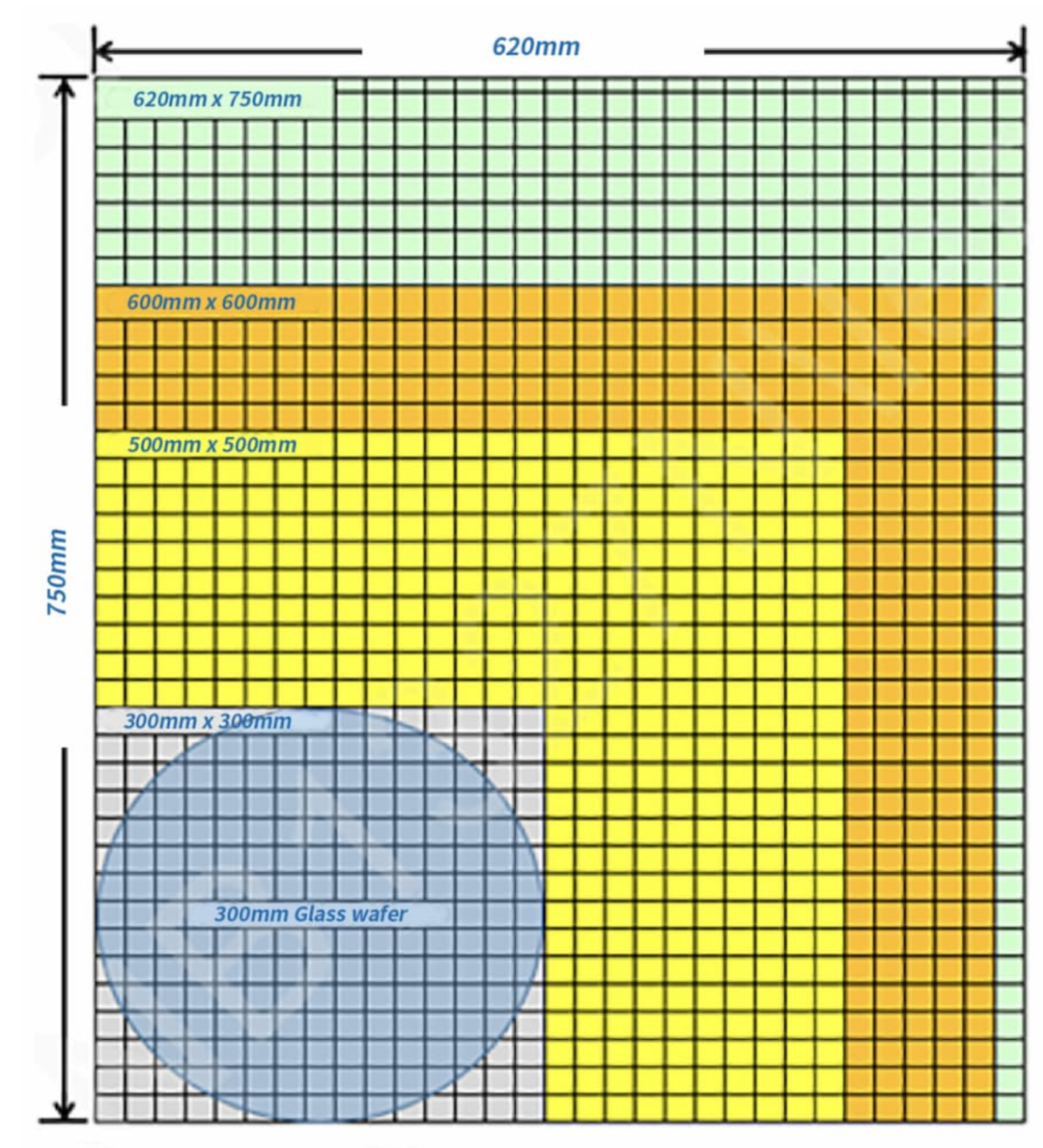

G3.5 FOPLP Glass Panel 生产面积。(Source:群创)

台积电开发的 FOPLP 可想象成「矩形 InFO」,整合台积电 3D fabric 平台其他技术,发展出 2.5D / 3D 等先进封装,以用于高阶产品应用,最快 2027 年亮相。据日经报导,台积电正与设备及原物料供应商合作研发面板级芯片封装技术,目前仍在早期阶段。据悉,试验中的矩形基板尺寸为 510×515mm,但有消息称新定案版本为 600×600mm。

半导体设备业者认为,FOPLP 生态链发展主要看台积电,但随着 AI 持续发展,在算力提升又必须兼顾成本的考量下,FOPLP 仍是未来需发展的方向。这项技术应该不会取代 CoWoS,而是提供客户在成本考量下的新解决方案。

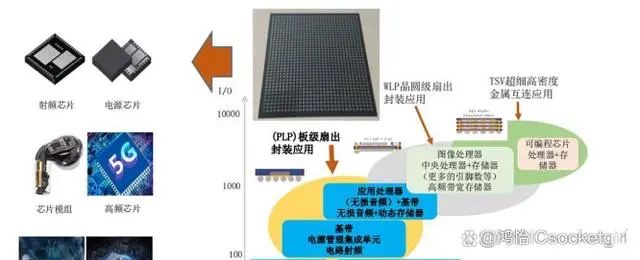

随着半导体技术的迅猛发展,对芯片封装工艺的要求也不断增长。尤其是针对高频、射频、电源和传感器等芯片的处理,封装技术的发展显得尤为重要。而在众多封装技术中,扇出型面板级封装(Fan-Out Panel Level Packaging, FOPLP)以其独特的优势逐渐脱颖而出,成为行业的焦点。

FOPLP板级封装技术特点

1. 扩展封装面积

FOPLP技术将单个芯片及其周边电路安装在更大面积的材料面板上,形成扇出形状。这种方法可以显著减少芯片间连线的长度,从而降低传输损耗和讯号干扰,提高电性能。

2. 提高集成度

与传统封装技术相比,FOPLP能够容纳更多的芯片和功能集成在一起,适合于复杂的多芯片模组封装。FOPLP通过增加面板面积来增加封装密度,使得更多功能单元可以集成在有限的空间内,从而提高系统性能。

3. 优化热管理

FOPLP技术在封装过程中使用了更优质的热导材料,通过合理设计提升散热能力,降低芯片运行温度,增强可靠性和寿命。

FOPLP在不同芯片类型中的应用

射频芯片

在射频芯片领域,FOPLP技术拥有显著的优势。射频芯片对信号稳定性和降噪能力有很高的要求。FOPLP技术能够更有效地隔离噪声干扰,提供更好的信号传输路径,同时通过封装结构的优化提升信号质量和传输速率。

电源芯片

电源芯片需要高效的散热性能,以及良好的电性能和机械强度。FOPLP技术通过高密度集成和优化散热路径,保障电源芯片在高功率条件下的稳定运行。此外,FOPLP技术还提供卓越的机械强度,确保封装的稳定性和可靠性。

芯片模组

芯片模组是多种芯片协同工作的系统单元。FOPLP技术能够通过集成多个芯片在一块面板上,简化模组设计,提高系统集成度。此外,FOPLP技术优化了芯片之间的互连结构,提高模块的整体性能和可靠性。

高频芯片

高频芯片在通信设备中起着至关重要的作用,要求拥有高带宽、低延迟和高信号传输质量。FOPLP技术在封装过程中可以有效降低信号损耗,优化信号传输路径,从而提高高频芯片的性能和可靠性。

数字芯片

数字芯片涵盖了处理器、控制器等核心组件。FOPLP技术通过改进封装设计,提高芯片的散热和电性能,使得数字芯片在工作过程中能够更加稳定和高效地运行。

传感器芯片

传感器芯片用于检测和反馈环境变化,对体积和能耗要求较高。FOPLP技术通过优化封装面积和电路设计,提高传感器芯片的灵敏度和精度,同时降低功耗和提升抗干扰能力。

FOPLP封装对芯片测试的优势

1. 更高的测试效率

FOPLP封装由于集成度高、封装面积大,能够在一次测试过程中检验更多的芯片。相较于传统封装技术,FOPLP封装显著提高了测试效率和测试速度,降低测试成本。

2. 提供更全面的测试数据

由于FOPLP封装技术优化了芯片之间的连接和信号传输路径,使得在测试过程中能够获得更全面、更准确的测试数据,提供了更好的芯片性能评估基础。

3. 改善散热性能

在测试过程中,芯片的温度管理尤为重要。FOPLP封装技术通过优化散热路径,确保芯片在高功耗运行条件下的温度控制,从而提高测试结果的准确性和稳定性。

4. 灵活的测试方案

FOPLP封装技术具备高度的灵活性,因此可以根据不同芯片的特性和需求进行个性化的测试方案设计。无论是高频芯片、射频芯片还是电源芯片,FOPLP封装技术都能够提供适合的测试方案,保障测试结果的一致性和可靠性。

定制化测试座的必要性

尽管FOPLP封装在许多方面展现了巨大的优势,但在芯片测试过程中,测试座的设计和制造往往需要针对具体应用进行定制。这是因为不同类型的芯片及其应用场景对测试座的要求各不相同,包括:

1. 特定的电性和机械要求

不同类型的芯片在测试过程中需要具备特定的电性和机械要求。例如,高频芯片需要具有优良的信号隔离能力,电源芯片需要良好的散热性能等。因而,测试座的设计必须根据芯片的具体特性进行专门设计。

2. 高度灵活的连接结构

FOPLP封装中的高集成度和多芯片共存特性,要求测试座需要具备高度灵活的连接结构,以适应不同芯片的测试需要。标准化的测试座往往难以满足这一需求,因此定制化的设计成为必要。

3. 精确的数据采集和分析能力

高性能芯片对测试数据的精度和分析能力有着很高的要求,为了能够精确采集和分析测试数据,测试座必须具备专业化和高精度的设计。标准产品无法完全满足这一需求,必须根据具体芯片进行定制。#百家快评#

随着芯片技术和封装工艺的发展,FOPLP板级封装凭借其优异的扩展性、高集成度和优化的热管理能力,在射频芯片、电源芯片、传感器芯片等领域展现了显著的技术优势。同时,FOPLP封装在芯片测试过程中具备更高的效率和更全面的数据获取能力。但由于不同芯片在电性能、机械要求及连接结构方面的特性各异,测试座需针对具体应用进行定制,确保测试过程的准确性和可靠性。

台积电布局 FOPLP 以前,早期投入这项技术的台湾地区厂商包括力成、群创和日月光。力成 2018 年在新竹科学园区三厂开始兴建,启动全球第一座 FOPLP 量产基地,正式布局高阶封装领域。执行长谢永达指出,看好未来在 AI 世代,异质封装将采用更多 FOPLP 解决方案,预计 2026~2027 年会导入量产。

封测龙头日月光 FOPLP 产品将在明年第二季开始出货,面板尺寸从 300×300mm 已经扩张至 600×600mm,目前高通与其洽谈 PMIC(电源管理IC)产品。此外,AMD 也与日月光、力成洽谈 PC CPU 产品。

面板大厂群创近年积极转型,自 2017 年便投入研发,目前试量产线月产能约 1,000 片,今年下半年可望量产。目前首期产能已被订光,并开始启动第二期扩产计划,主要客户为恩智浦、意法半导体等国际 IDM 大厂,未来将视客户需求将月产能逐步提升至 15,000 片,以 PMIC 产品为主。

盘点台湾地区 FOPLP 相关供应链,有湿制程领域弘塑、溅镀/水平式电浆蚀刻设备厂友威科、雷射修补设备商东捷、载板干制程设备厂群翊、RDL制程设备亚智科技、电浆清洗及雷射打印厂商钛升、自动化设备商万润、开发 FOPLP 特殊合金载板鑫科材料等。

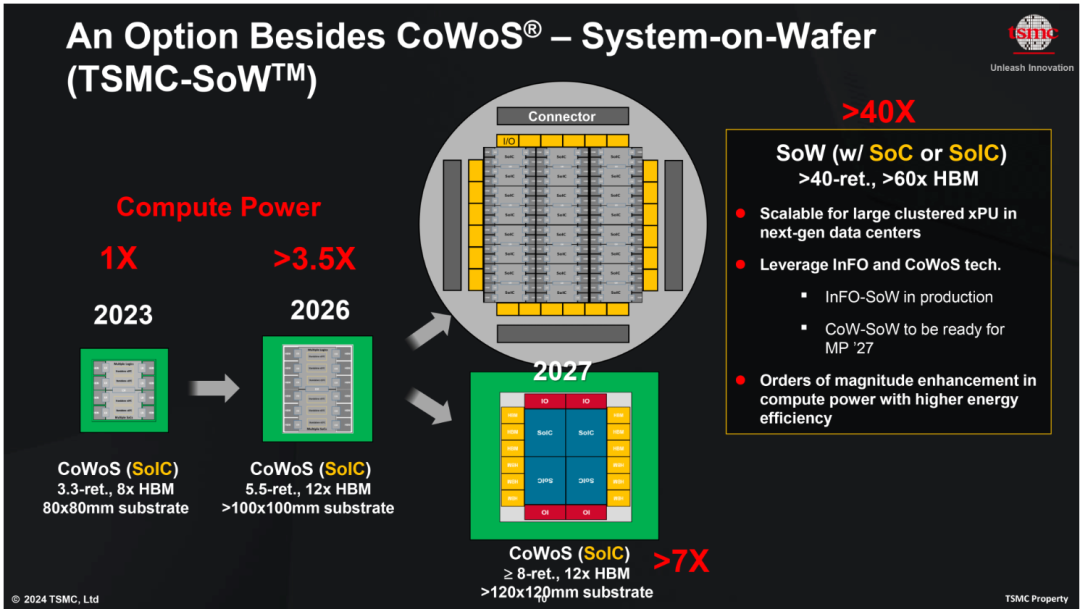

随着先进封装转换至 panel level(面板级),半导体设备商将提出另一个说法,即所谓的「CoPoS」(Chip-on-Panel-on-Substrate),即是 CoWoS「面板化」,以面板(Panel)取代晶圆(Wafer),将芯片排列在矩形基板上,最后再透过封装制程连接到底层的载板上,让多颗芯片可以封装一起。

CoPoS 这项技术处于早期初期,初步判断需要三五年才有机会到位,目前仍以 CoWoS、FOPLP 是较为明确的技术路线图。

然而,FOPLP 受限于线宽及线距问题,目前应用仍以 PMIC 等成熟制程为主,待技术成熟后才会导入到主流消费性 IC 产品,TrendForce 预期时间约落在今年下半年至 2026 年;至于更高阶的 AI GPU 应用,则是 2027-2028年有望落地,与台积电董事长魏哲家预期至少三年后的量产时间相一致,他表示,目前尚未有成熟的解决方案,支持大于十倍光罩尺寸(Reticle size)芯片,预期三年后 FOPLP 将开始导入后,台积电也将做好准备。

联系我们

CINNO 公众号矩阵

更多商务合作,欢迎与小编联络!

扫码请备注:姓名+公司+职位

我是CINNO最强小编, 恭候您多时啦!

CINNO于2012年底创立于上海,是致力于推动国内电子信息与科技产业发展的国内独立第三方专业产业咨询服务平台。公司创办十二年来,始终围绕泛半导体产业链,在多维度为企业、政府、投资者提供权威而专业的咨询服务,包括但不限于产业资讯、市场咨询、尽职调查、项目可研、管理咨询、投融资等方面,覆盖企业成长周期各阶段核心利益诉求点,在显示、半导体、消费电子、智能制造及关键零组件等细分领域,积累了数百家中国大陆、中国台湾、日本、韩国、欧美等高科技核心优质企业客户。