在功率模组封装中,焊料的疲劳与键合线故障导致的失效是器件和模组失效的主要原因。其中,芯片下方的散热通道是散热的主要途径,芯片下焊料是其中的重要组成部分,也是最容易发生焊料疲劳退化的位置。

传统钎焊料熔点低、导热性差,在工作期间产生的热循环过程中,由于材料间CTE差异,在材料间产生交变的剪切热应力,在应力的连续作用下,容易导致焊料层疲劳老化、产生裂纹,进而发展为材料分层,由于裂纹和分层的产生,焊料层与各层材料间的接触面积减小,热阻变大,加速了焊料层的失效,难以满足车规高功率SiC器件封装的可靠性及其高温应用要求。为解决高功率密度车用模块中芯片下焊料疲劳与键合线故障问题,翠展微电子针对Tpak SiC系列封装提出了一个创新解决方案,银浆烧结+铜Clip方案。芯片与AMB间的连接方式采用银浆烧结,代替传统焊料。银的熔点高达961℃,不会产生熔点小于300℃的软钎焊连接层中出现的典型疲劳效应,大幅提高了模块的功率循环能力。同时芯片上表面用leadframe一体化的铜Clip替代铝线键合,减小了模块内部的杂散电感,提升了芯片表面电流的均流性,增强了模块整体的过流能力。铜比铝更优异的导热能力也提升了模块整体的散热能力。有效地提升了模块整体的出流能力和可靠性。铜Clip技术:铜Clip是一种替代传统焊接线的连接方式,它通过物理接触直接连接到功率半导体芯片的顶部,高强度、高导电性的铜材料,确保了优良的电流传输能力。这种方式减少了传统焊接线所导致的寄生电感,同时由于铜材质的高导电性,还可以减少电阻损耗,进而提升效率。

AMB陶瓷基板:AMB指的是活性金属化烧结技术,它使用金属(通常是铜)与陶瓷基板进行直接烧结,形成非常坚固且导热良好的连接。AMB基板用于支撑芯片并提供高效的热路径。提高了热导率和机械稳定性。

银浆烧结:银浆烧结技术用于连接芯片与AMB基板,代替了传统的焊料技术。这种方法提高了热性能和机械强度,因为银具有较高的导热率并且烧结形成的连接比焊料更可靠。避免了传统焊料可能引起的热循环疲劳。典型技术参数:

- 工作温度范围:通常适用于较宽的工作温度范围,如-40°C至+150°C,具体取决于材料选择和设计。

- 电流密度:相较于传统键合线方案,TPAK铜Clip单管方案能够支持更高的电流密度,可达几十甚至上百A/mm²。

- 导通电阻(Rds(on)):由于使用了低电阻的铜Clip连接,导通电阻相对较低,有助于提高效率。

- 热阻(RθJA):通过AMB陶瓷基板和有效的散热设计,热阻可显著降低,典型值可能在几K/W到十几K/W之间。

- 寄生电感:由于铜Clip的设计减少了引线长度,因此寄生电感也相应减小,有助于减少电磁干扰(EMI)和提高开关速度。

主要优势

- 高功率密度:TPAK封装设计允许更高的电流密度通过较小的空间,这得益于铜Clip的低电阻特性和AMB基板的良好热传导特性。

- 可扩展性:模块化的设计使得TPAK封装易于扩展,可以根据不同的功率要求灵活调整模块配置。

- 可靠性高:银浆烧结和铜Clip的组合减少了传统焊料和键合线可能带来的疲劳和故障风险,从而提高了整个系统的可靠性。

- 抗震动性能:铜Clip相比细长的键合线更能抵抗机械应力,因此在振动环境中表现得更好。

- 成本效益:尽管初期投资可能较高,但由于其高效能和可靠性,TPAK封装可以在长期运行中节省维护和更换成本。

- 降低热阻:通过改善热管理,TPAK封装可以帮助延长器件的使用寿命并提高整体系统效率。

- 降低杂散电感:由于采用了铜Clip而非键合线,TPAK封装方案可以大幅减少杂散电感,这对于高频开关应用尤为重要。

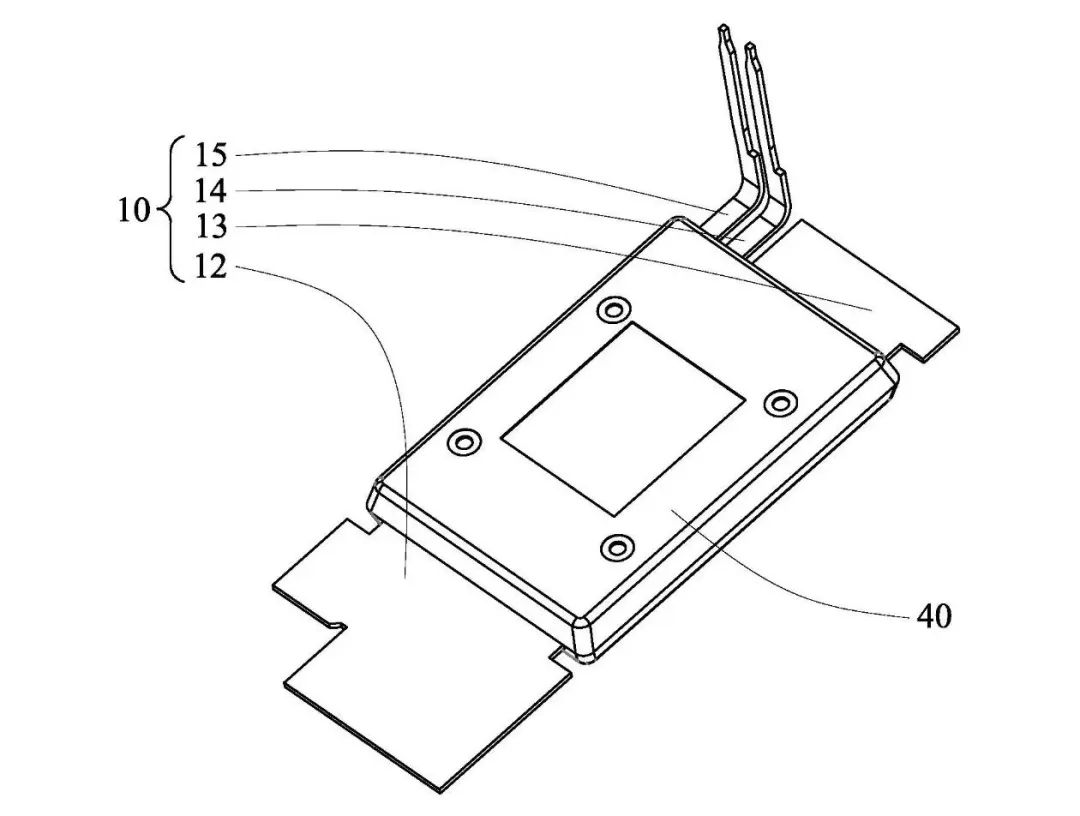

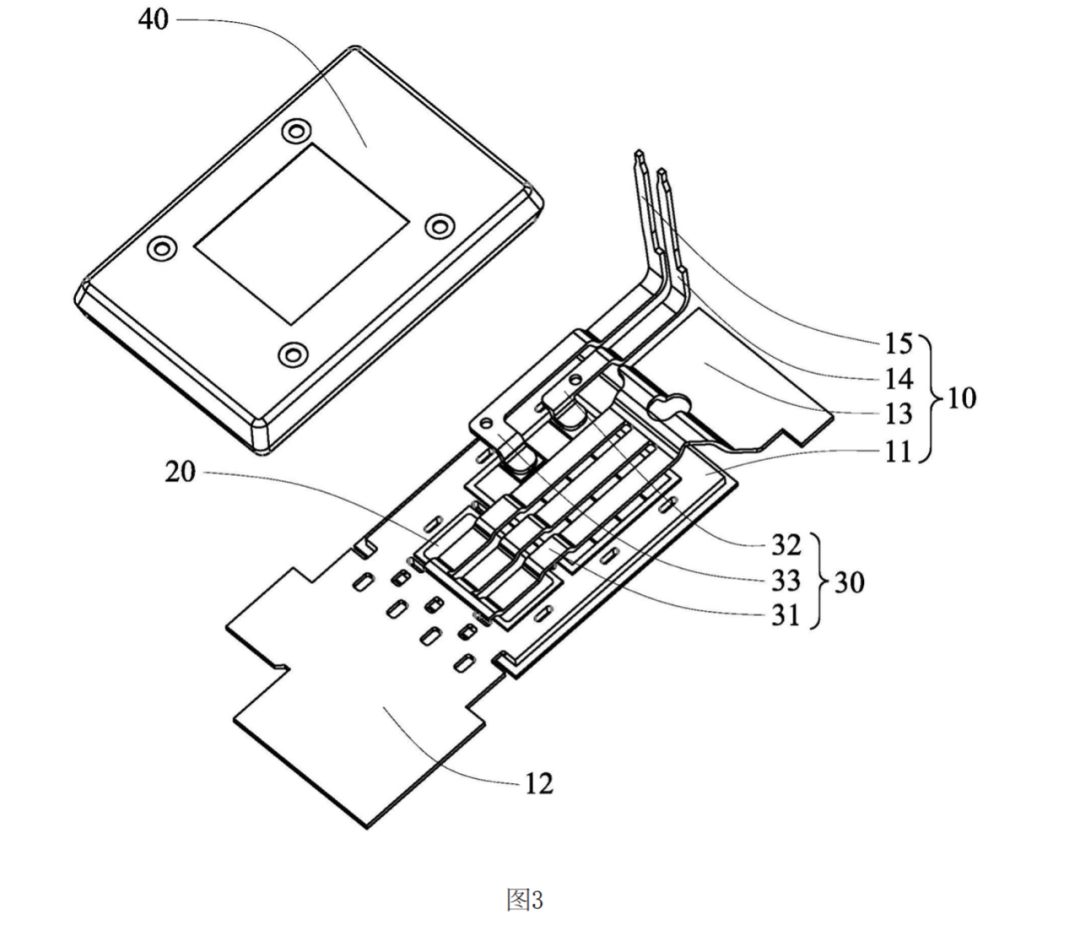

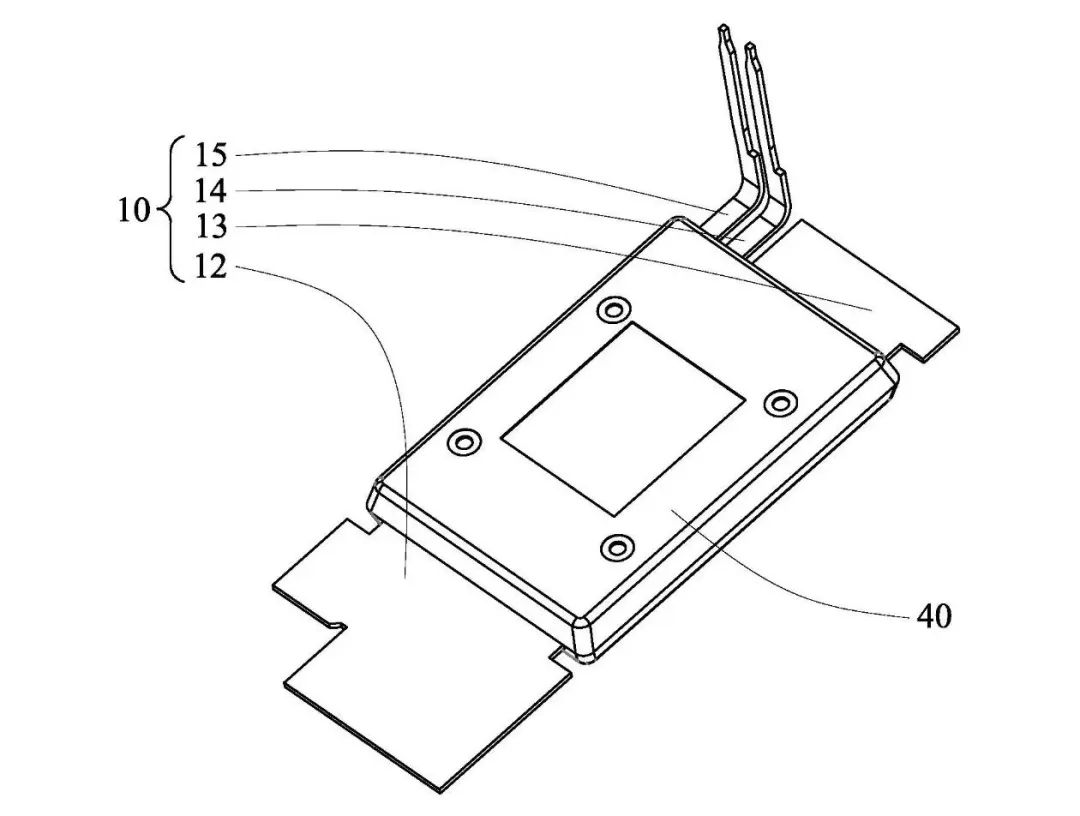

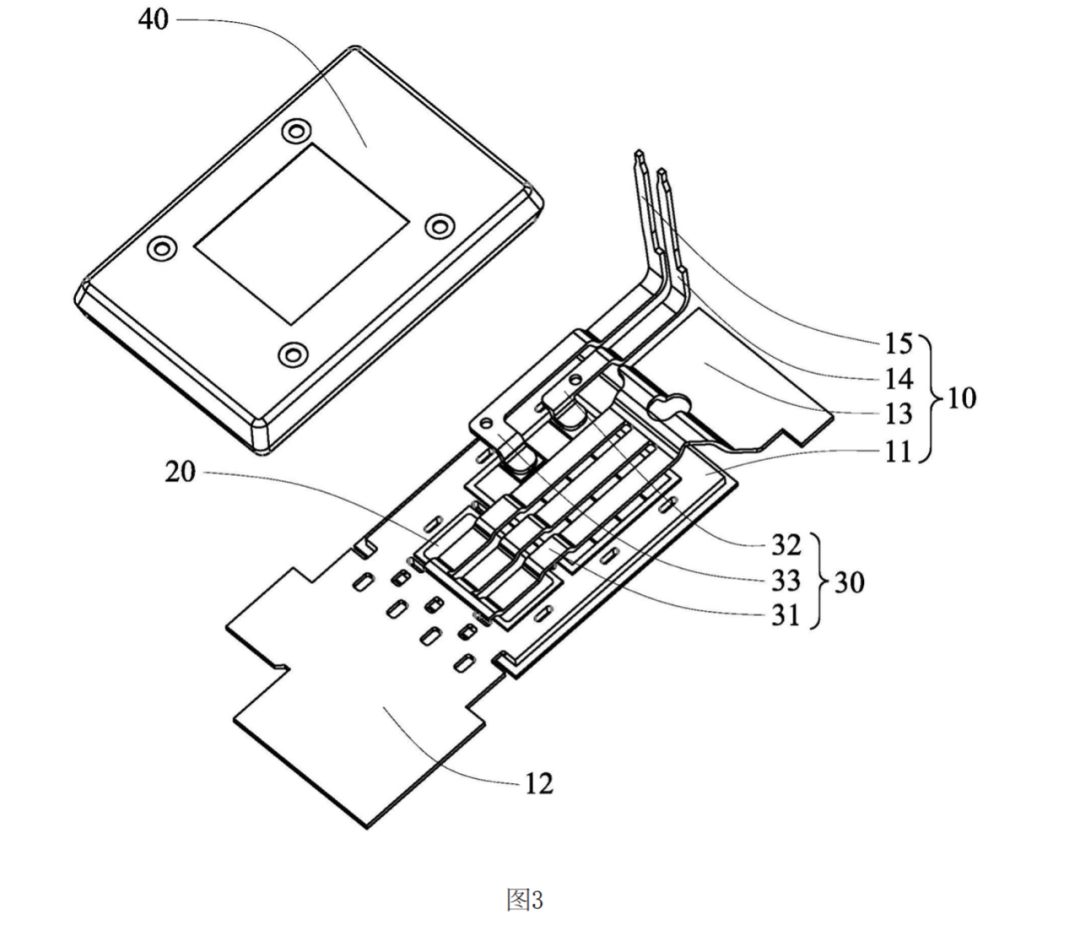

昨日,翠展微获得了一个申请于去年12月的专利授权《一种TPAK铜clio单管塑封结构》其包括载体层,TPAK器件层,连接层,盖板。所述载体层包括DBC上铜层第一功率端子,第二功率端子,发射极信号端子,门极信号端子。所述连接层包括第一连接结构,第二连接结构,第三连接结构。与现有技术相比,本实用新型通过设置所述连接层,采用Cu-Clip连接,电流分布更加均匀,信号端子波形更加稳定,避免了键合线脱落从而景响寿命及可靠性。同时通过设置一体成型的所述第一功率端子与DBC上层,减少了焊料的使用,降低焊料失效的风险,同时芯片布局空间变大,减少热耦合的影响,回流焊下残余应力也降低。最后通过塑封,使得结构更加稳定,信号端子不会在使用的过程中有脱离的风险。

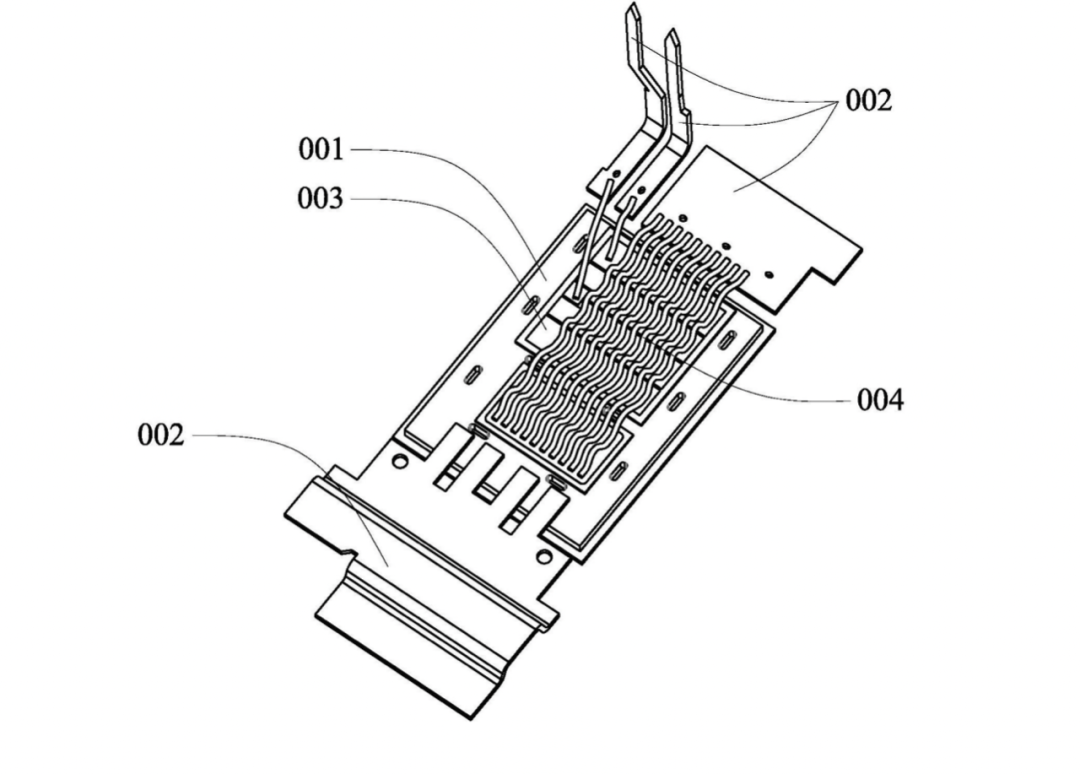

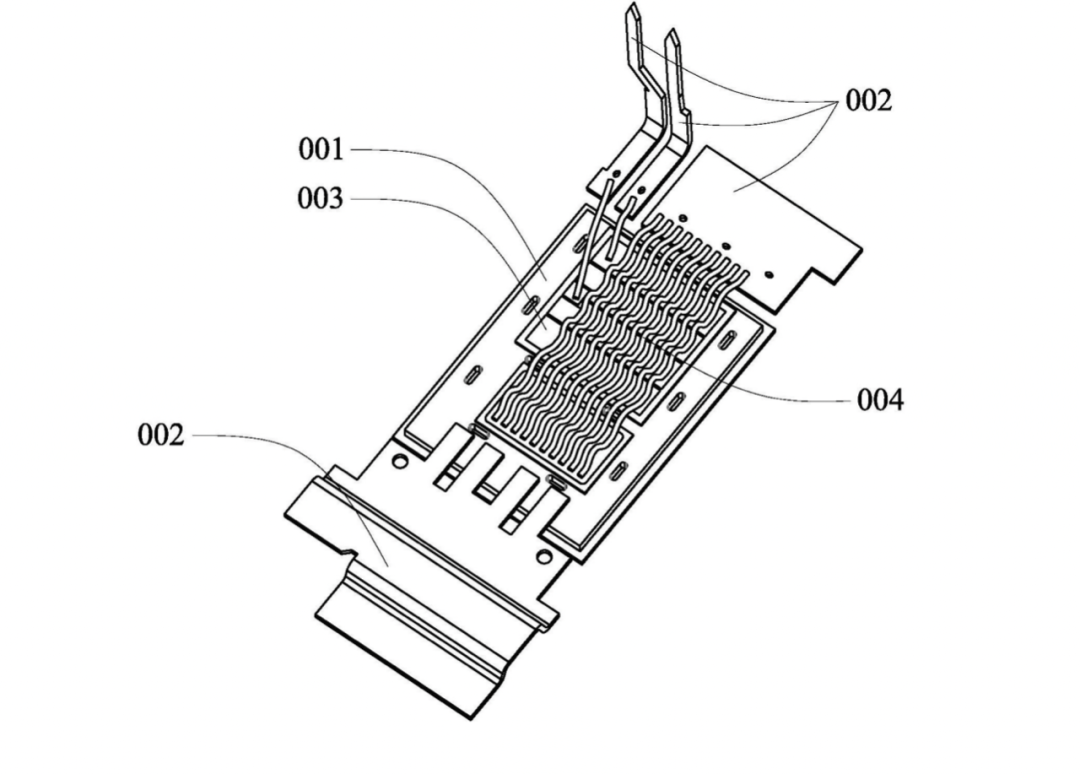

根据专利说明书介绍,TPAK封装是采用介于单管和常规模块之间的单开关模块(Single SwitchModule)设计,既超越了之前单管封装带来的输出电流、输出功率、寄生电感等限制,又保留了多管并联的灵活性,可以根据不同的逆变器功率输出需求,来选择TPAK模块并联数量。目前的TPAK单管模块,一部分单管芯片与功率端子采用键合线连接,一部分使用铜clip连接,但信号端子几乎采用键合线,也有发射极信号端子与功率端子连成一体门极信号端子都采用键合线连接。功率端子采用焊接方式与DBC连接。

现有技术的TPAK单管模块,包括一个上铜层001,以及多个功率端子002,各个功率端子002与芯片003之间均采用铝线004进行连接,存在以下问题:1)采用键合线的可靠性不足,连接信号端子的键合线往往更容易脱落,同时采用键合线的杂散电感较高;

2)功率端子焊接到DBC也存在焊料失效的风险,同样占据芯片空间,不利于排布。

有鉴于此,本实用新型提供了一种可以解决上述问题的TPAK铜clip单管塑封结构。

其包括一个载体层,一个设置在所述载体层上的TPAK器件层,一个设置在所达TPAK器件层上的连接层,以及一个设置在所述载体层上的盖板。所述载体层包括一个DBC上铜层,一个与所述DBC上铜层连接的第一功率端子,一个设置在所述DBC上铜层一侧的第二功率端子一个设置在所述DBC上层一侧的发射极信号端子,以及一个设置在所述DBC上铜层一侧的门极信号端子。所述第一功率端子与所述DBC上铜层一体成型。所述TPAK器件层采用多个并联设置的芯片。所述连接层包括多个连接在所述第二功率端子与所述TPAK器件层之间的第一连接结构,一个连接在所述发射极信号端子与所述TPAK器件层之间的第二连接结构,以及一个连接在所述门极信号端子与所述TPAK器件层之间的第三连接结构。所述第一连接结构为一个从所述第二功率端子延伸出来的板状结结构且与所述第二功率端子一体成型。所述第二连接结构为一个从所述发射极信号端子延伸出来的板状结结构且与所述发射极信号端子一体成型。所述第三连接结构为一个从所述门极信号端子延伸出来的板状结结构且与所述门极信号端子一体成型。所述第一连接结构、第二连接结构及第三连接结构均通过Cu-Clip互连技术连接在所述TPAK器件层上。所述盖板通过塑封技术将所述TPAK器件层与连接层封装在内。

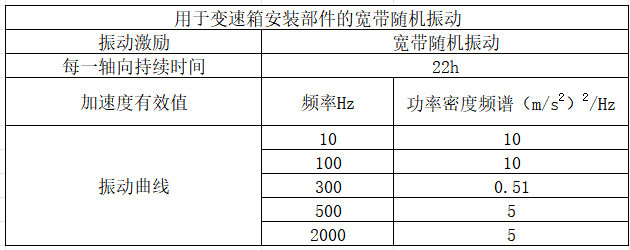

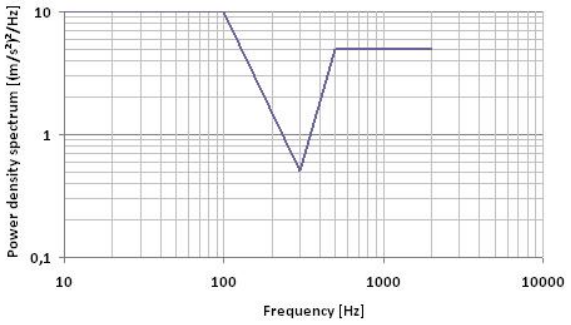

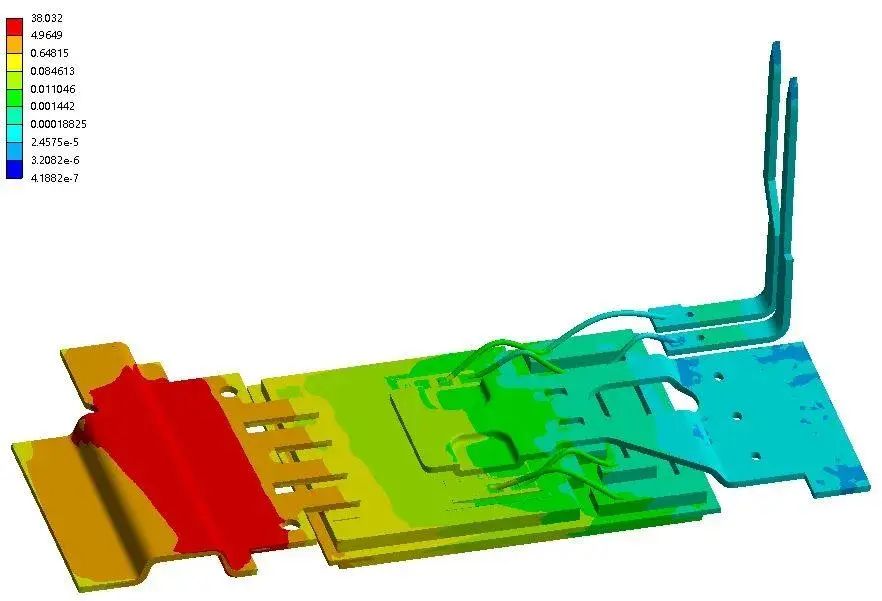

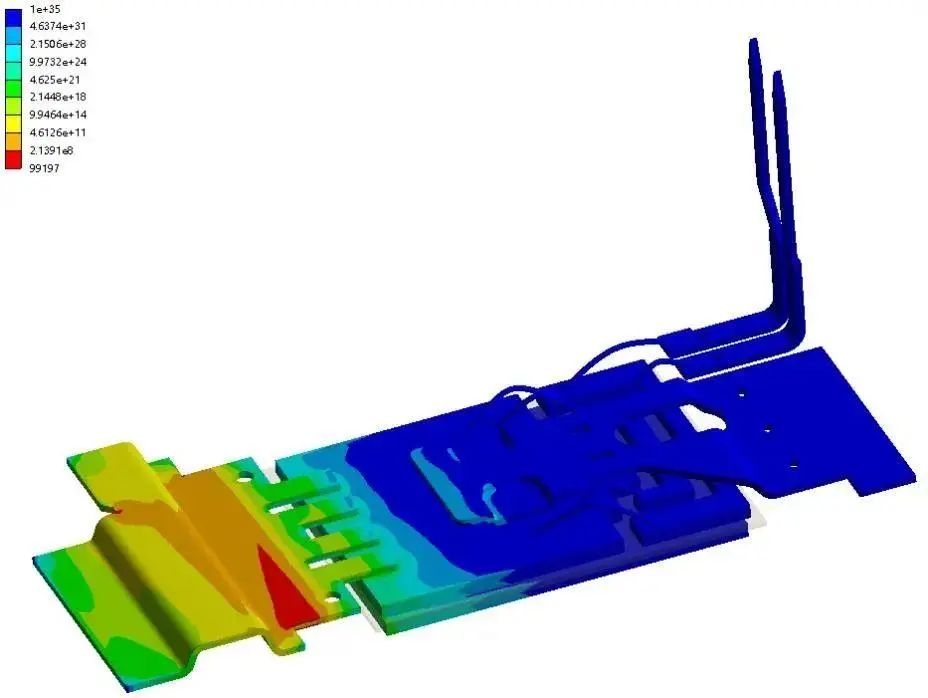

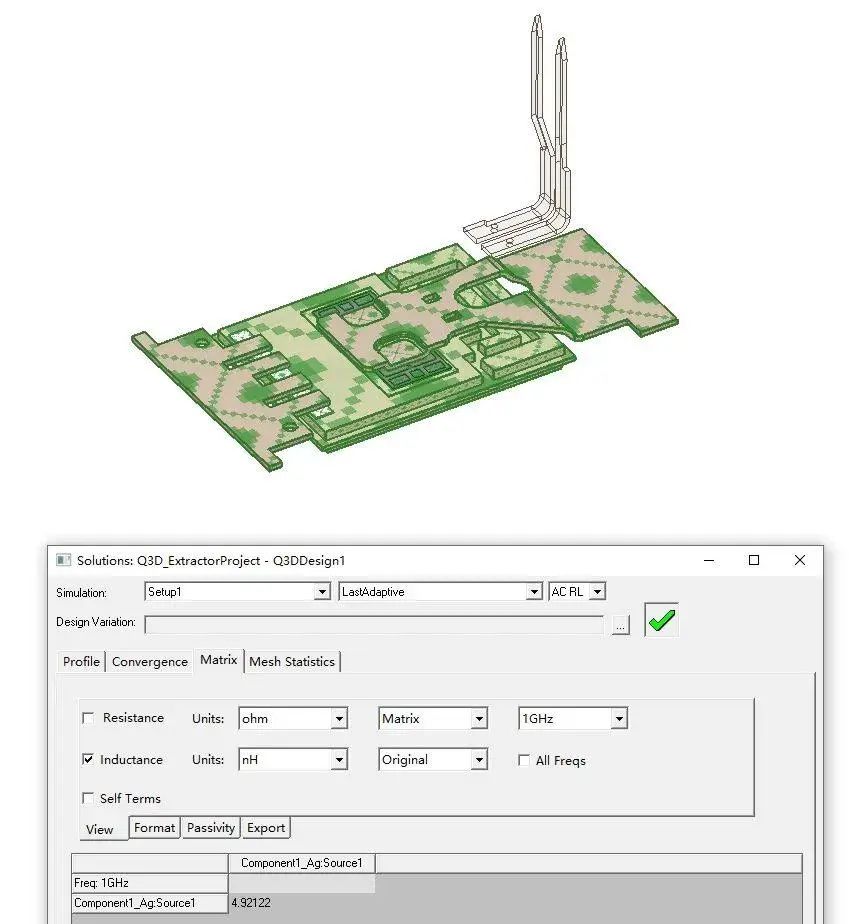

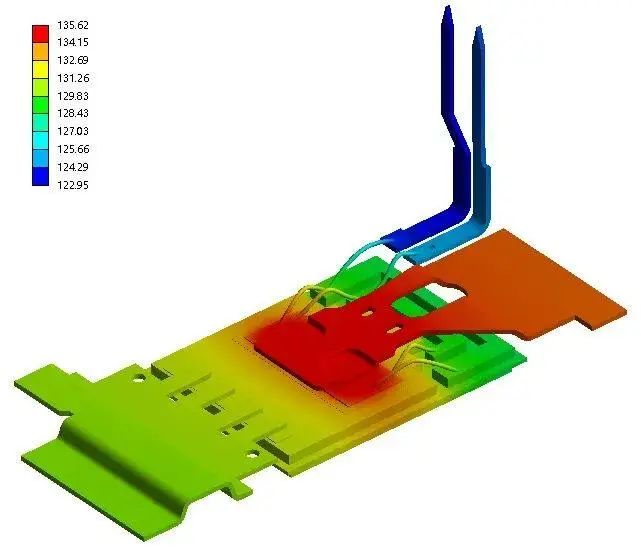

根据此前翠展微披露的Cu-ClipTPAK模组仿真结果看,按照AQG-324标准,获取模块在随机激励条件下的振动频率,研究Clip方案模块被迫抵抗外部随机振动的能力与结构设计合理性。

根据仿真结果,模块整体应力较小,最大应力出现在与塑封体相交的铜排端子处部位,其中最大应力不超38MPa,安全系数取1.35,满足安全使用条件。在对应PSD频谱作用下,模块最易损坏的部分是与塑封相交的铜排端子处部位,与模型的应力分布相吻合,其中模块最低寿命为9.9×104s满足22h要求。电感部分对模块整体电感进行仿真,仿真结果模块电感4.9nH满足设计要求。前期验证考虑芯片最大结温是否满足芯片耐受温度。使用软件PLECS,依据数据手册计算相应芯片损耗,根据热仿真结果芯片最高温度小于140℃,满足设计要求。总的来说,翠展微电子Tpak器件系列采用银烧结和Clip技术实现了高可靠性、低热阻、低杂散电感器件设计。银烧结技术使用银浆替代传统焊料,降低模块整体热阻,提高芯片和AMB互连的可靠性,有效增强模块的功率循环能力。Clip技术利用Leadframe一体化的铜排代替键合铝线,可以有效地减小模块内部杂散电感,拥有更高的电流输出能力的同时可以增强芯片的散热,提高模块的可靠性。文章来源:国家知识产权局《一种Tpak铜clip单管塑封结构》翠展微电子TPAK SiC系列解决方案:银浆烧结+铜Clip方案*免责声明:本文由作者原创。文章内容系作者个人观点,碳化硅芯观察转载仅为了传达观点,仅代表碳化硅芯观察对该观点赞同或支持,如果有任何异议,欢迎联系碳化硅芯观察。