在ARM cortex-M系列的CPU中,连接在一起的称为NVIC(Nested Vectored Interrupt Controller),cortex-A/R系列的CPU中使用的GIC(Globe Interrupt Controller), 而在RISC-V中,也有相应的一套中断控器称为CLINT(Core-Local Interruptor)+CLIC/PLIC(platform-level interrupt controller)。

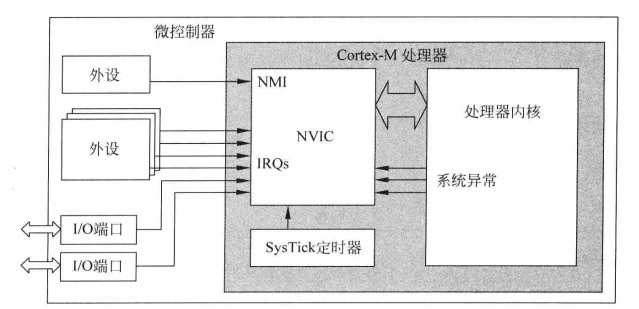

由于篇幅有限,本文重点介绍NVIC与CLINT。NVIC的结构如下图所示:

之所以称之为嵌套中断向量控制器,从“nested”二字可以看出该中断具备中断嵌套的,其实GIC/CLINT也支持中断嵌套,但是NVIC最为特殊,因为它相比GIC/CLINT,一旦产生中断后,CPU总中断不会被硬件关闭,在中断里面允许更高优先级中断打断,而GIC/CLINT触发中断时,CPU会关闭总中断,在中断处理过程中,不会响应任何中断,包括更高优先级中断,因为总中断是关闭着的, 因此想要在GIC/CLINT上达到和NVIC相同的效果,软件必须主动开启总中断。从“vectored”可以看出,NVIC 的中断是向量类型的,原来中断还有很多讲究,分为向(矢)量类型和非向量类型。对于GIC来说,中断则是非向量类型的。而作为ARM的后来者RISC-V则表现出了非常灵活的一面,既支持向量类型,也支持非向量类型,软件可配。

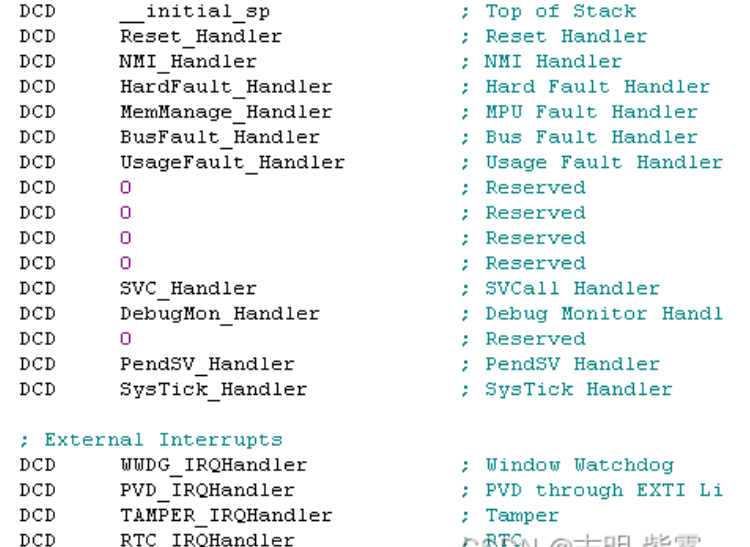

对于向量类型中断而言,CPU一旦响应中断,则会从 各个中断编号的固定的地址入口跳转运行,如下图STM32中断向量表所示。其中前1~15(SysTick_Handler)号向量中断属于cortex-M CPU特有的,任何芯片设计公司都会遵从这个约定,而15号以后的(WWDG_IRQHandler)则是各家芯片设计公司自己定义的一套。

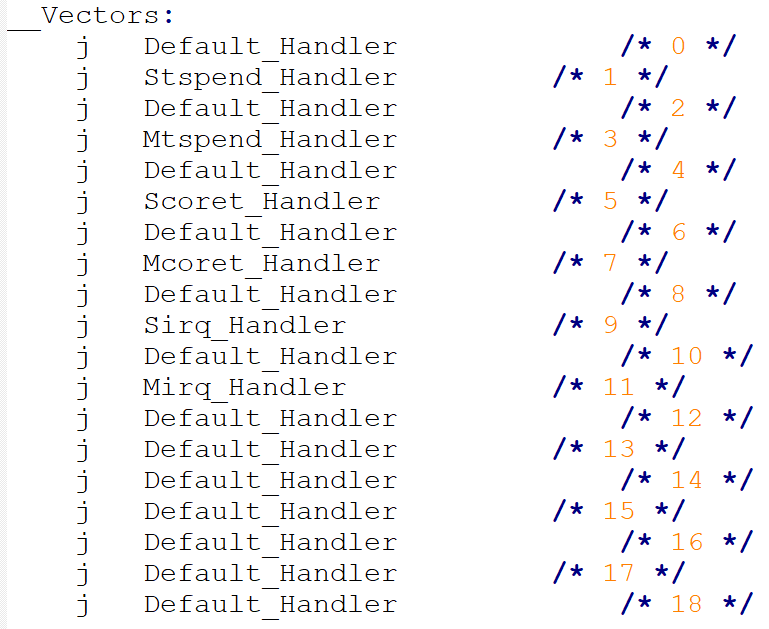

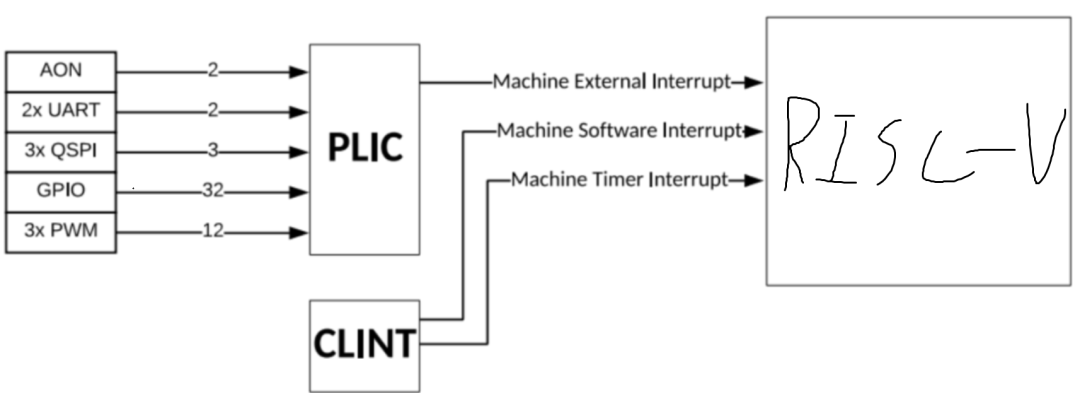

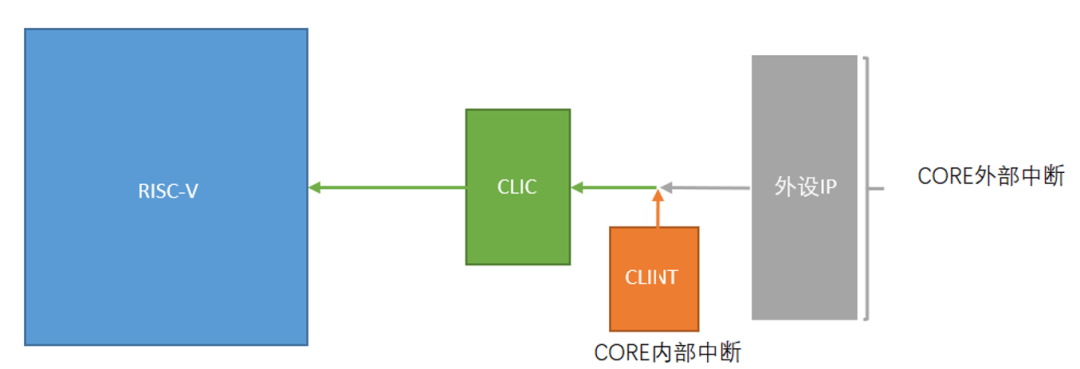

其中0~15号中断编号也是RISC-V固定的,而15(有些可能更靠后,16/17)号以后的也是各家芯片设计公司自己定义的一套中断。一个比较有意思的是cortex-M的15号中断Sys tick和RISC-V的1/3号 S/Mtspend中断非常类似,都是core timer,通常用在RTOS中的时间片调度。但是CLINT只能管理0~15号CPU core中断,而15号以后的还需要依赖另外一个中断控制器CLIC或PLIC(Platform ),如下图所示, CLINT管理的是CPU core中断,而PLIC(和GIC非常非常类似,支持多clustor,SMP)。比如某家芯片设计公司设计的SOC芯片使用的是RISC-V CPU,他们设计的SOC IP中断请求信号(UART,IIC,SPI,TIMER等)只能连在PLIC或者CLIC上,而不能连在CLINT上, 因为CLINT是core上的中断控制器。

总结:

通常使用RISC-V CPU的芯片设计公司在设计中低端芯片时,会使用CLINT+CLIC搭配方式,等价于ARM cortex-M系列的NVIC; 在设计中高芯片时,会使用CLINT+PLIC搭配方式,等价于ARM cortex-A系列的GIC;

关注公众号,加星标,回复1024获取学习资料,每天进步一点点。

声明:

本号原创、转载的文章、图片等版权归原作者所有,如有侵权,请联系删除。

关注、点赞、在看、转发,支持优质内容!

关注、点赞、在看、转发,支持优质内容!