群里有人问了一下电容贴电容的工艺是怎么弄的,我脑子里瞬间的记忆出来,确实好像是有这种工艺有在哪看过资料,但是什么要这样做就完全没印象,所以我最直接的疑问是,为什么会有这种做法,为什么要这样做?

群里有人问了一下电容贴电容的工艺是怎么弄的,我脑子里瞬间的记忆出来,确实好像是有这种工艺有在哪看过资料,但是什么要这样做就完全没印象,所以我最直接的疑问是,为什么会有这种做法,为什么要这样做?

首先能确定的,这个工艺方式肯定是非常非常不常见的方式,就算在手机行业里,好像也没有使用工艺吧(对电容),哪怕手机芯片堆叠这么常见普通,但电容的堆叠好像还是极其少见!

另一方面,这工艺确实也有在做,但能肯定的是99%的工艺人不一定接触过。

所以马上有个新疑问,那从搞电路设计角度来说,这种方式有没有可能是RD瞎搞的结果?

所谓的瞎搞,就是RD设计的时候,可能有什么问题,但发现这样焊接问题解决了,就会认为这样比较好,然后把这个工艺难题交给了工艺,让他们解决。然后,然后,这个技术出来了!(以上均为胡猜,勿喷 )

)

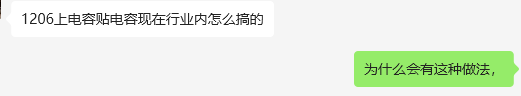

手机CPU和内存的堆叠工艺很好理解,因为设计空间有限,而且CPU本身面积大,如果能把2个芯片合二为一,那这个意义是非常巨大的,而且这样的连接可以让CPU和内存的连接距离更短,速率更高。

当然不管是不是真的是设计问题,但它事实 客观也让工艺能力技术更一步提升了,多高技术,好工艺都是因为各种奇葩要求逼迫提升起来

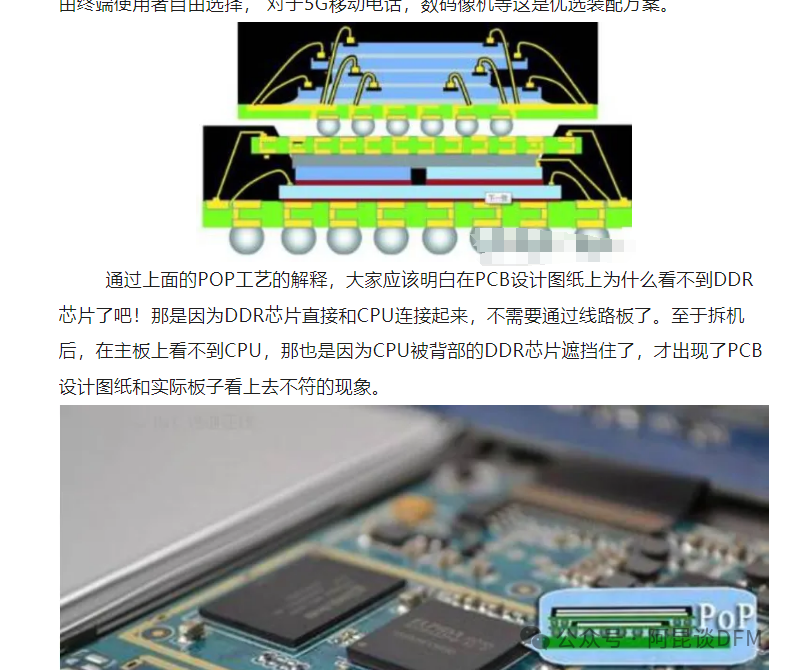

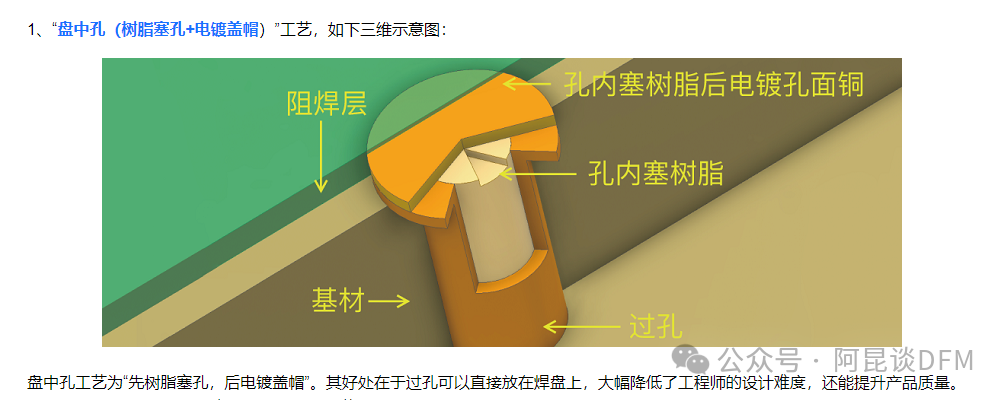

比如焊盘中的盘中孔设计,从正常工艺角度来说,焊盘上不能放孔,因为这样会吃锡引起虚焊问题,所以在早期DFM要求中是不允许的,但现在技术的提升,盘中孔的设计也非常成熟了,而且本身盘中孔的设计对于高密度产品来说也是非常现实的客观问题,就边立创都在大力推广盘中孔,还能免费打样了!这其这就是需求引起的技术提升!

但对于MLCC电容就有点难理解了,容量不够就用大容量,面积不够,再用小封装,总有一种合适 的方法对应,另外,什么样的电路会让电容落脚地方没有,把它逼上”梁山“。?

来吧,各位小伙伴,你们对于这种贴片电容堆叠工艺应用了解吗,一起讨论一下?

什么情况下会这样来应用?