| ESD与Latch-up | 数字中后端课程 |

| DFT设计与实现(理论) | DFT设计与实现(实践) |

本周三于旧金山举行的高盛技术会议上,英伟达 CEO 黄仁勋向观众表示,台积电在应对英伟达需求方面展现出了“令人难以置信的灵活性和能力”,但他补充道,“如果有必要,当然,我们也可以选择其他供应商。”

虽然黄仁勋没有明确指出,但是其他供应商应该指的就是全球第二大代工厂三星电子。即使现在黄仁勋想更换到三星,分析下来可能性也是很小。

去年,三星代工厂获得了英伟达 8 纳米工艺芯片的订单,例如用于汽车的 Tegra 芯片以及 2020 年推出的 RTX-3000 图形处理单元(GPU)。然而,今年三星并未能成功获得英伟达更先进的 AI 处理器订单,例如 H 系列或 Blackwell 芯片,这些芯片需要更先进的制造工艺。而三星的先进工艺目前良率依然太低!

三星引入3nm GAA 纳米技术始于 2022 年,当时三星表示已启动其尖端制造工艺的量产,与该公司的 5nm 节点相比,它将带来一波性能和效率优势。市场消息指出,三星积极提升3纳米良率,用尽解决方案使3纳米不陷入困境。报告显示,尽管“拼了老命”付出许多努力,三星3纳米GAA良率仍比量产水平低三倍。

据韩国时报报道,三星第一季3纳米GAA良率仅个位数,虽然有提升,但不幸的韩国分析师指出,三星须将良率提高到60%才能量产,才能让高通等客户对此制程有信心。

韩国时报的一篇报道提到,三星的 3nm GAA 良率在 2024 年第一季度为个位数。慢慢地,该公司成功地取得了进展,将这一数字提高到20%。不幸的是,虽然这是一个进步,但韩国分析师估计,三星必须将这一数字提高到 60% 才能开始大规模生产,因为其前客户(如高通)将开始表现出信心。

低良率不仅导致晶圆价格变贵,还会增加客户拿到正常芯片的时间,故台积电为何是客户首选。三星2纳米GAA也进展不佳,另一份报告提到,良率低至10%~20%。

此外由于三星良率不佳,市场传出美国德州泰勒厂撤出部分人员,以削减成本。路透社报道,可能是三星裁员计划的一部分,重新考虑晶圆代工策略和先进制程路线,故延后泰勒厂量产时间并撤出员工。

美国政府据《芯片与科学法案》最高提供64亿美元补助,以及其他优惠贷款,但三星要取得这笔款项恐怕有困难,因三星晶圆厂必须投产后才能拿到补助,这条件不太可能马上满足。

三星泰勒厂预定为生产SF4以下制程基地,包括SF3(第二代3纳米)和SF3P(正式名称为SF2)。但良率不如预期,特别是 SF3 / SF3P 良率过低,三星必须重新评估泰勒厂生产计划。一份新报告称,该公司已被迫从其设施中撤出人员,目前只留骨干员工。

三星代工良率低已流传多年,特别先进制程,使三星SF3E(第一代3纳米)仅生产挖矿芯片,未获其他客户青睐。三星仍称之为后继产品,SF3 和 SF3P 用于数据中心和智能手机处理器。

三星努力寻找解决方案因应挫折。事实证明,3纳米GAA制程如果达量产良率,有利英伟达等公司,因客户有更多选择生产AI芯片。遗憾的是,良率若无法提高,客户很难下单,AI 芯片代工商机还得被台积电牢牢把握。

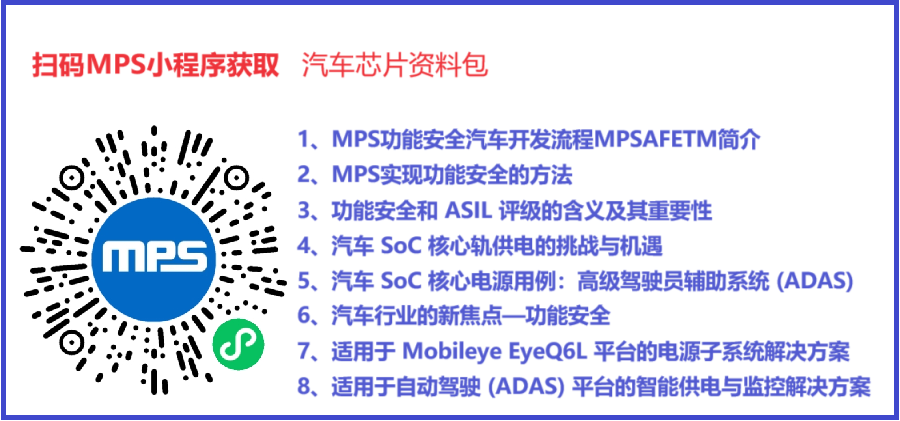

扫码获取!

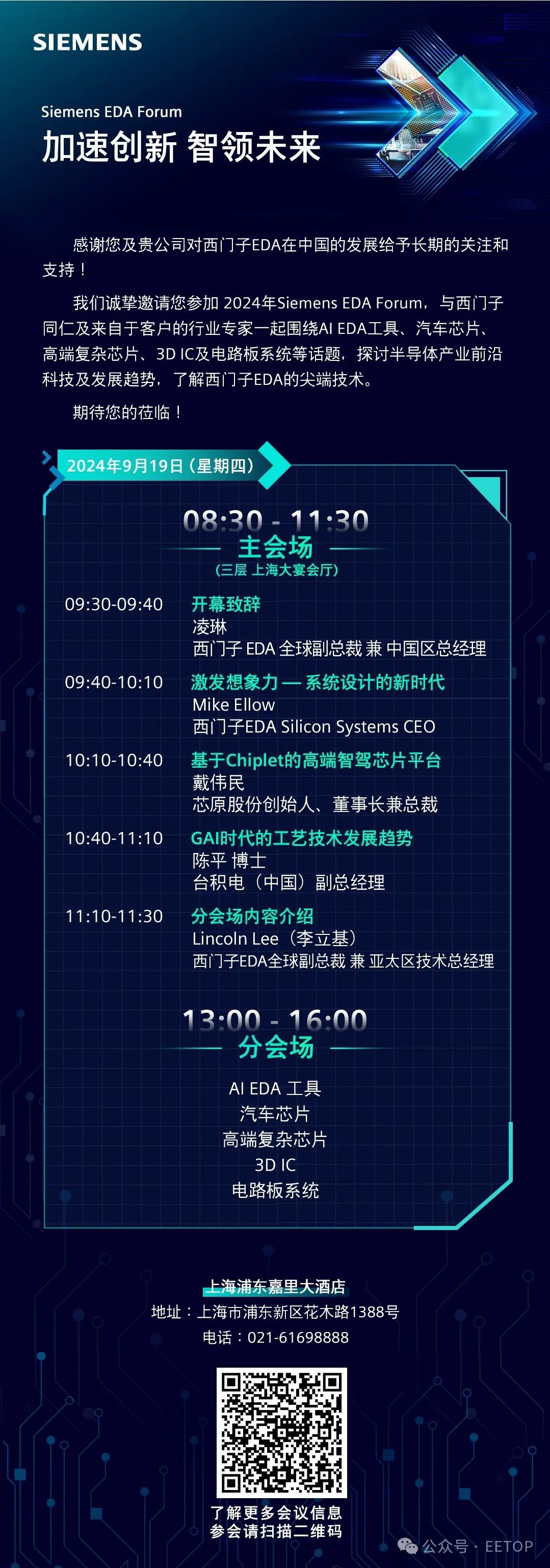

EDA大会邀请函(扫码报名参会 免费)

报名倒计时7天!