前言

在《AUTOSAR-MCAL--SPI模块详解(一),AUTOSAR-MCAL--SPI模块详解(二),AUTOSAR-MCAL--SPI模块详解(三)》三文中详细介绍了AUTOSAR MCAL SPI模块的概念,且介绍了Renesas RH850 U2A-16芯片的SPI模块,但是没有介绍如何配置MCAL SPI模块。本文再次介绍Infineon TC3xx芯片QSPI模块,同时介绍MCAP SPI的配置。希望大家能搞清楚以下问题:

1.如何配SPI时钟

2.如何配置SPI外部连接Pin脚

3.如何配置SPI中断

4.如何配置SPI时序

5.如何计算SPI波特率

6.如何理解和设计Sequence, Job, Channel

7.如何理解EB和IB

目录

注意:本文内容比较多,如果只是先快速使用TC3xx QSPI模块的朋友可以直接阅读第1和第4,5章节,遇到不理解的概念再去查阅2,3章节。

缩略词

简写 | 全称 |

SPI | Serial Peripheral Interface |

BPI | Bus Peripheral Interface |

FPI | Flexible Peripheral Interconnect (Bus protocol) |

参考文献:

1. SPI详解

2. 英飞凌TC3XX MCAL QSPI实操指南 (qq.com)

注:本文章引用了一些第三方工具和文档,若有侵权,请联系作者删除!

正文

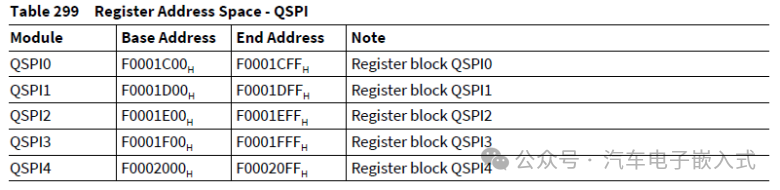

TC37x芯片总共有5个SPI Unit/Module, SPI用作Master SPI时,SPI 0可以通过片最多选挂载14个Slave SPI.

注意:TC3xx芯片一个Master SPI最多可以挂载16个Slave SPI.

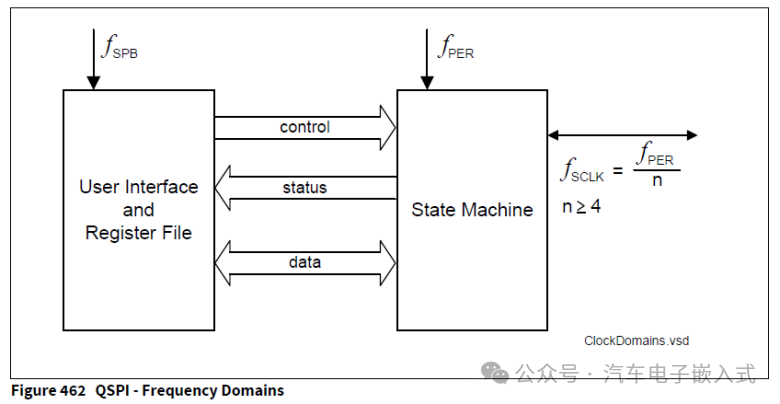

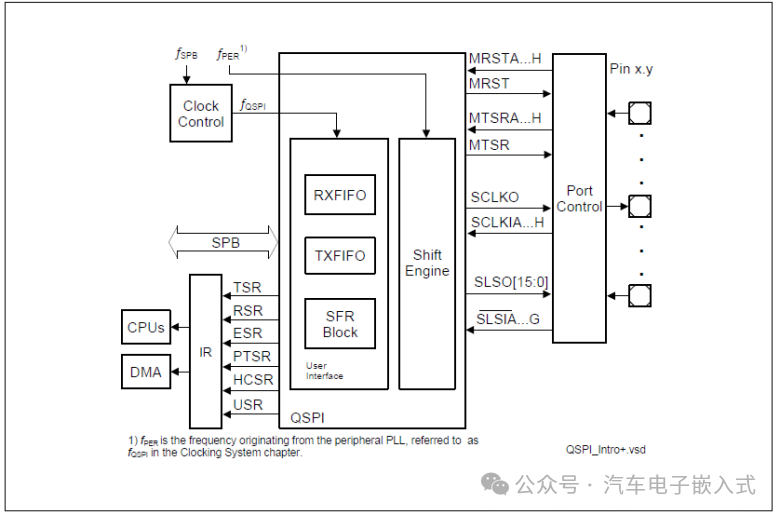

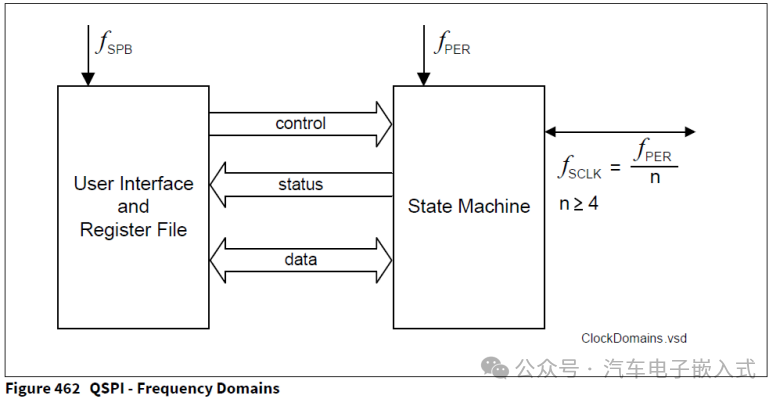

SPI模块需要两个时钟驱动,fSPB和fPER, fPER也就是SPI章节中提到的fQSPI.

fSPB主要用来驱动SPI的User Interface相关的操作。

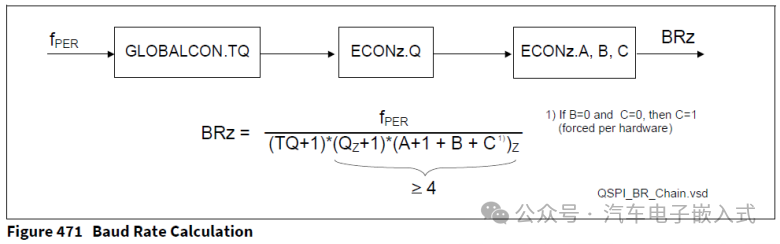

波特率由fPER频率除以等于或大于4的整数确定。

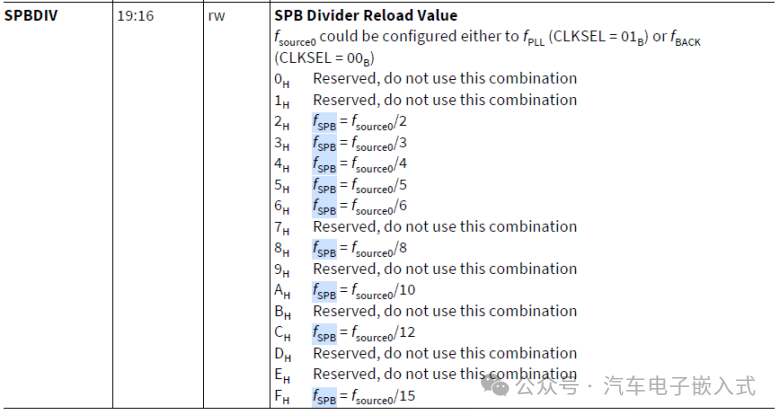

fSPB和fPER都由时钟模块的CCU(Clock Control Unit)分频/倍频后提供。CCUCON0. SPBDIV来配置fSPB

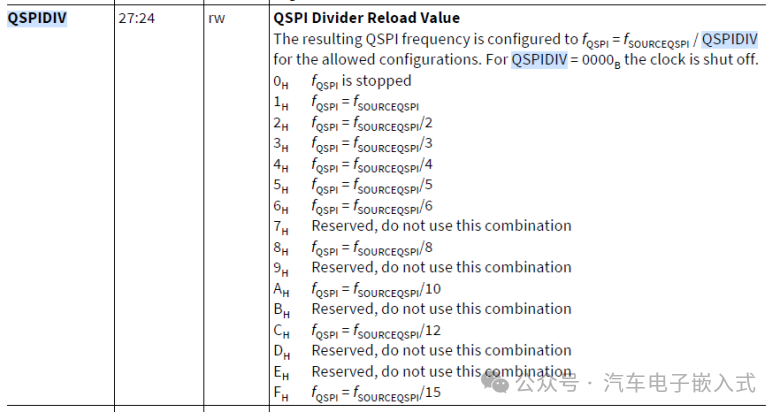

CCUCON1. QSPIDIV来配置fQSPI也就是fPER

具体如何从外部晶振一步一步配置产生fSPB和fPER可以参考《TC3xx芯片Clock System功能详解-时钟分配CCU》一文。

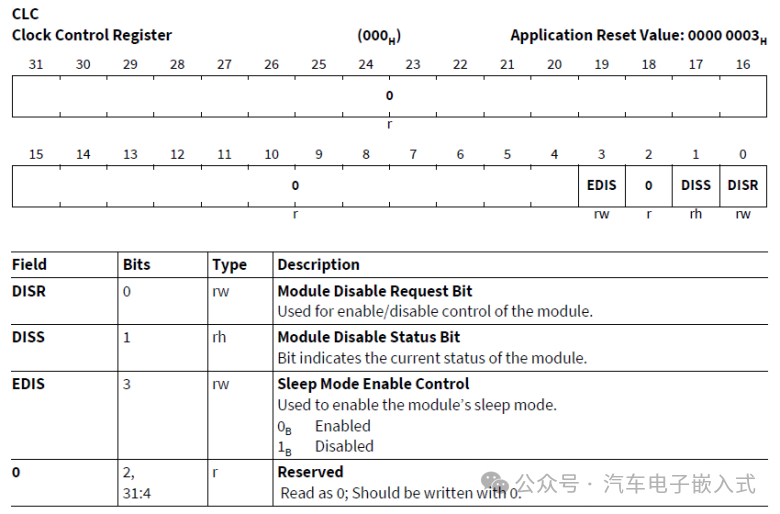

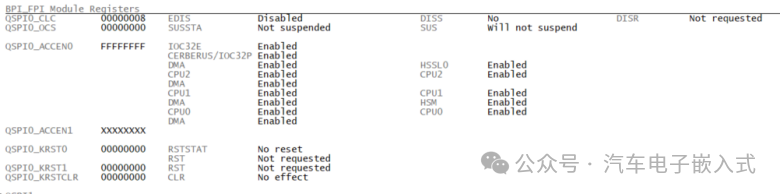

时钟控制寄存器CLC允许user根据应用程序的要求调整模块的功能和功耗。当模块内核连接到CLC时钟控制接口时,CLC控制模块的f<>模块时钟信号、睡眠模式和禁用模式。

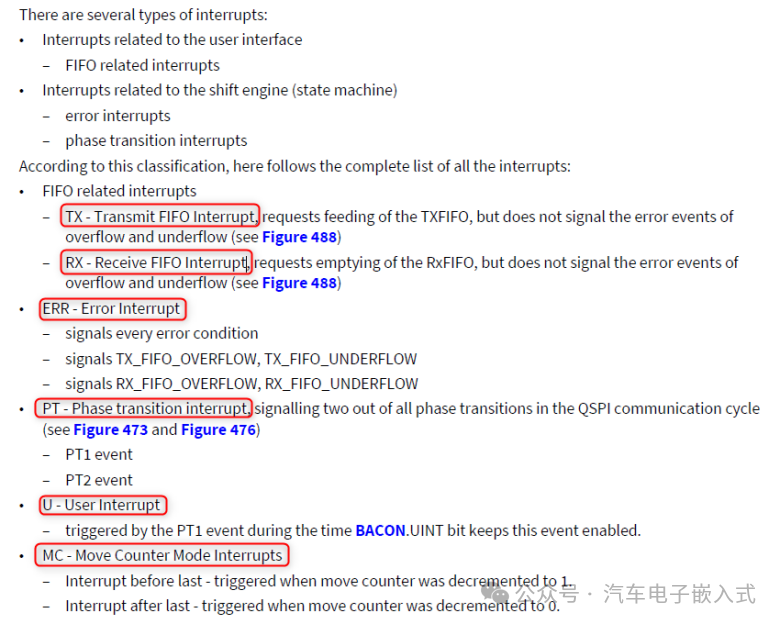

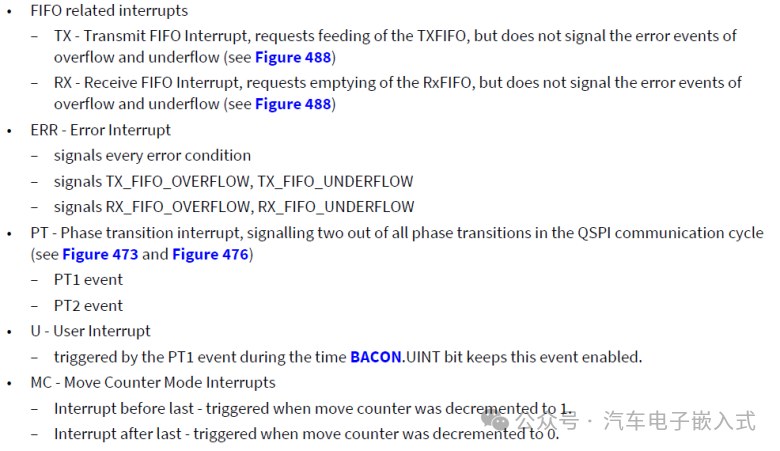

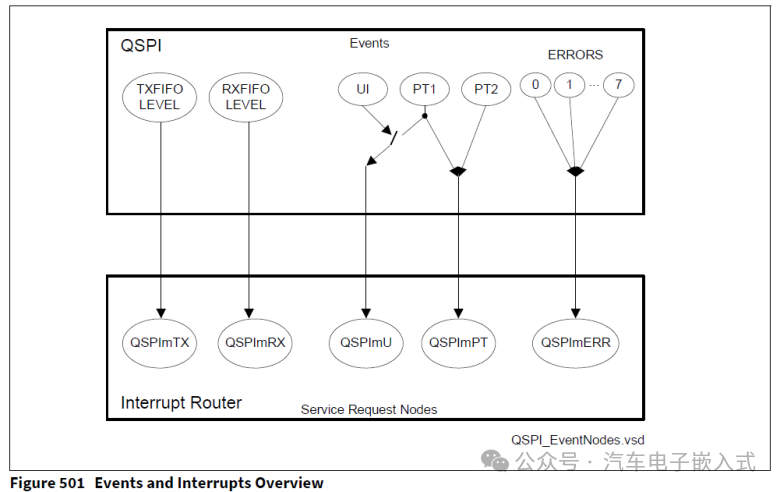

每个SPI Unit/Module可产生以下6个中断,Tx -Transmit FIFO interrupt, Rx-Receive FIFO Interrupt, ERR- Error Interrupt, PT-Phase transition interrupt, U-User Interrupt, MC-Move Counter Mode Interrupt.

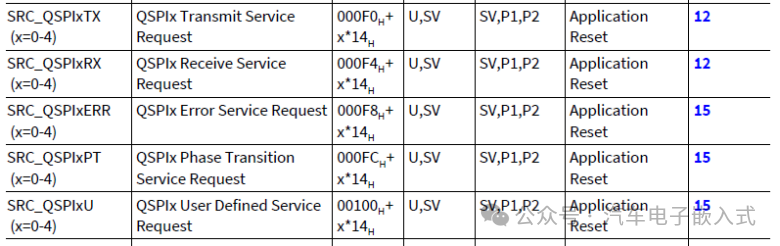

在Autosar OS上配置SPI ISR的interrupt Source时参考以下公式。

注意:TC37x芯片手册的IR模块没有提供MC-Move Counter Mode Interrupts的中断Sources计算公式,是TC37x不知此MC-Move Counter Mode Interrupt吗?

每个中断的产生机制看后文的模块功能介绍。

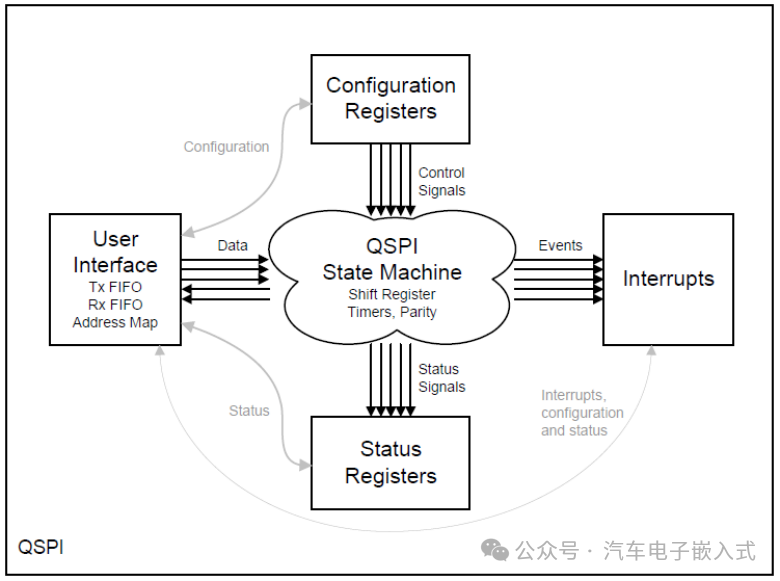

用户通过User Interface可以配置SPI模块的配寄存器(比如和SPI时序相关的配置参数.eg.),同时也可以往SPI模块的Tx FIFO写数据以及从Rx FIFO读数据。SPI模块的QSPI State Machine拿到数据后根据配置寄存器中的配置参数按配置格式(时序,大小端.eg.)将数据发送到SPI总线上(MOSI),在收发数据的时候会更新SPI状态到状态寄存器,也会产生中断中断到IR模块。

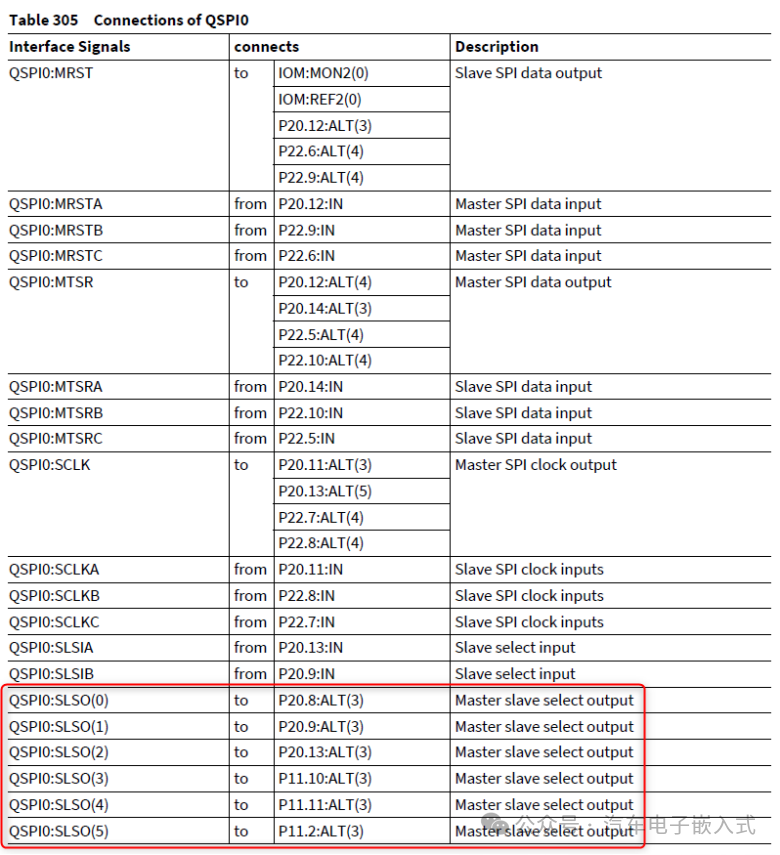

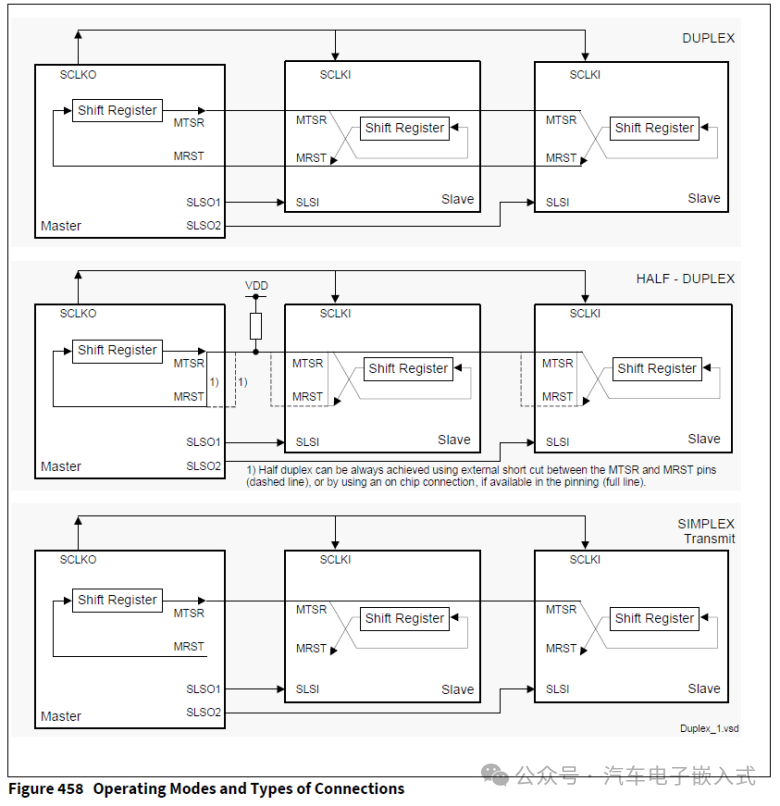

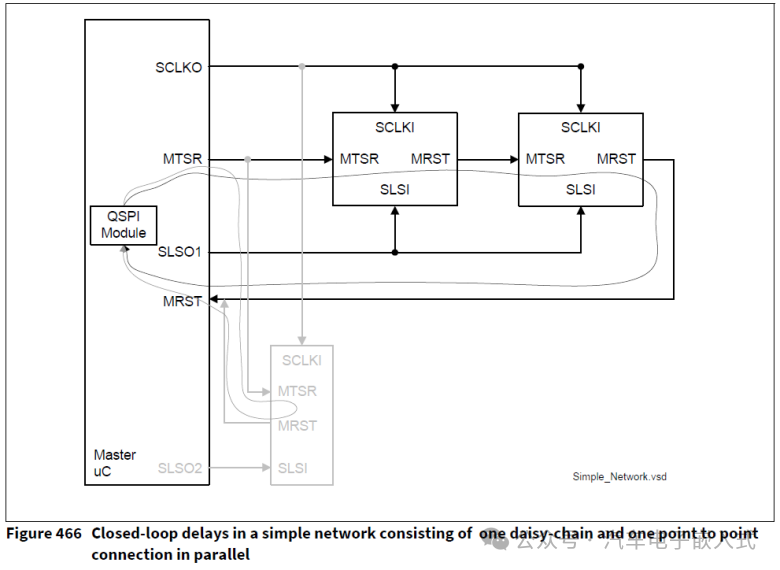

两个SPI设备通过以下4个信号线进行连接通信:

. 串行时钟线 SCLK

. 主设备输出,从设备输入数据线MTSR(Master Transmit Slave Reveive)

. 主设备接收,从设备输出数据线MRST(Master Reveive Slave Transmit)

. 片选从设备线(SLS)

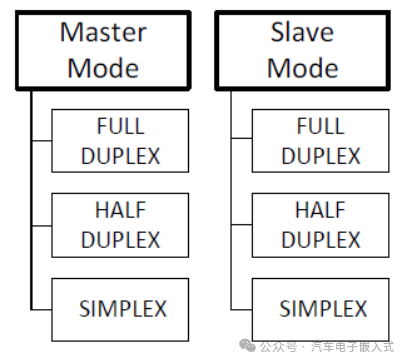

TC3xx芯片的SPI模块支持Master Mode和Slave Mode配置,每种Mode下又支持全双工,半双工,单工模式。

下图为下又支持全双工,半双工,单工模式信号线连接。

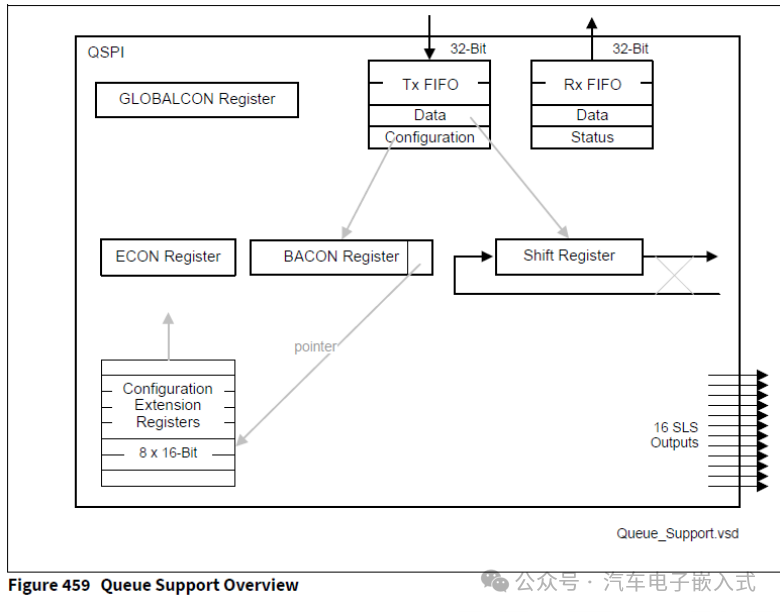

TC3xx芯片的SPI模块叫做QSPI, 也就是队列(Queue SPI),那该怎么理解这个Queue的含义了?

《AUTOSAR实战篇: 手把手带你搞定TC3XX芯片基于DMA的SPI实现 (qq.com)》一文中这么解释:TC3xx的SPI模块内部存在队列相关的硬件机制,该队列主要体现在能够最大限度的提高寄存器与数据的统一配置。

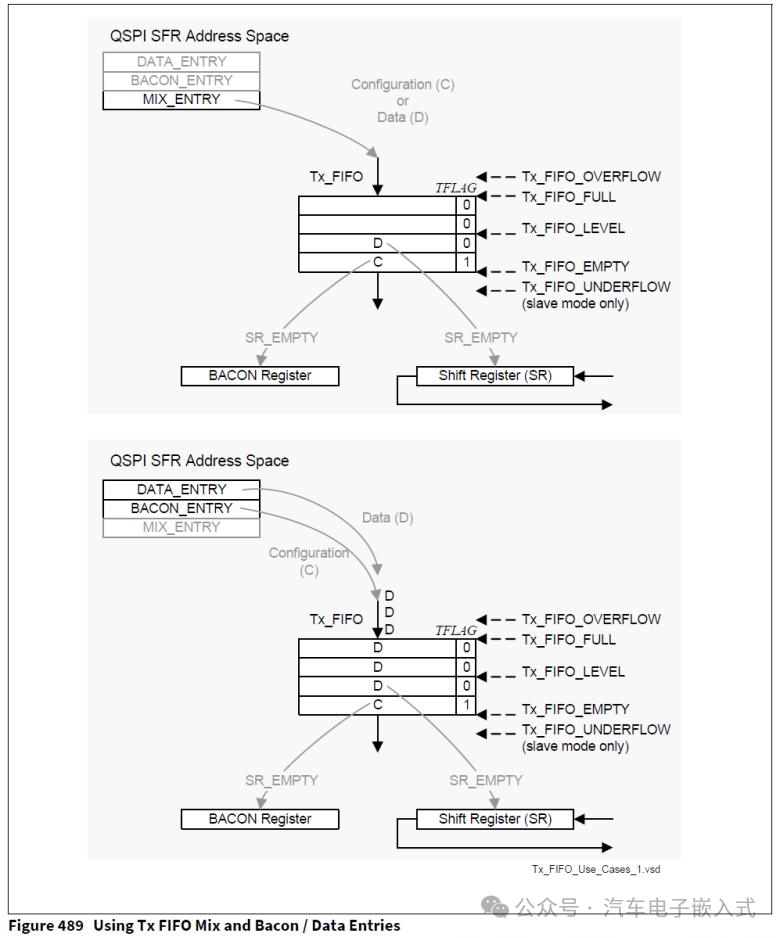

《英飞凌TC3XX MCAL QSPI实操指南 (qq.com)》一文中这么解释:QSPI中的Queue指的是一块通用的内存,其中包含两种数据,分别为配置数据和传输数据,配置数据就是寄存器的配置,传输数据就是实际要发送的数据。

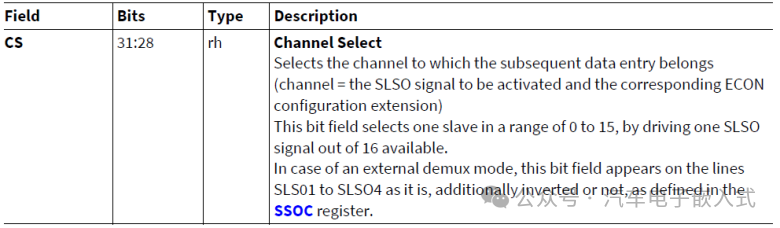

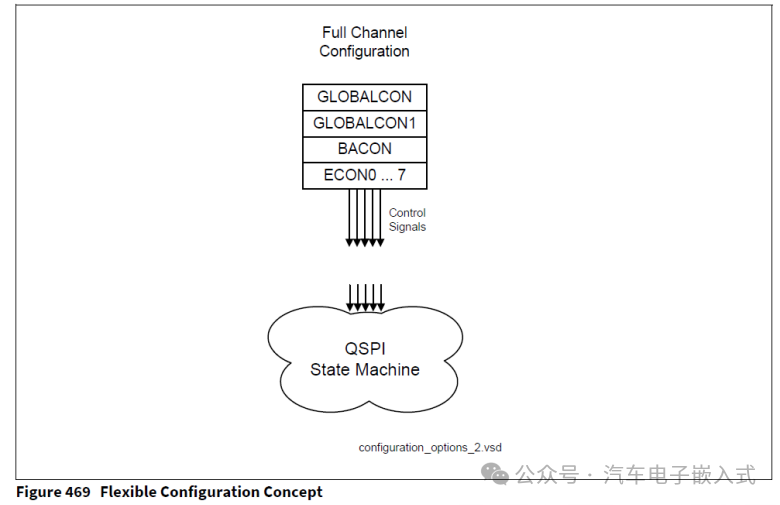

官方手册解释:队列机制使得片选信号激活后(CS线拉低),SPI帧的时序切换(两帧或多帧SPI报文的时序要求不一样)变得更加平滑舒展(comfortable)。用户铜鼓User Interface可以将配置和数据都带到TXFIFO,QSPI而已跟踪哪个TXFIFO条目是配置,哪些数据是配置。QSPI模块期望通过一次移动(例如DMA移动)将32个基本配置位从某个片上通用RAM移动到TXFIFO。来自TXFIFO的这32个配置位(BACON)和QSPI模块中包含的8个配置扩展寄存器ECONz(z=0-7)的配置位共同定义了模块的完整配置(见下图)。一个扩展寄存器用于两个从属选择:ECON0用于SLSO0和SLSO8,ECON1用于SLSO1和SLSO9…

个人理解:通过后文可以知道,QSPI给用户提供了所谓的DATA_ENTRY和8个BACON_ENTRY(也就是两类寄存器),用户往这两个寄存器中写配置或者数据时,QSPI的硬件机制就会将用户写入到配置或者数据存放到QSPI的TXFIFO中(共有4个32bit的Queue Items),这个时候Queue就不为空,QSPI的硬件机制就会将配置数据写入到BACON寄存器中,将DATA放到Shift Register中开始数据发送,而发送数据的配置信息(时序配置)就存在BACON寄存器和ECON寄存器中。如果两次数据的发送的时序不同,通过QSPI的Queue机制就能完成比较平滑的时序切换(比如TXFIFO中存放的内容为:BACON_0, DATA0, BACON_1, DATA1, 使用BACON_0的时序配置发送完DATA0后就能尽快且平滑的使用BACON_1的时序配置发送DATA1)。

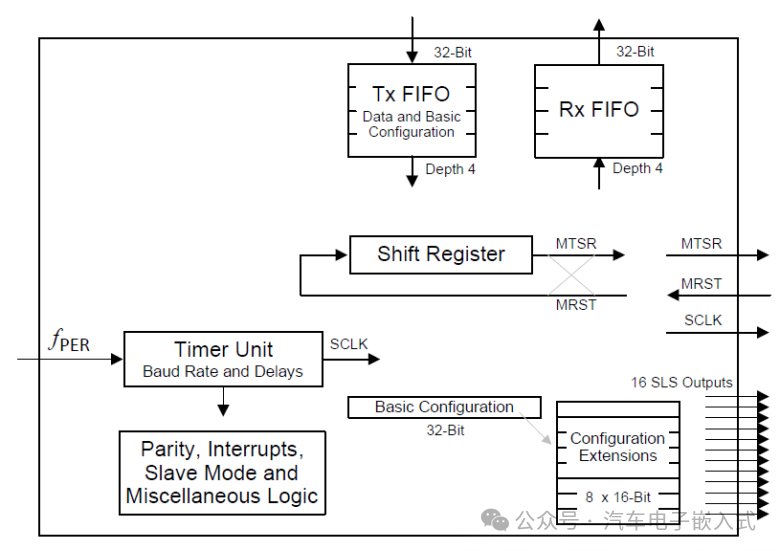

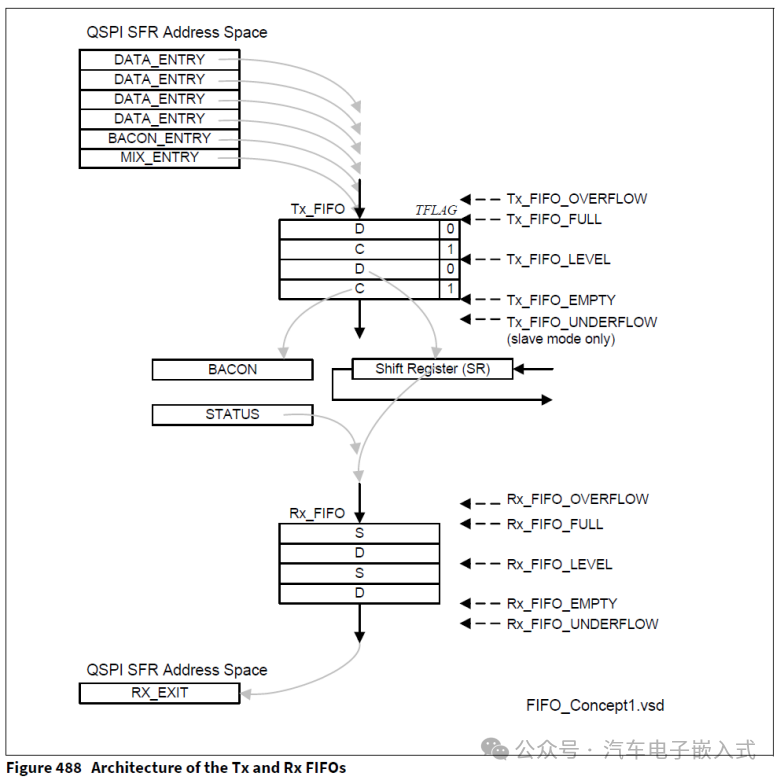

TxFIFO和RxFIFO提供用户接口。移位寄存器和“混杂逻辑” 块构建了模块的状态机。“配置扩展”块提供了配置QSPI帧的全面功能。

参考1.2章节

在主模式下,QSPI模块生成时序、串行时钟和从设备片选信号。

本节描述了配置QSPI通信相位长度的可能性:定时延迟、数据长度、占空比和数据采样。

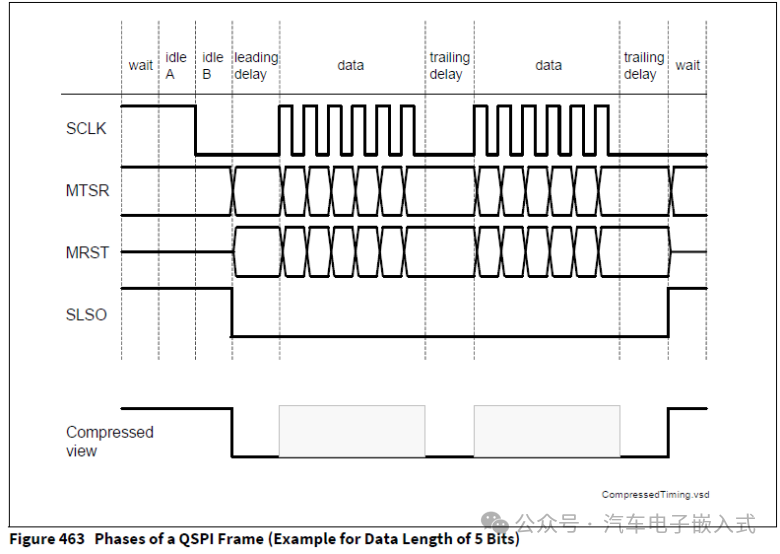

QSPI帧开始于激活从设备片选信号SLSO(从idle phase切换到leading delay phase的切换点),QSPI帧结束于Disable从设备片选信号SLSO(从trailing delay phase切换到wait phase或者idle phase)。这是一个由五个阶段组成的序列:空闲延迟idle delay、前导延迟leading delay、数据段Data phase、尾随延迟trailing delay和可选的等待阶段wait phase. 空闲阶段分为两个相等长度的阶段:idle A和idle B.

下图显示了QSPI帧及其相位的完整和压缩视图。全视图显示了QSPI连接所需的所有四个信号。压缩视图以适合讨论其属性的方式在单行中表示相位。

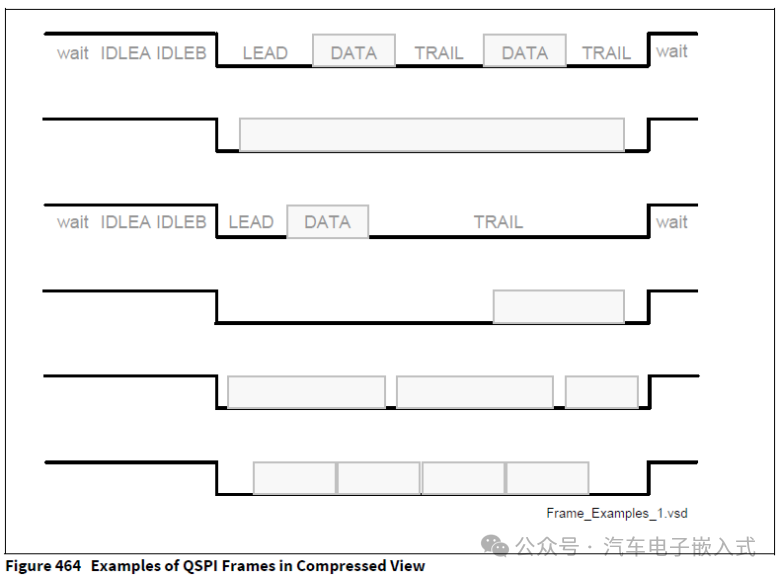

QSPI的灵活时序控制允许在非常宽的时间范围内以足够的精度对每个相位进行编程。下图显示了压缩视图中具有不同相位长度的QSPI帧的一些示例。

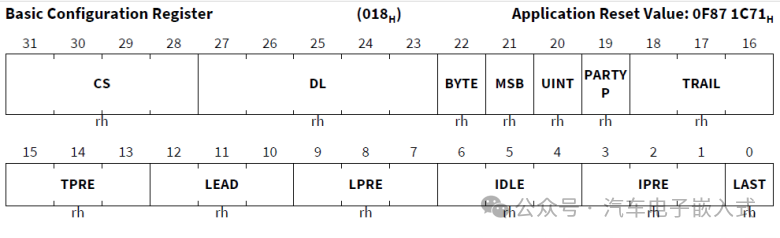

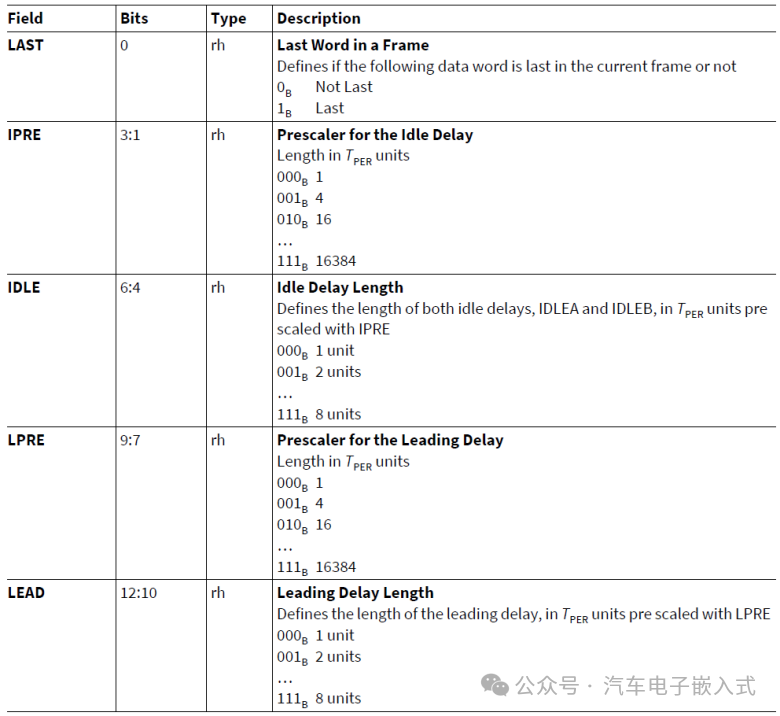

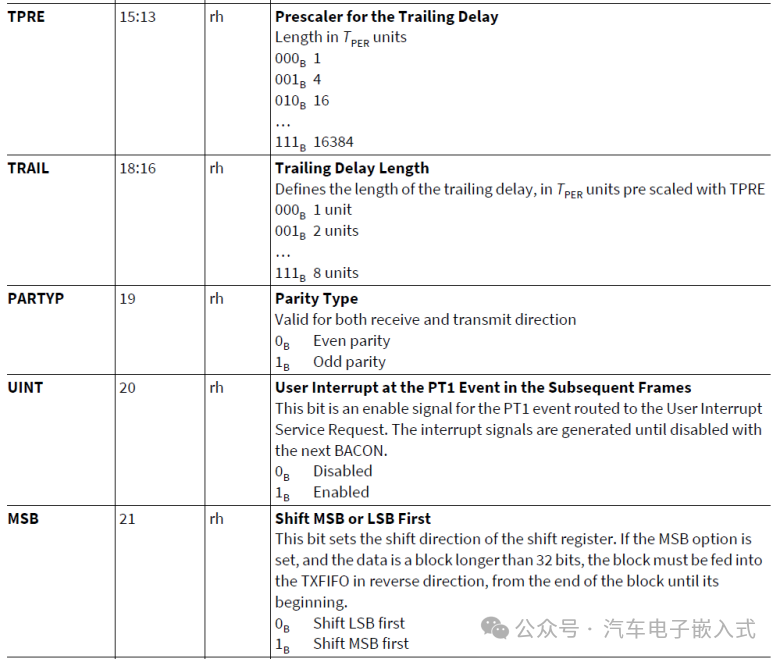

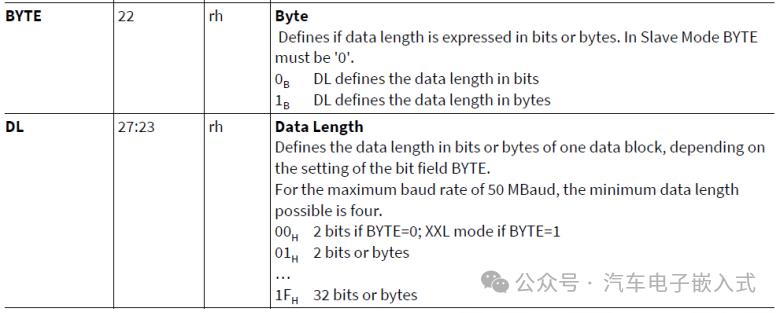

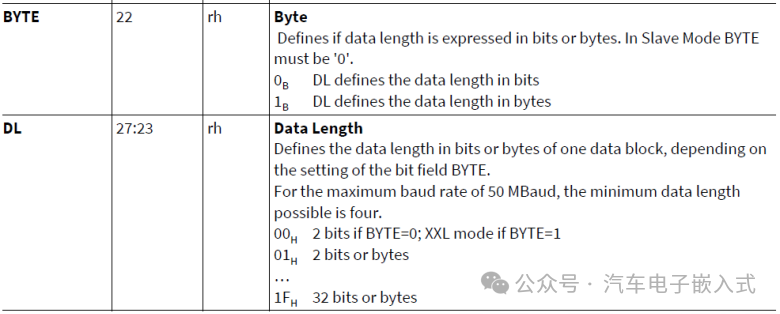

使用寄存器BACON中的相应位域对相位长度进行编程。有四个主要的位域定义了以tQ为单位的相位长度,还有几个修饰符位字段定义其范围和粒度:

. IDLE

. LEAD

. DATA

. TRAIL

WAIT Phase只是一个等待写入Tx FIFO的循环,没有预定义的持续时间,因此没有定义的bit field.

IDLE位字段定义了长度相同的IDLEA和IDLEB的两个子相位。在它们之间的转换处,设置/改变下一个从属设备的串行时钟信号的极性。

此外,灵活的时序控制允许对串行时钟的占空比和采样点属性进行编程。考虑到时钟不对称和环路延迟,这允许在一定程度上提高可实现的波特率。

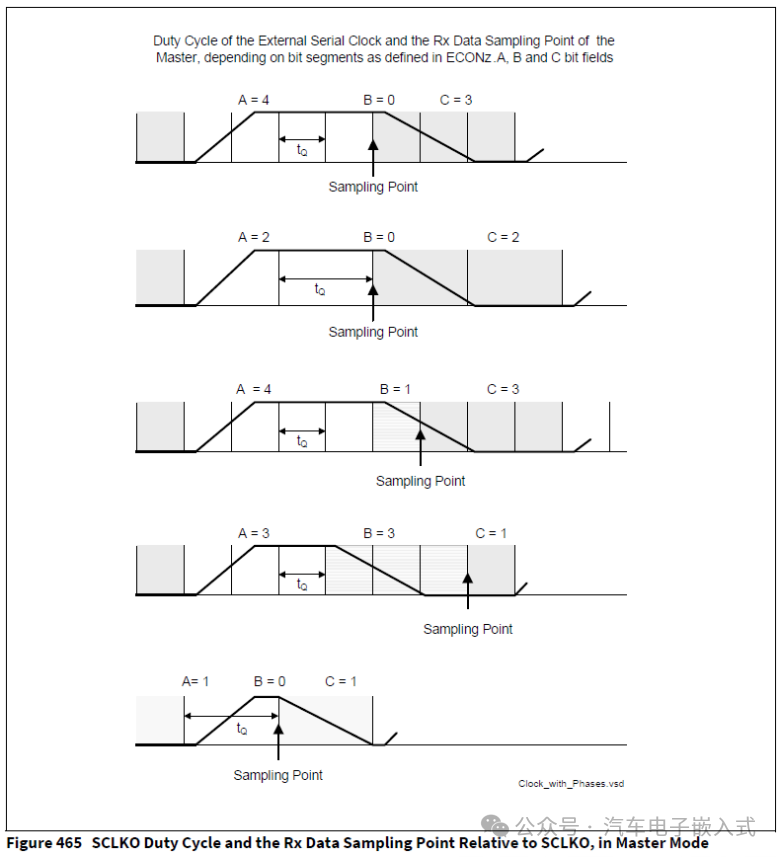

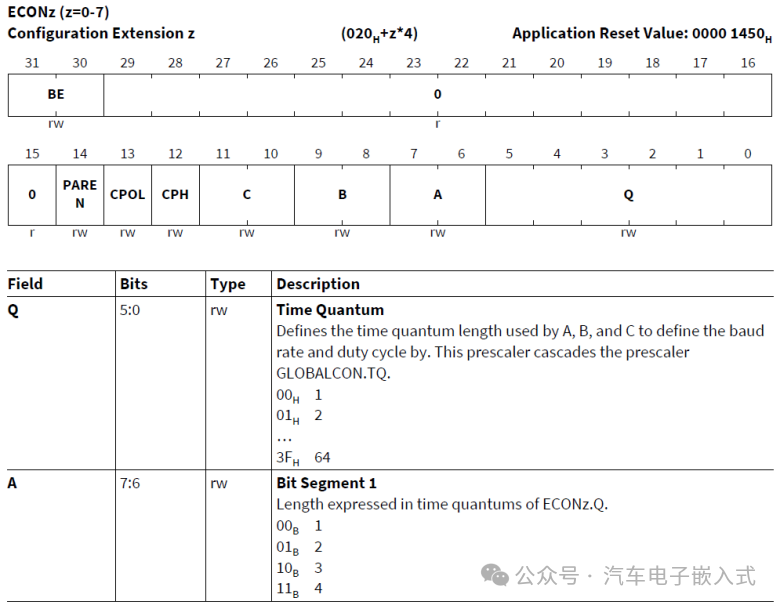

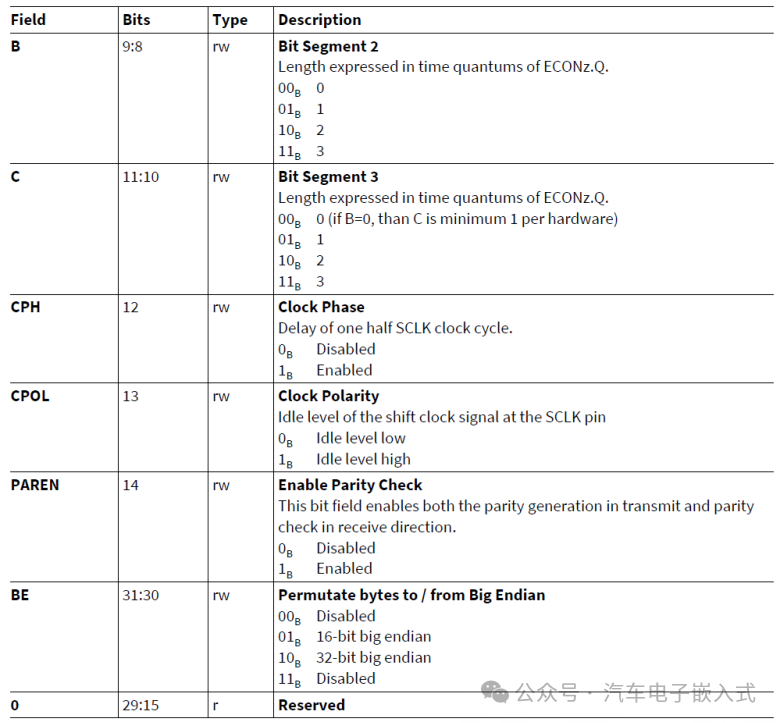

ECONz(z=0-7)位字段A、B和C定义了相应位段的长度。采样点始终位于相位B和C之间的过渡处,时钟占空比由相位A和B+C定义。

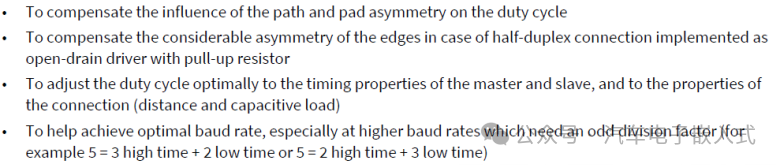

占空比控制的目的:

采样点控制的目的是允许以尽可能高的波特率可靠地接收从设备传输的数据。

在Master设备接收方向上,Slave设备传输的数据相对于串行时钟的shift edge到达主设备的时间要晚得多。这是由循环延迟引起的,包括:

. 移位时钟沿从主时钟到从时钟的传播延迟

. 从设备的响应延迟

. 数据从从设备到主设备的传播延迟

最后但并非最不重要的一点是,灵活的时序控制允许配置移位时钟的相位和极性。

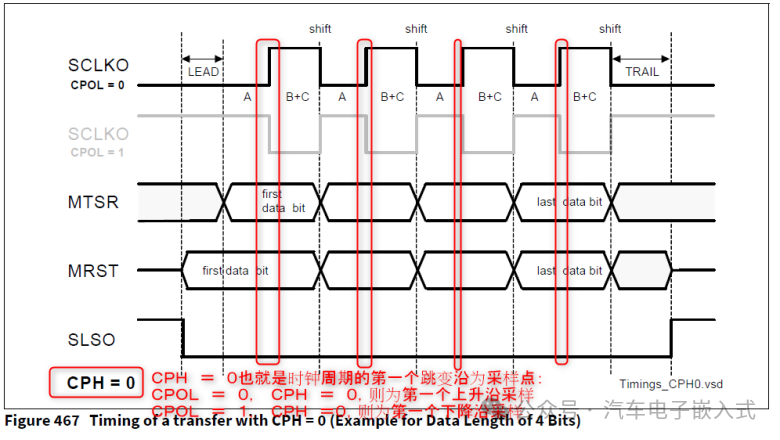

时钟极性由位字段ECONz(z=0-7). CPOL配置。此位字段将时钟空闲极性设置为低或高。

时钟相位由位字段ECONz(z=0-7).CPH配置。该位字段将初始时钟延迟设置为0或位段A,如位字段ECONz(z=0-7). A所定义。

CPOL和CPH设置控制主模式。从模式的时序固定为CPOL=0和CPH=1,这些值必须在BACON.CS指向的ECONz(z=0-7)寄存器中编程(programmed)。ECONz(z=0-7).A, B和C在从模式下不影响采样点,采样位于SCLKI的下降沿。

下图显示了时钟相位CPH=0的QSPI时序。

当与从属设备通信时如果使用ECONz(z=0-7).CPH=0,则该从属设备在用SLS信号选择后立即传递第一位的有效值。在这种情况下,帧中的第一个时钟边沿用于锁存第一个比特。第二个边沿传递第二个比特值,以此类推。帧中的最后一个边沿传递一个无所谓值的比特。

Trailing delay在数据块的最后一个移位时钟周期之后开始,随后是片选信号SLSO拉高,或者是连续模式下的新数据块。

注意:如果CPH=0,则片选信号SLSO拉低和串行时钟SCLKO的第一边沿之间的总延迟为LEAD+ECONz(z=0-7).A.

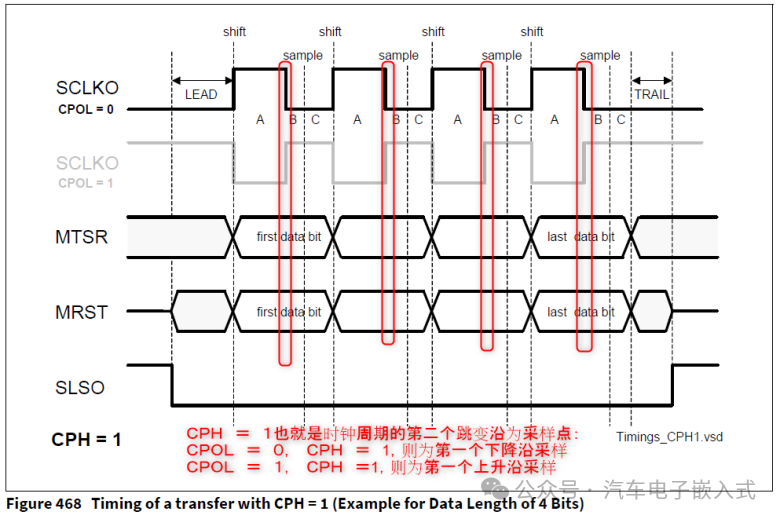

下图显示了时钟相位CPH=1的QSPI时序。

ECONz(z=0-7). CPH=1用于与从属设备通信,该从属设备在用片选SLSO信号选择后立即传递具有随机或无关紧要值的比特。在这种情况下,从属设备使用帧中的第一个时钟沿来移出第一个有效数据位。第二个时钟沿锁存该位值,依此类推。帧中的最后一个时钟沿用于锁存最后一个有效的数据位,该数据位通常保持驱动状态,直到帧结束。

Leading delay持续在SLSO的有效边缘和第一移位时钟边缘之间。

注意:如果CPH=1,则SCLKO的最后一个边缘和片选信号SLSO最后拉高之间的总延迟为TRAIL+ECONz(z=0-7).B+ECONz(z=0-7).C

本节描述了配置QSPI通信相位的可能性:时序延迟timing delay、数据长度、范围和粒度ranges and granularity.

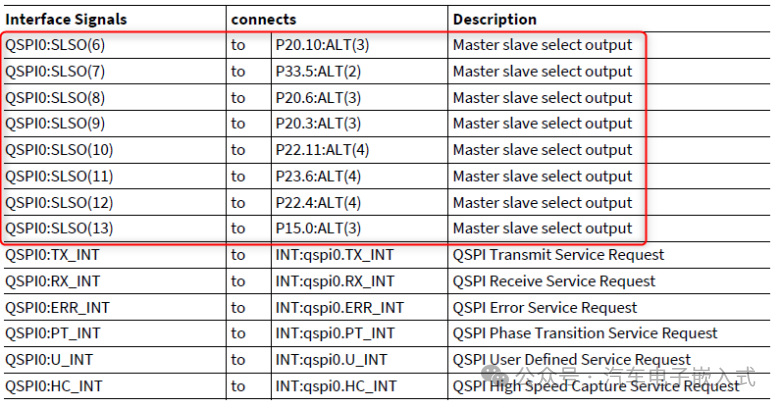

QSPI模块控制16个可单独编程的通信通道。每个通道都与一个片选信号以及相应的时序及其他属性(波特率、延迟、数据宽度、奇偶校验等)相关联。

QSPI模块的16个从属选择通道被细分为两组,每组8个:

. 通道0到7

. 通道8到15,通道8和通道0共用一个ECONz(0-7)的配置,通道9和通道1共用一个配置,以此类推。

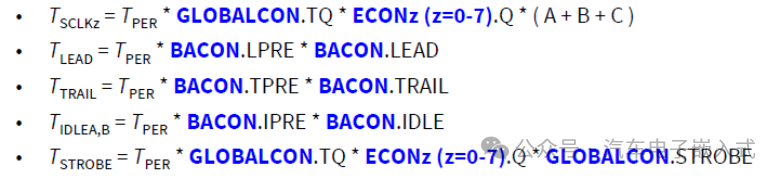

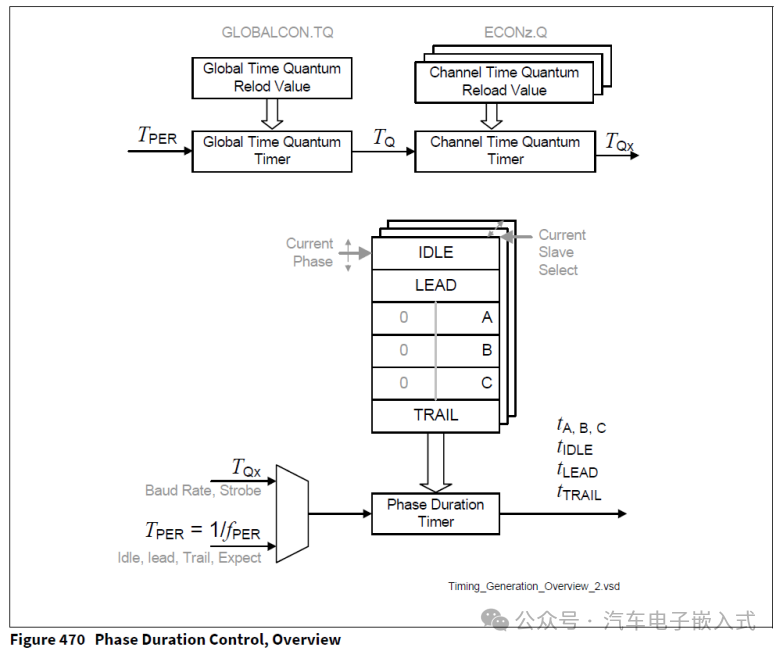

QSPI Phase对应于定义简单状态和循环序列的简单状态机的状态。由于通信周期的严格顺序性,一个定时器足以定义每个Phase的长度。每个Phase的长度以时间量(Time Quanta, TQ)定义,时间量的长度由时间量计时器定义。每个QSPI从设备信道都有自己的时间量长度,基于模块时间量长度:TPER时钟周期->一个模块时间量->一个信道时间量

每个QSPI模块生成一个模块时间量,该时间量进一步缩小到信道量。这会影响延迟和波特率。假设pad strength setting、电容性负载和相应的QSPI网络布局属性不允许连接到一个模块的不同从设备的波特率存在极端差异。它们都有相似的速度范围:高速、中速或低速。混合非常高速和非常低速的从属设备没有多大意义。许多从属设备在时钟和数据输出上产生高累积电容性负载,这会影响所有从属设备的可能波特率。通过改变每个信道中的比特段相位,一个模块的从属设备的波特率可以在6:1的范围内变化。每个从属设备额外的两位计数器允许额外缩放1、2、4或8,使一个模块中通道之间的总比特时间变化达到48:1。

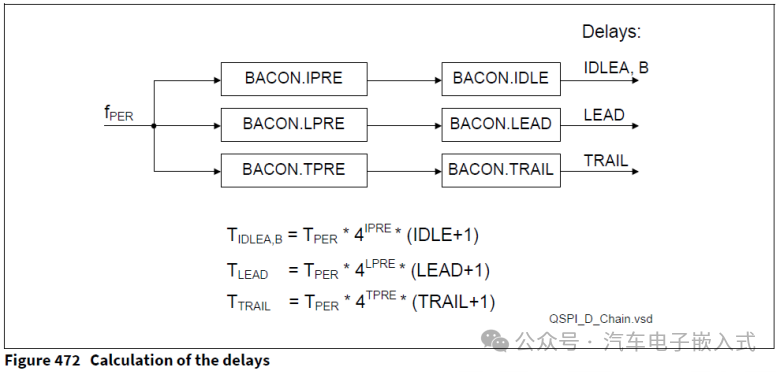

根据TPER=1/fPER,每个QSPI从属选择通道都有自己的相位长度集:

信道的波特率生成链从一个通用的TQ分频器开始。专用Q和A、B、C分频器使用由此产生的全局时间量来生成每个信道的波特率(从属选择)。

注意:必须满足以下条件:(Q+1)*(A+1+B+C)>=4。或者,另一种表述方式是:比特长度必须至少为4*TQ.

活动信道(从属选择)的每个延迟都有一个单独且独立的分频器链,从四次幂的预分频器和一个n分频器开始。

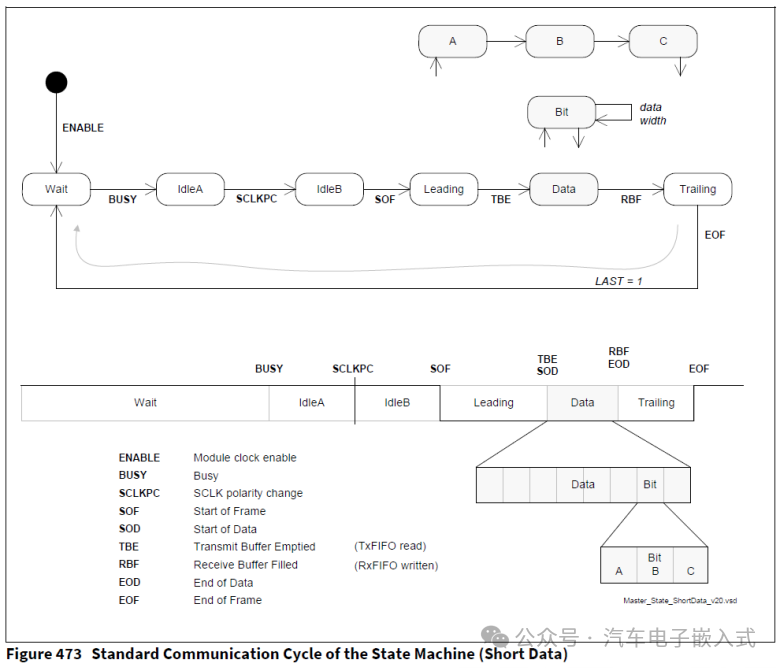

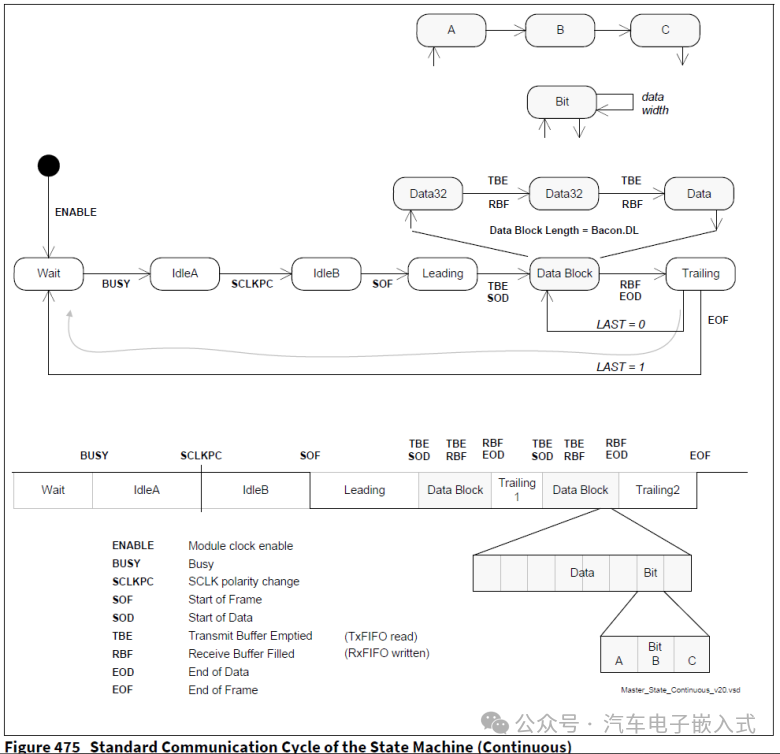

下图以分层方式显示了QSPI状态机的标准通信周期的俯视图。“数据”状态由几个“位”状态的循环组成,其中重复次数由数据宽度位字段定义。每个“位”状态都由一个简单的“a”、“B”和“C”状态序列组成。

仅当位BACON.LAST=1时,才执行包含所有阶段的完整(或标准)通信循环,从激活从属选择开始,到停用为止。否则,从属选择将保持活动状态,模块将等待更多FIFO数据条目。

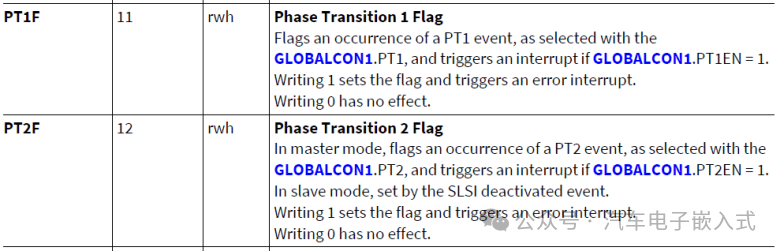

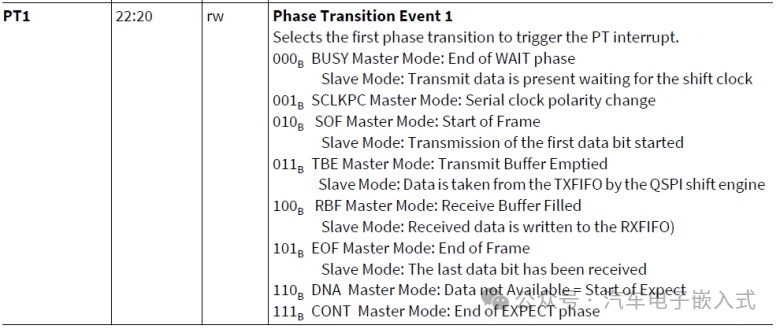

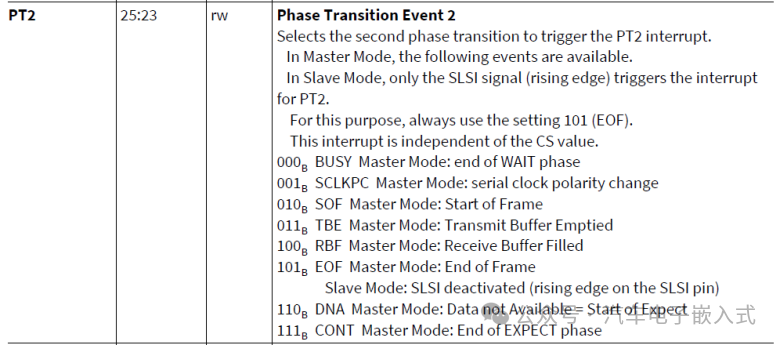

在Master模式下,相变中断事件PTI1和PTI2,每个信号都表示一个相变,如下图所示。事件通过STATUS.PT1F和STATUS.PT2F标记。GLOBALCON1.PT1和GLOBALCON1.PT2的值决定了哪些转换会导致事件。如果GLOBALCON1.PT1EN和GLOBALCON1.PT2EN设置为1,这些事件也会导致中断。通过FLAGSCLEAR寄存器的编程清除事件标志。

上图中的“数据块”是指短数据或长数据块。在连续模式下连接数据块时,每个块可以根据其BACON配置独立配置为短或长。

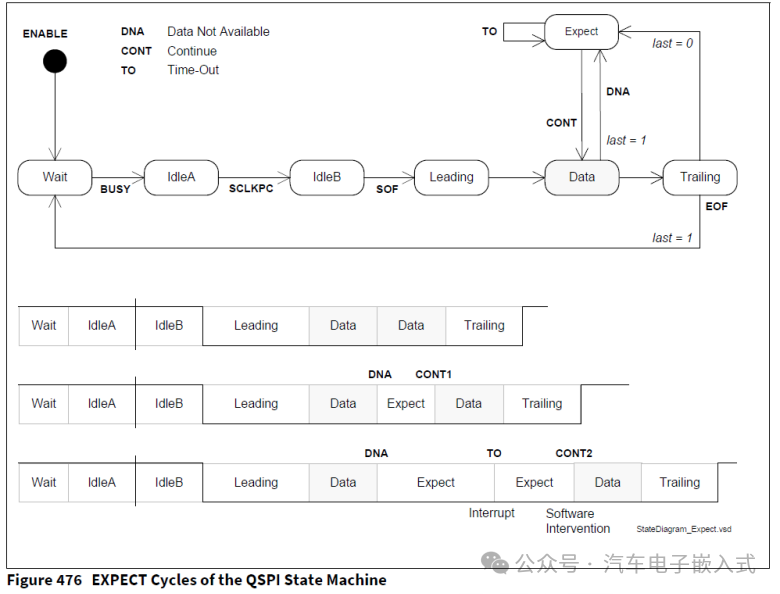

下图显示了QSPI状态机图中的EXPECT状态。这种状态可以在长数据模式和连续模式下进入,其中一帧由多个TXFIFO条目组成。其目的是监控FPI总线上的延迟。在这种情况下,根据BACON.DL,在一个FIFO条目被移出后,模块预计会有更多比特被移出DL,超时计数开始。如果预期的FIFO条目没有及时到来,则会发生超时。

如果在当前数据状态结束时,FIFO中已经有新数据可用,则EXPECT状态的持续时间为零。

如果在允许的时间窗口内的任何时间将下一个数据写入TXFIFO,则EXPECT状态的持续时间可以在零和编程上限之间的任何地方。在这种情况下,当前帧继续,SLSO信号保持有效。

如果数据没有及时到来,则EXPECT状态的持续时间恰好是最大的。然后,当前帧停止,但SLSO未停用。引发TO(超时)中断。状态机在循环中继续EXPECT状态,等待软件干预,在每个预期时间间隔后生成中断信号。

TC3xx的MCAL只支持Master Mode, 且主芯片(MCU)一般都用作Master节点,Slave Mode这里就不作介绍,感兴趣的可以自己去研究下。

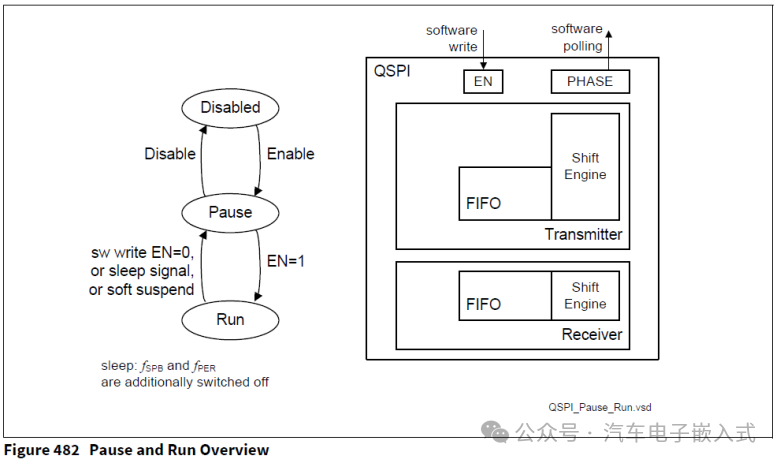

如果QSPI模块收到关闭时钟或暂停模块的请求,它将禁用所有服务请求。

QSPI模块提供了两种关闭时钟或暂停模块的选项:硬暂停(尽快考虑中断请求脉冲的长度)和软暂停(达到预定义状态后转换为暂停状态)。这些请求可以通过硬件信号(禁用、挂起、睡眠)或通过软件写入GLOBALCON. EN位来触发。

Disable, Pause and Run

通过清除CLC.DISR位,QSPI进入暂停状态。在这种状态下,可以初始化QSPI模块,预填充TXFIFO,然后通过设置GLOBALCON.EN位,进入RUN状态。

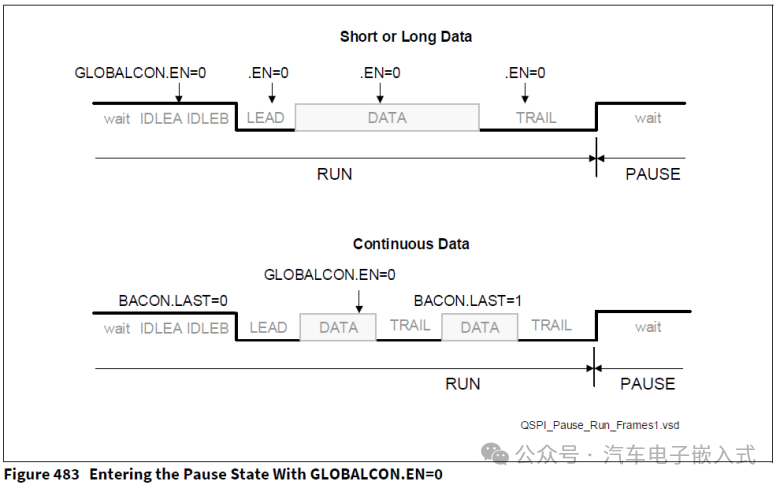

软件通过清除GLOBALCON. EN位请求运行模块的PAUSE状态。软件可以通过轮询GLOBALCON. EN=0且STATUS. PHASE=0来检测QSPI模块是否已达到暂停状态。(表示等待状态,仅主模式)。

在PAUSE状态下,模块的User Interface处于活动状态。寄存器和FIFO可以读写。然而,无论是在主模式还是从模式下,接收和发送状态机都处于非活动状态。这允许在不影响串行总线的情况下重新配置模块。

PAUSE状态的概念被重新用于处理软件OCDS挂起和睡眠请求。与主动暂停状态和OCDS暂停相比,睡眠状态具有特殊属性,即(由于低功耗要求)FPI和QSPI时钟都关闭。

如果正在运行的模块收到暂停请求,它将等待帧的最后一个TRAIL阶段结束。对于所有模式(短、长和连续),暂停状态由GLOBALCON. EN=0和STATUS.PHASE=0指示,仅主模式。

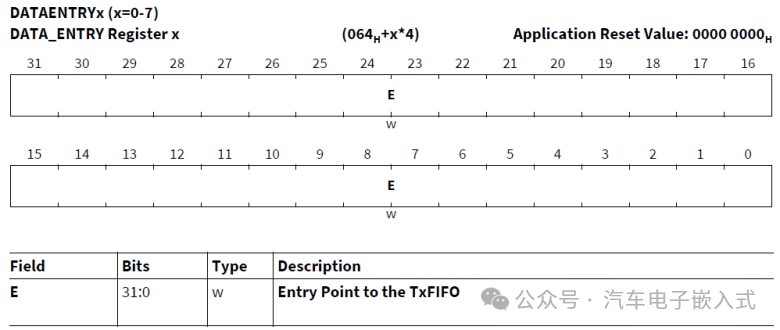

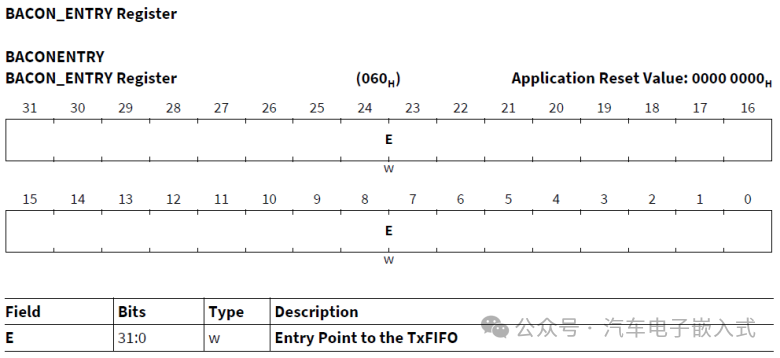

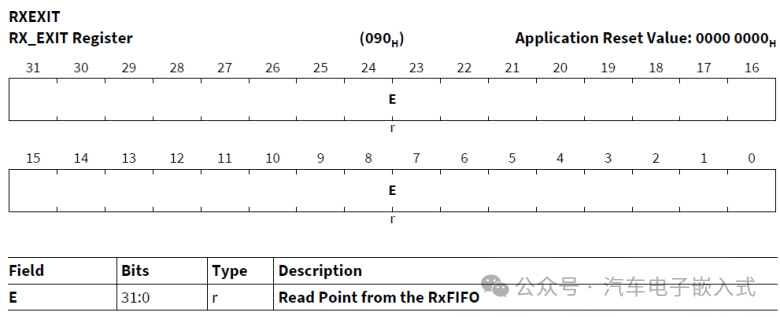

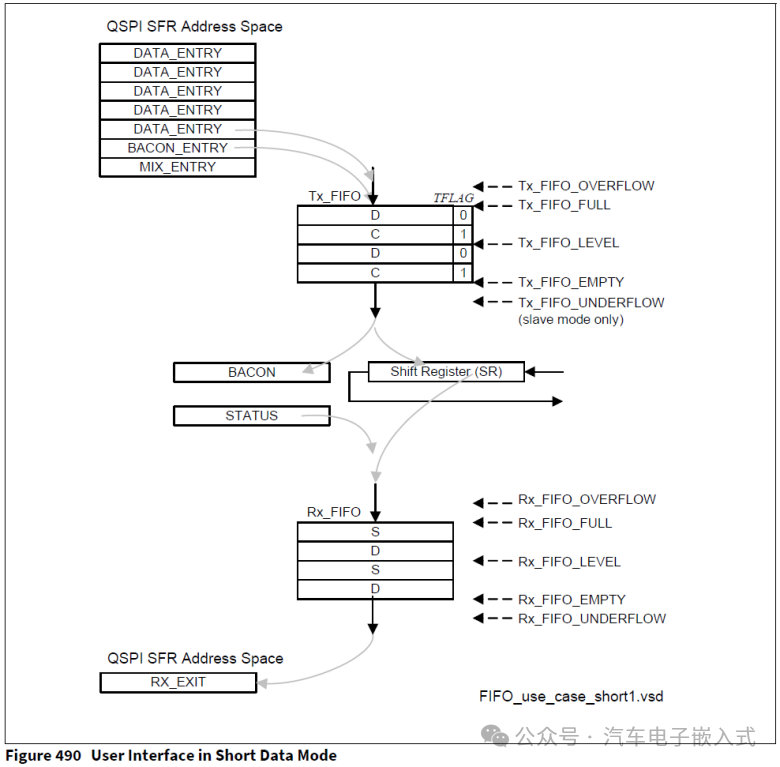

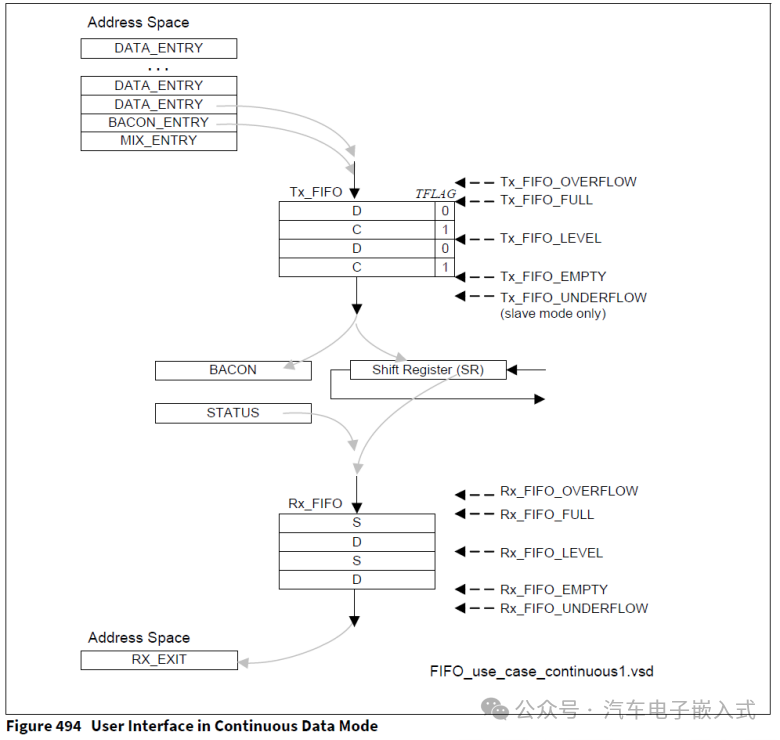

本节描述了使用发送和接收FIFO在片上RAM存储器和QSPI模块之间传输数据的可能性。QSPI具有一个4 x 32位Tx FIFO和一个4×32位Rx FIFO. 用于向Tx FIFO写入数据和配置以及从Rx FIFO读取数据和状态的地址范围由具有特殊属性的地址位置组成:

. Tx FIFO

– DATA_ENTRY - writes to any of these eight functionally identical locations are always interpreted as data

– BACON_ENTRY - writes to this location are always interpreted as configuration

– MIX_ENTRY - writes to this location are interpreted as data or configuration, based on a set of rules

. Rx FIFO

– RX_EXIT - reads from this location deliver either datum and optionally status, based on a set of rules.

使用MIX_ENTRY或DATA_ENTRY/BACON_ENTRY组合发送帧。不要将DATA_ENTRY/BACON_ENTRY和MIX_ENTRY组合在一起发送帧。

以下列表概述了QSPI的操作模式和TxFIFO条目地址的使用情况:

. Short Mode: MIX_ENTRY, DATA_ENTRY / BACON_ENTRY

. Long Mode: MIX_ENTRY, DATA_ENTRY / BACON_ENTRY

. Continuous Mode: MIX_ENTRY, DATA_ENTRY / BACON_ENTRY

. Single Configuration

Multiple Frames: MIX_ENTRY

. XXL Mode: DATA_ENTRY / BACON_ENTRY

. Move Counter Mode: DATA_ENTRY / BACON_ENTRY

DATA_ENTRY其实就是一个寄存器,用户往这个寄存器立马写数据,硬件就会将数据传递到QSPI的Tx FIFO中。

BACON_ENTRY其实也是一个寄存器,用户往这个寄存器立马写配置,硬件就会将配置传递到QSPI的Tx FIFO中,硬件会将配置数据写入到BACON寄存器,在发送数据的时候按照BACON中的配置时序参数来发送数据。

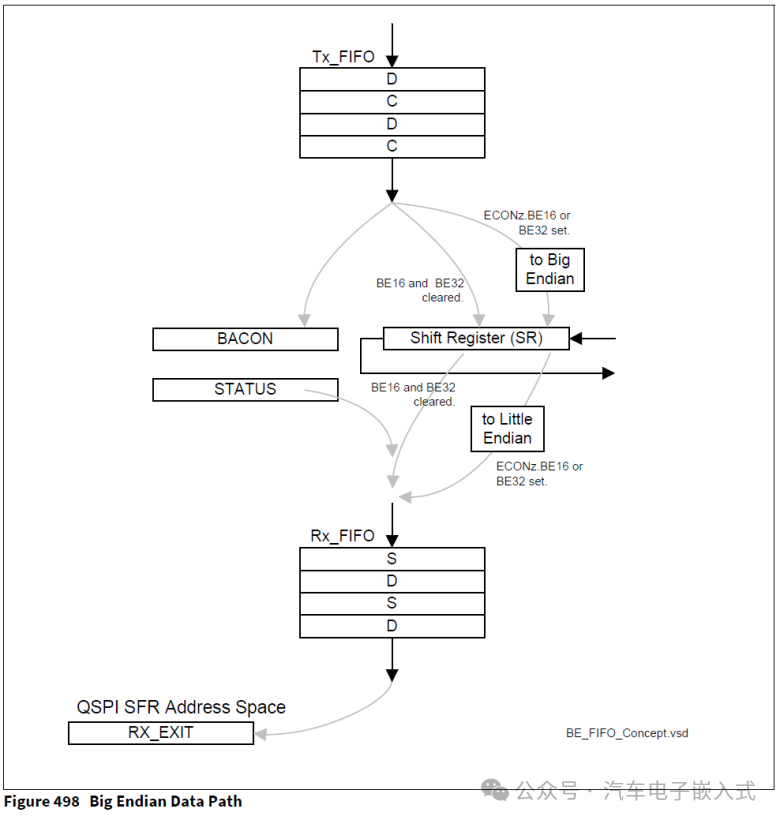

RX_EXIT也是一个寄存器,QSPI通过Shift Register发送数据后又会将Slave Device的数据保存到Shift Register中,硬件又会将Shift Register中的数据保存到Rx FIFO中,Rx FIFO中更新了接收数据后,硬件又会将Rx Data保存到Rx EXIT寄存器,用户可以通过读Rx EXIT寄存器得到Slave Device的数据。

Tx_FIFO中填充了配置和数据条目,这些条目被分发到Tx_FIFO出口处的BACON和移位寄存器。TxFIFO跟踪条目是配置还是数据。控制和数据元素自动分配到BACON和移位寄存器。如果没有可用数据,则新BACON处于挂起状态。

如果一帧结束,FIFO中有数据,则:

. 如果是short mode, 新帧以与前一帧相同的配置自动开始。

. 如果是long mode, 额外的数据被忽略。

TXFIFO错误条件:

. FPI总线往 Full的TXFIFO中写数据会产生溢出中断,写入数据被忽略。

. 在从模式下(GLOBALCON.MS=1X),在下溢的情况下,只传递“1”。

RXFIFO错误条件:

. 从空RXFIFO读取的FPI总线会产生下溢中断,并且只传递“1”位。

. 硬件尝试写入包含数据或状态的完整RXFIFO会产生溢出中断。RXFIFO会忽略写入尝试。

. 如果GLOBALCON.SRF位已设置,在主模式下FIFO满的情况下停止通信。在从模式下,该位被忽略,无法停止。

. 如果FPI总线频率非常低,波特率非常高,则可能会在移位寄存器和未满RXFIFO之间的途中丢失一些数据。在这种情况下,尽管RXFIFO未满,但会产生溢出中断。

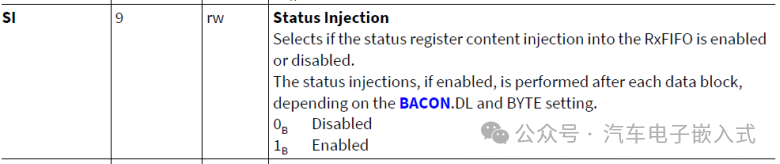

Rx_FIFO可以填充状态和接收到的数据条目,具体取决于GLOBALCON.SI

注意:如果对TXFIFO条目地址执行8位或16位写入,则数据将1:1映射到其在32位宽TXFIFO条目中的位置,其余部分用零填充。

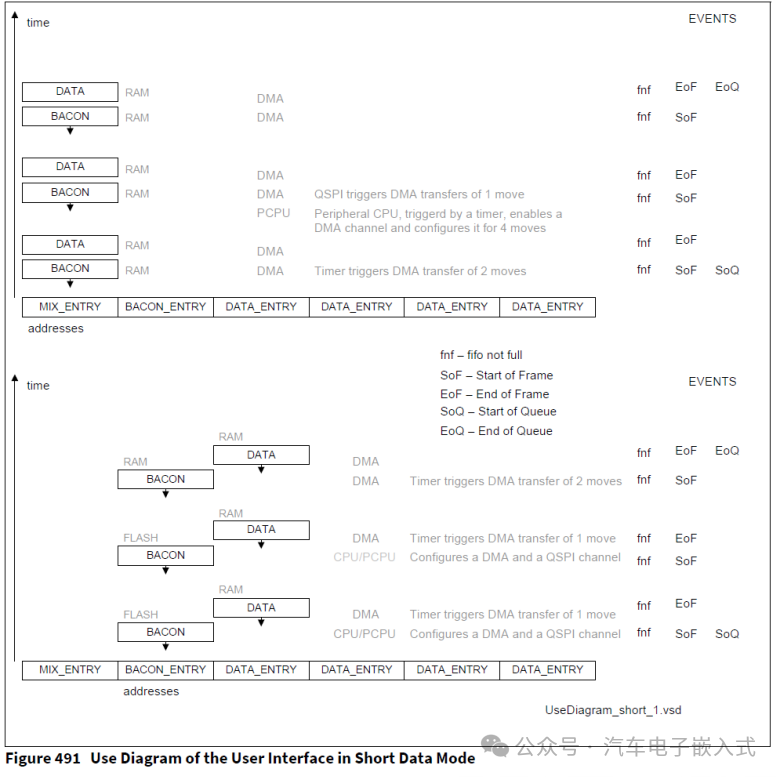

在短数据模式下,QSPI模块在一帧中传输长度为2至32位的单个数据。此模式由BACON.LAST=1且BACON.BYTE=0定义。

传输周期由以下阶段组成:W_I_L_D_T。符号“?”表示该阶段是可选的(允许持续时间为0)。

例如,Tx_FIFO事件可用于触发一次DMA传输(由两次32位移动组成),将BACON和DATA条目从片上RAM存储器传输到QSPI模块。

MCAL代码仅支持Continuous Data Mode, Long Data Mode暂不介绍,感兴趣的自己去研究。

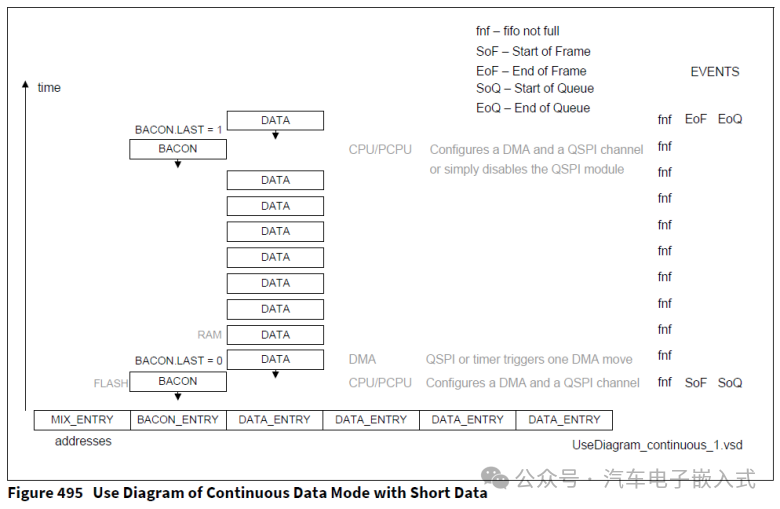

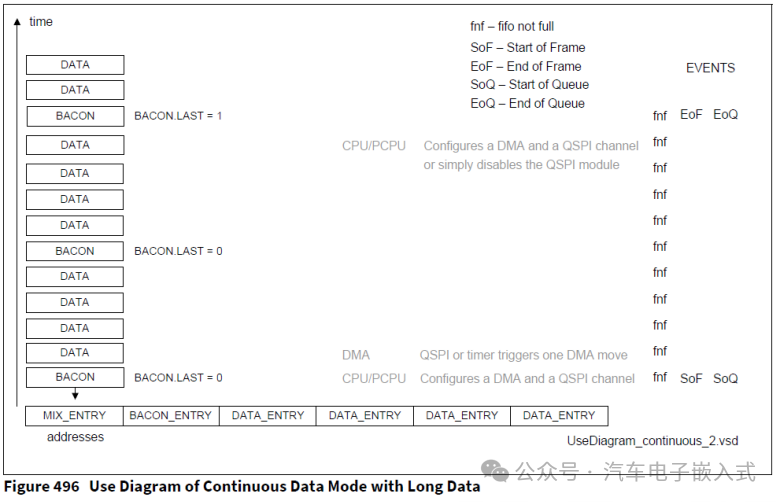

在连续数据模式下,QSPI传输任意长度的数据流且激活从设备片选信号。它可以用于短数据和长数据。

此模式首先对包含BACON.LAST=0和第一个数据的控制字进行编程。通信继续进行,随后写入数据条目。该模式以包含BACON. LAST=1和最后一个数据的控制字结束。如果LAST=0,则TRAIL是数据块之间的延迟。显示W_I_L_D_T_D_T_D_D_T序列。每个“D” 代表BACON. DL定义的数据块。和BACON. BYTE(最多256位)。如果LAST=1,则TRAIL是trailing延迟。

下图显示了使用短数据的连续数据模式的示例。这里,CPU通过将BACON写入BACON_ENTRY地址来启动流,然后DMA传输除最后一个BACON和DATA之外的整个流。

下图显示了使用长数据的连续数据模式的示例。在这里,第一个BACON必须在每个数据块之后重复,但另一方面,整个传输可以仅使用MIX条目和一个DMA通道完成,无需CPU参与。通过使用长数据块,可以最大限度地减少由于不必要的额外BACON而导致的效率损失。

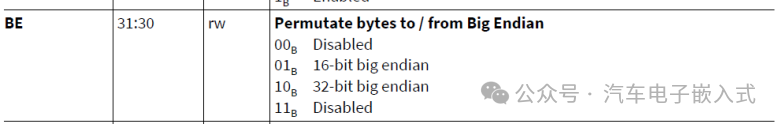

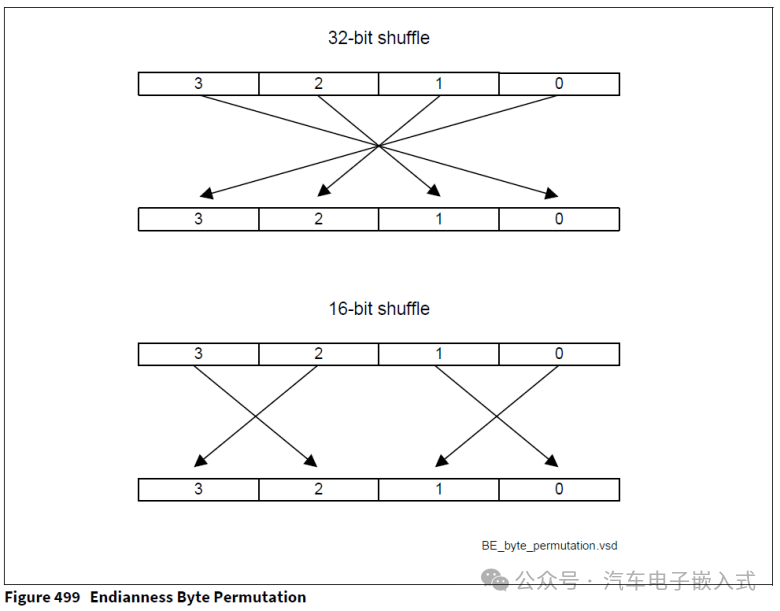

ECONz(z=0-7).BE位域激活写入移位寄存器的数据字节的排列,并从移位寄存器读取到大端序格式并返回。

ECONz(z=0-7).BE允许每个从设备在大端序和小端序之间切换(SLSO信号)。

将数据从小字节序转换为大端序和其他方式需要对数据字节进行相同的排列,如下图所示,一个排列块位于移位寄存器之前,一个位于移位寄存器之后,因此只能对数据进行排列,而不能对BACON或STATUS进行排列。

端序字节排列应仅用于16位和32位数据(及其倍数),而不适用于其他数据长度。

有几种类型的中断:

. 用户接口(user interface)相关的中断

-FIFO相关的中断

. 和移动引擎(Shift engine, 也就是state machine)相关的中

-Error中断

-Phase transition 中断

根据这种分类,以下是所有中断的完整列表:

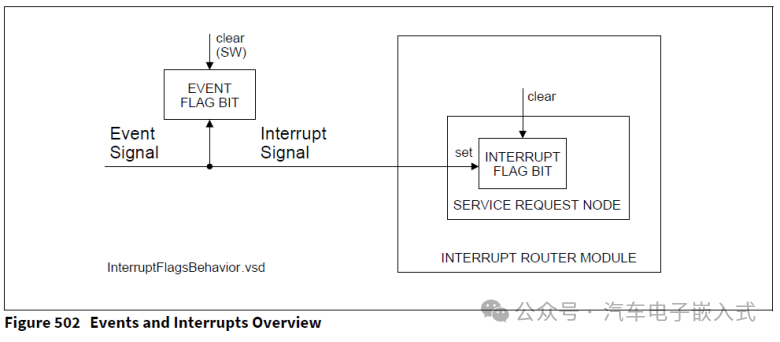

事件标志的状态(低或高)不影响其事件信号的流动。如果事件反复发生,并且事件标志保持设置状态(如果未被软件中断处理程序清除),则中断标志(当中断赢得仲裁轮时,由硬件、ICU清除)将收到反复触发,并且该标志将始终保持设置状态。

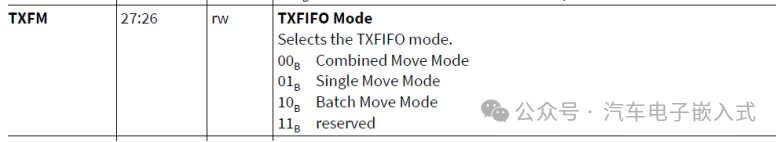

TXFIFO提供两种中断生成模式(Combined Mode是由两种中断生成模式组合的),由位字段GLOBALCON1.TXFM选择:

. Single Move Mode

. Batch Move Mode

. Combined Mode

RXFIFO和TXFIFO可以彼此独立地使用中断生成模式。

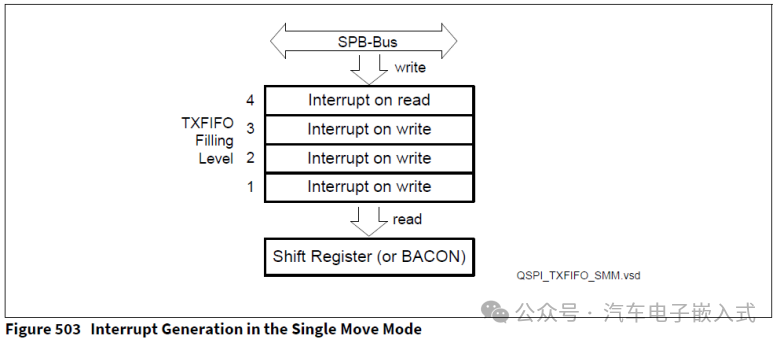

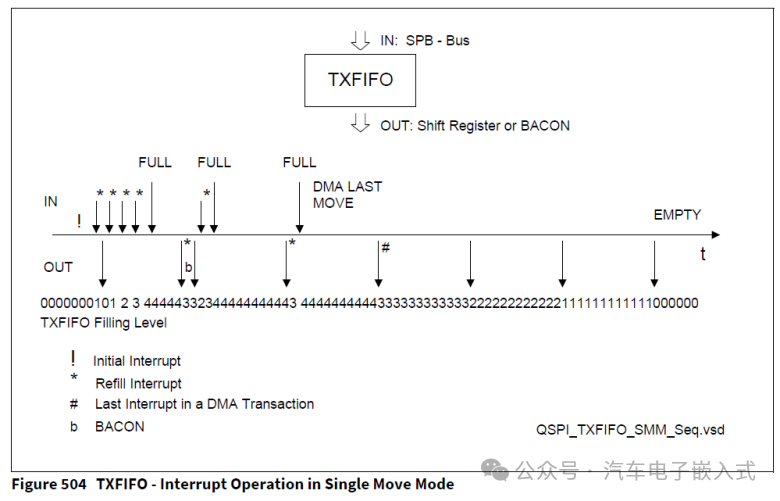

Single Move Mode

单移动模式的目的是使TXFIFO尽可能满,一旦有空闲元素,就通过写入来重新填充TXFIFO。

一个示例可能是使用单移动模式,DMA在每个TXFIFO中断时执行单移动。在此模式下,DMA保持TXFIFO满。每次执行对TXFIFO的写入时,都会触发DMA请求,并且至少有一个空元素可用。如果写入使TXFIFO满(不再有空元素),则不会生成中断以防止溢出。稍后,当移位寄存器(或BACON)从TXFIFO读取一个元素,使其未满时,它就会生成。

下图显示了TXFIFO的填充水平(filling levels),以及与触发TXFIFO填充中断的每个填充水平相关的事件。

为了在上电复位后启动重新填充中断的第一个链,软件需要对TXFIFO执行一次写入,或者在TXFIFO中断节点中设置中断标志。之后,(DMA)中断链是自我维持的,直到整个事务结束。

注意:在单移动模式下,多个软件写入或阻塞DMA移动将导致多个中断和(错误)事务丢失事件。因此,应避免使用这些动作——只应使用单次动作。

Infineon芯片的MCAL仅支持Single Move Mode, 这里就不再介绍Batch Move Mode和Combined Mode, 感兴趣的可以自己去研究。

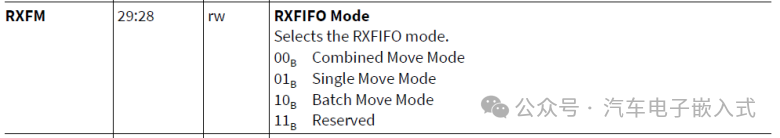

RXFIFO提供两种中断生成模式(Combined Mode是由两种中断生成模式组合的),由位字段GLOBALCON1.RXFM选择:

. Single Move Mode

. Batch Move Mode

. Combined Mode

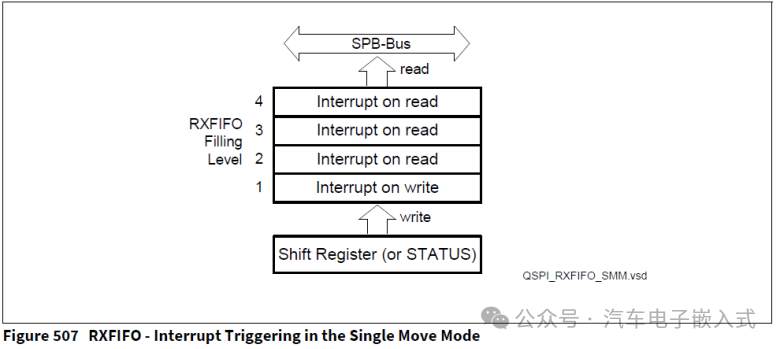

Single Move Mode

单移动模式的目的是通过尽快逐一获取接收到的元素,使RXFIFO尽可能保持为空。

一个示例是使用单移动模式,DMA在每个RXFIFO中断时执行单移动。在这种模式下,DMA尽可能地保持RXFIFO为空。每次执行从RXFIFO的读取时都会触发DMA请求,并且RXFIFO之后仍然不是空的。如果读取使RXFIFO为空,则不会生成中断以防止下溢。稍后,当移位寄存器(或STATUS)将新元素写入空的RXFIFO时,它会生成。

下图显示了RXFIFO的填充水平(filling level),以及与触发RXFIFO填充中断的每个填充水平相关的事件。

初始RXFIFO中断由移位寄存器在传递第一个接收到的元素后触发。之后,重新获取中断的DMA触发链是自我维持的,直到整个事务结束。在DMA事务结束时,由于读取RXFIFO中的最后一个元素不会触发中断,因此服务请求节点中没有服务请求保持活动状态。

注意:在单移动模式下,多个软件读取或块DMA移动会导致多个中断和(错误)事务丢失事件。因此,应避免使用这些动作——只应使用单次动作。

关于MCAL SPI模块的详细介绍,请参考《AUTOSAR-MCAL--SPI模块详解(三)》一文。

配置MCAL SPI模块,除了SPI模块外还需要配置Port模块,OS模块,如果使用DMA还需要配置DMA模块。

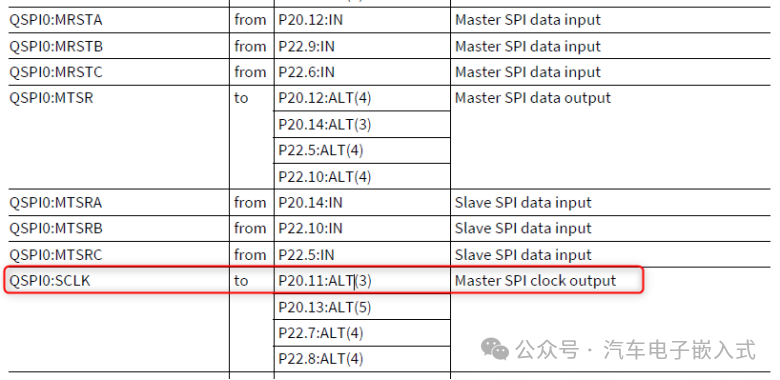

比如,我们要配置SPI0:SCLK时钟信号,则需要配置P20.11(3)引脚。

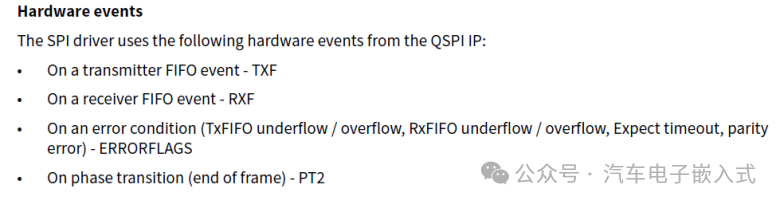

Infineon的MCAL SPI支持以下中断:

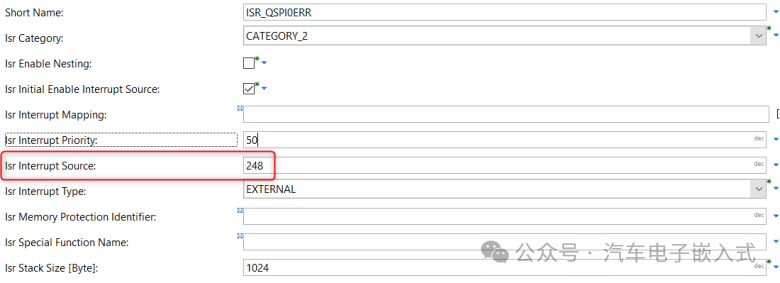

配置OS中断,其中的Isr Interrupt Source需要计算,参考1.3.章节的计算公式即可。

参考《英飞凌TC3XX MCAL QSPI实操指南 (qq.com)》

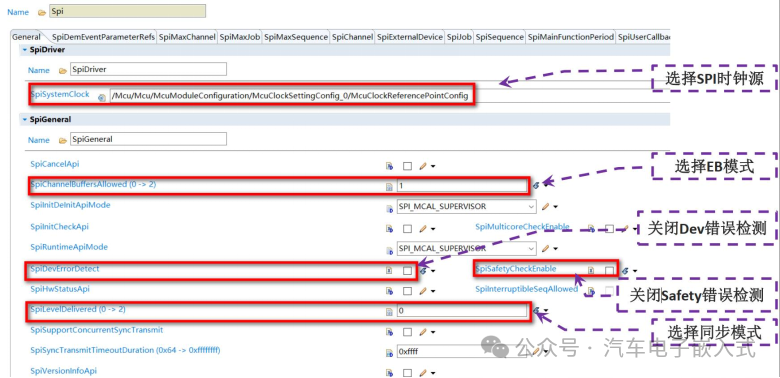

跟之前的列举的其他模块一样,首先是General模块的配置,包括时钟源,SPI的模式,另外错误检测以及safety检测的关闭或者开启,可根据需求来设置。

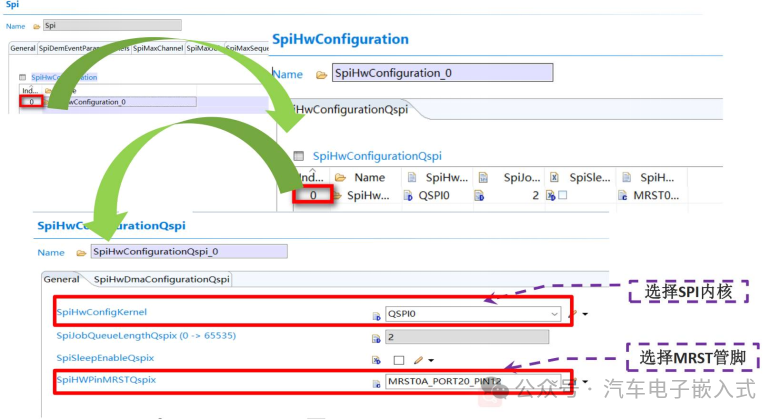

第二步则是配置SpiHwConfiguration模块,包括SPI内核的设置以及接收引脚的配置。

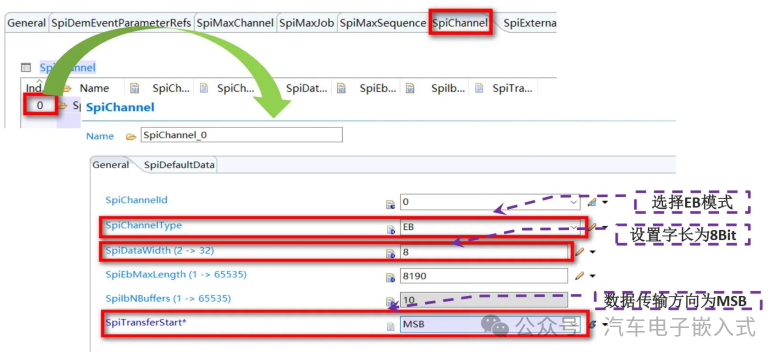

第三步则是通道的配置,包括模式,数据长度,传输方向等。

需要根据Slave设备的特性来配置Channel,一般来说Slave设备的DataSheet中规定了这些参数的(参考《》一文中L9301的SPI帧格式),Master Device需要按Slave Device规则来配置。如果Slave Device也是一个MCU/SOC,则需要双方来设计协议。

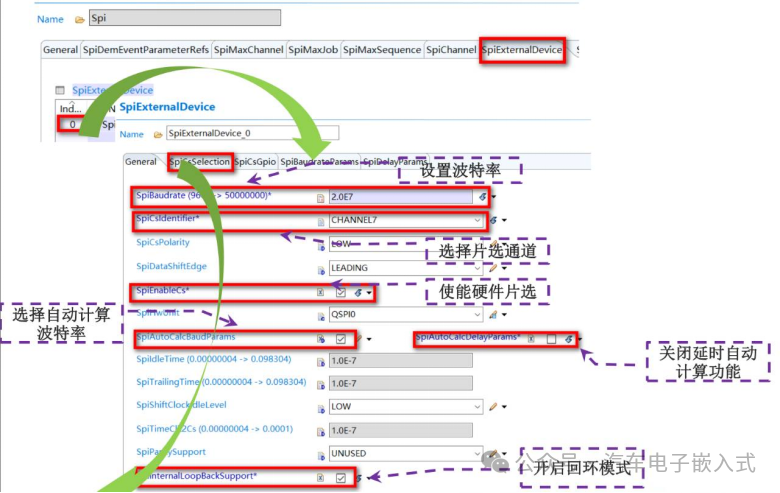

第四步则是波特率,片选通道、开环模式的配置。

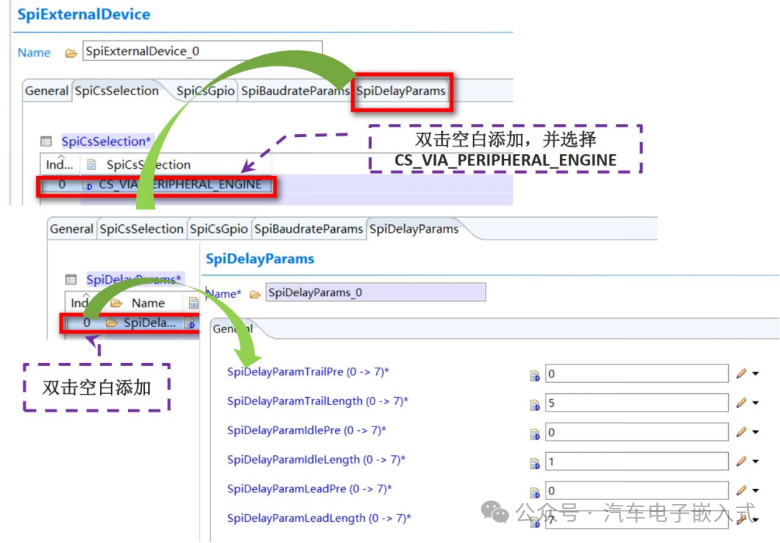

第五步则是上述提到的idle/trail等时间参数的设置。

SpiDelayParams中的参数说明参考3.2.1章节,也就是配置SPI帧时序,这些时序一般也是来着Slave Device的DataSheet说明。

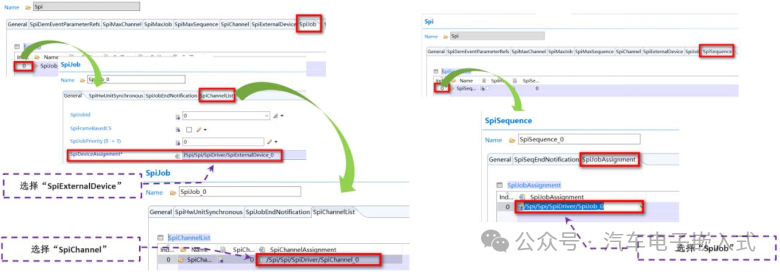

第六步则是Job或者Squence的配置。

如果是一个Master Device挂载一个Slave Device,那么只配置一个Sequence + 一个Job + 一个Channel就能时序功能,如果一个Master Device挂载多个Slave Device就需要设计多个Sequence + 多个Job + 多个Channel了。SPI使用者需要深入理解Sequence,Job, Channel之间的关系。

SPI可以使用DMC,也可以不使用,关于SPI的DMA数据传送内容敬请期待…

本文1-3章节基本是TC3xx芯片手册上的内容翻译,为啥要这么辛苦的翻译一遍了?-- 不做笔记不读书,只有一行一行的阅读过,思考过才能窥探这个模块的全貌,不然总感觉不全。各位看官根据需要阅读即可,不必像作者一样这么纠结。

对于QSPI模块的使用者,其实只要弄清楚以下内容即可:

1.QSPI有多少硬件资源,实际项目具体使用的是哪个QSPI modle, 具体使用了QSPI module的哪些信号连接(MTSR, MRST, SCK, SLS具体使用哪些Pin)?

2.如何配置QSPI使用的Pin脚(Port模块)?

3.如何配置SPI的时钟?

4.如果配置QSPI帧的时序?

5.TXFIFO和RXFIFO的好处,以及用户如何使用TXFIFO和RXFIFO?

6.QSPI会产生哪些中断,中断产生的时机是?

如果使用AUTSOAR MCAL SPI模块,着重要搞清楚SPI模块Chanel, Job, Sequence的逻辑含义:

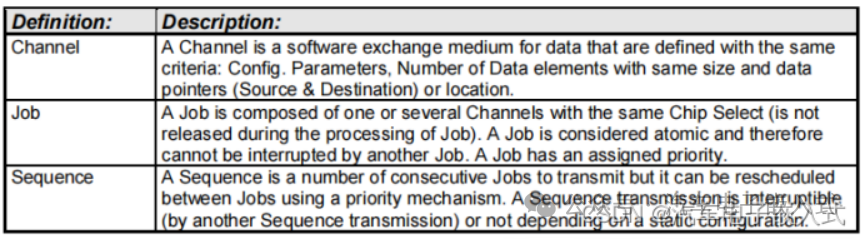

1个Channel对应1个发送缓冲区和1接收缓冲区;1个Job对应着1次SPI通讯发送的内容(既SPI一次片选过程所传输的内容)。1个Sequence 对应着1个SPI通讯序列(job序列)。多个Job可以分配给一个Sequence。SPI通讯是基于Sequence触发的,即使发送1个Job也要将该Job分配给1个队列,然后通过触发Sequence来实现Job的传输。

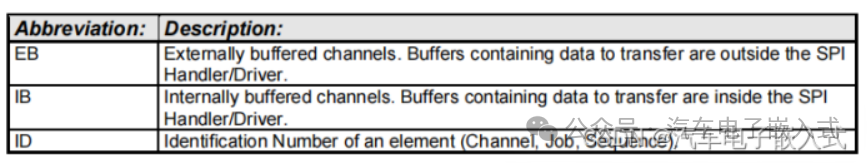

理解EB和IB的含义:

EB: 外部缓冲通道。包含要传输的数据的缓冲区在SPI处理程序/驱动程序之外。

IB: 内部缓冲通道。包含要传输的数据的缓冲区位于SPI处理程序/驱动程序中。一般都是配置为Internally Buffer。

如果Master SPI只挂载一个Slave Device, 那么只设计一个Sequence,一个Job,一个Channel也可以完成SPI数据的发送及功能的实现。但是对于多个Slave Device且每个Device有不同的读写数据格式,就要设计多个Sequence, 多个Job, 多个Channel了。

涉及使用SPI的复杂驱动的时候,需要考虑:

1.AUTOSAR架构下MCAP_SPI模块的详细设计,着重理解Channel,Job,Sequency的概念,SPI异步发送过程,以及EB和IB缓存的适用场景。

2.从具体芯片(RENESAS,NXP,Infineon等)的SPI模块,主要了解芯片SPI模块的波特率配置、时钟配置、时序配置。

3. 具体外设芯片(L9301,L9369,35584,FS6522等),主要了解芯片的输入输出配置及功能,Pin定义,SPI帧结构、寄存器功能、时序要求。

End

「汽车电子嵌入式在CSDN上同步推出AUTOSAR精进之路专栏,本专栏每个模块完全按实际项目中开发及维护过程来详细介绍。模块核心概念介绍、实际需求描述、实际工程配置、特殊需求介绍及背后原理、实际工程使用经验总结。目的是让读者看完每一个章节后能理解原理后根据需求完成一个模块的配置或者解决一个问题。」

点击文章最后左下角的阅读原文可以获取更多信息

或者复制如下链接到浏览器获取更多信息

https://blog.csdn.net/qq_36056498/article/details/132125693

文末福利

2.为便于技术交流,创建了汽车电子嵌入式技术交流群,可尽情探讨AP,CP,DDS,SOME/IP等前沿热点话题,后台回复“加群”即可加入;

注:本文引用了一些第三方工具和文档,若有侵权,请联系作者删除!

推荐阅读

汽车电子嵌入式精彩文章汇总第一期:20210530-20230703

汽车电子嵌入式精彩文章汇总第2期

汽车电子嵌入式精彩文章汇总第3期

【OS】AUTOSAR OS Event实现原理

【OS】AUTOSAR OS Spinlock实现原理(下篇)

【OS】AUTOSAR OS Spinlock实现原理(上篇)

CanNm处于PBS状态下接收到一帧诊断报文DCM会响应吗

TC3xx芯片CAN模块详解

AUTOSAR OS Alarm实现原理

AUTOSAR OsTask切换原理

End

欢迎点赞,关注,转发,在看,您的每一次鼓励,都是我最大的动力!

汽车电子嵌入式

微信扫描二维码,关注我的公众号