时间的重要性不言而喻,加上时间这个维度就如同X-Y的平面加上了一个Z轴,如同打开了一个新的世界。所以今天我们就要来聊聊时序电路。

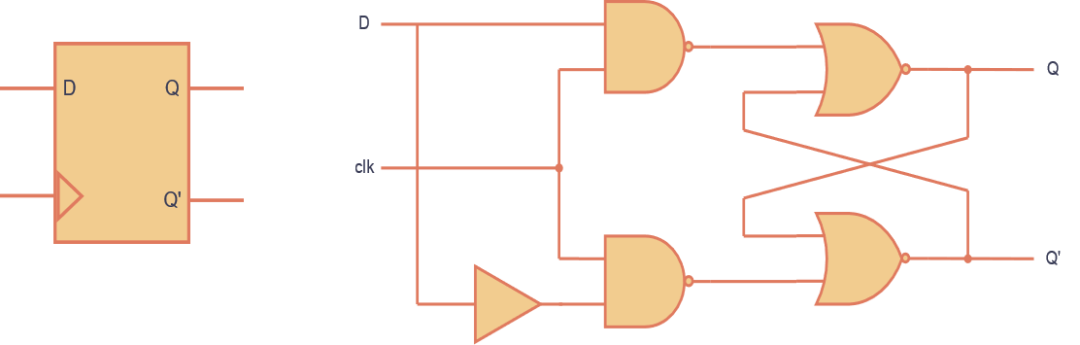

图1 D触发器框图和内部门电路结构

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

module dff2input clk,d,output reg q,output wire qbar);= ~q;always @(posedge clk) // 只有clk上升沿时刻触发= d; // 只有当触发生效时,才将d的值赋予给qendmodule

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

而为了帮助更多老师快速上手FPGA的使用和教学,在即将到来的寒假,我们针对高校从事教学/实验室一线工作的教师,推出一个为期5天(2021年1月25日-1月29日)的FPGA设计及应用快速培训,通过实用性非常强的典型案例动手实践,帮助大家快速、有效地上手FPGA,并能够在未来的教学、实践、电赛中大显身手,硬禾实战营也将成为参加培训的老师们长期的教学后援。

详情请见这里或者今天公众号的二条。期待在美丽的苏州跟您一起探讨FPGA和教学实践的结合。

END

硬禾学堂

硬禾团队一直致力于给电子工程师和相关专业的同学,带来规范的核心技能课程,帮助大家在学习和工作的各个阶段,都能有效地提升自己的职业能力。

硬禾学堂

我们一起在电子领域探索前进

关注硬禾服务号,随时直达课堂

点击阅读原文报名参加高校教师培训班