-----本文简介-----

主要内容包括:

LDO与DC-DC串联到底能抑制多少纹波?

关注微信公众号:硬件之路学习笔记

回复:粉丝群,领取资料

----- 正文 -----

先赞↓后看,养成习惯!

实际上由于现在追求小体积,DC-DC的频率越来越高,也就意味着其纹波频率越来越高。为何频率越高体积越小?点击此前的文章了解:如何减小DC-DC芯片外围电路体积?

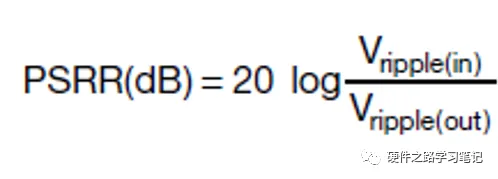

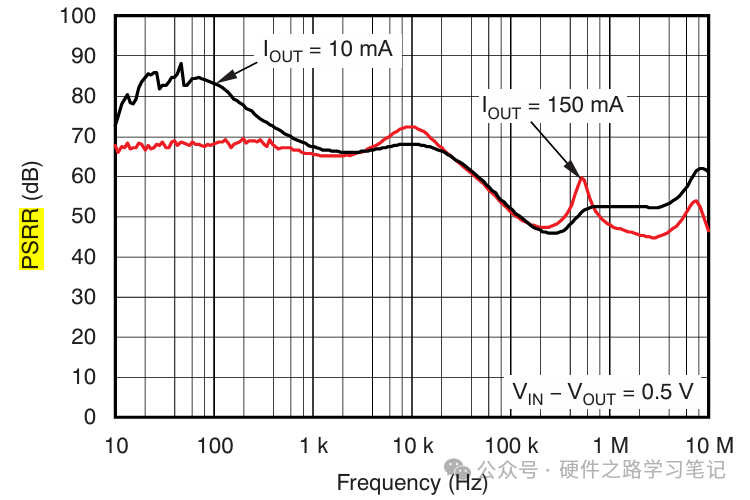

如下是TI的一款DC-DC,典型的工作频率为1.5MHz,那么参考上图,其1.5MHz下的PSRR大约为45dB,也就是能把纹波抑制为1/178。

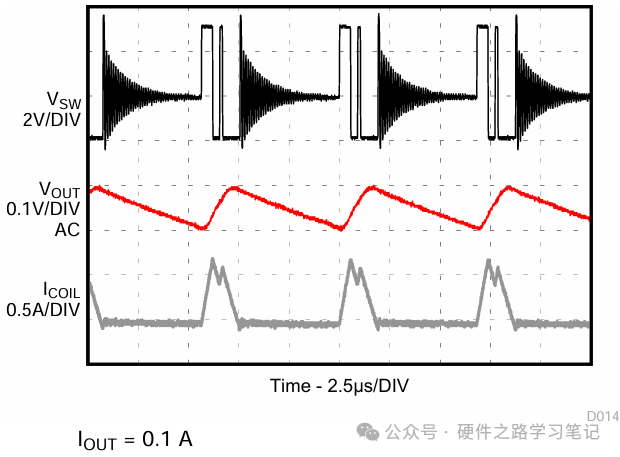

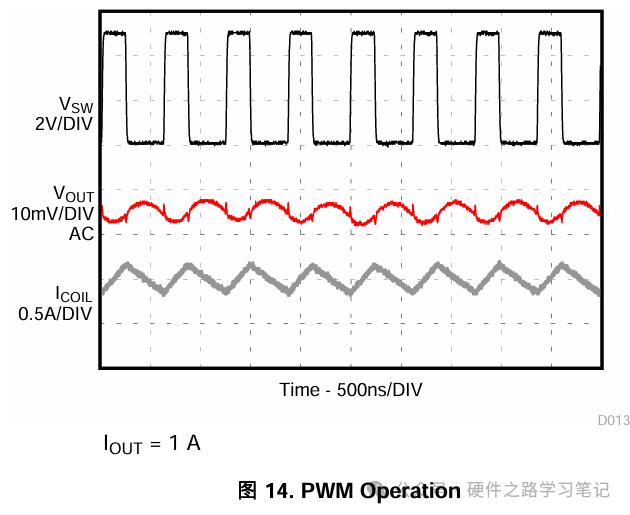

要注意的是,DC-DC在低负载下会切换为PFM模式,即其频率会降低,例如下图降低到了大约200kHz,在此频率下不仅DC-DC的纹波会增大,LDO的PSRR也会改变,因此在设计中也要关注不同频率下的PSRR,并且调试时测试不同负载下的纹波。