前面我们完成了C906的工程创建和综合,现在开始就可以进行引脚和时钟约束进行实现生成bit文件了。同时我们根据板子插座和需要的引脚设计一个简单的IO扩展板,方便调试。

根据顶层文件可以看到需要以下18个引脚

其中clk是时钟输入

j开头的是6个jtag相关引脚,jclk是jtag的时钟输入。其中 jrst_b是对调试接口复位, jnrst_b是对目标系统复位。

一个串口2个引脚 uart0_sout,uart0_sin

一个8p的IO ,b_pad_gpio_porta

一个系统复位 rst_b

clk先直接使用外部晶振,先跑50MHz, 后面再尝试使用内部时钟资源倍频跑更高的速率。

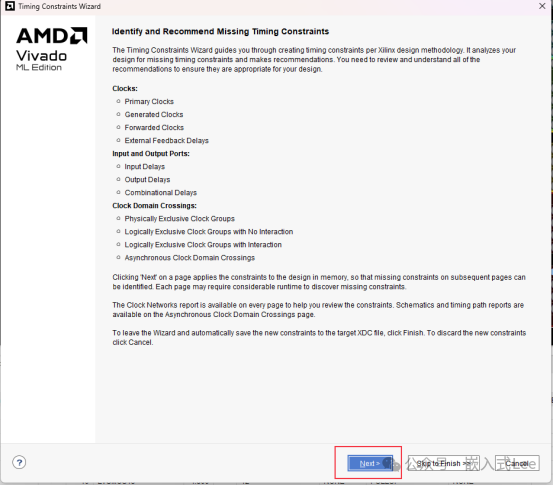

clk和jclk都要做时钟约束。

module c906_top(clk,rst_b,uart0_sin,uart0_sout,b_pad_gpio_porta,jclk,jrst_b,jnrst_b,jtg_tdi,jtg_tdo,jtg_tms);input clk;inout[7:0] b_pad_gpio_porta;input rst_b;input jclk;input jtg_tdi;input jtg_tms ;input uart0_sin;output jtg_tdo;output uart0_sout;input jnrst_b;input jrst_b;soc x_soc(.i_pad_clk ( clk ),.b_pad_gpio_porta ( b_pad_gpio_porta ),.i_pad_jtg_trst_b ( jrst_b ),.i_pad_jtg_nrst_b ( jnrst_b ),.i_pad_jtg_tclk ( jclk ),.i_pad_jtg_tdi ( jtg_tdi ),.i_pad_jtg_tms ( jtg_tms ),.i_pad_uart0_sin ( uart0_sin ),.o_pad_jtg_tdo ( jtg_tdo ),.o_pad_uart0_sout ( uart0_sout ),.i_pad_rst_b ( rst_b ));endmodule

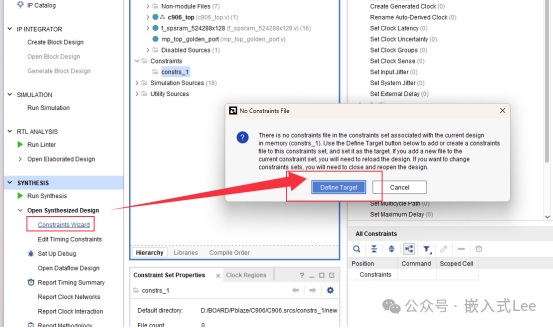

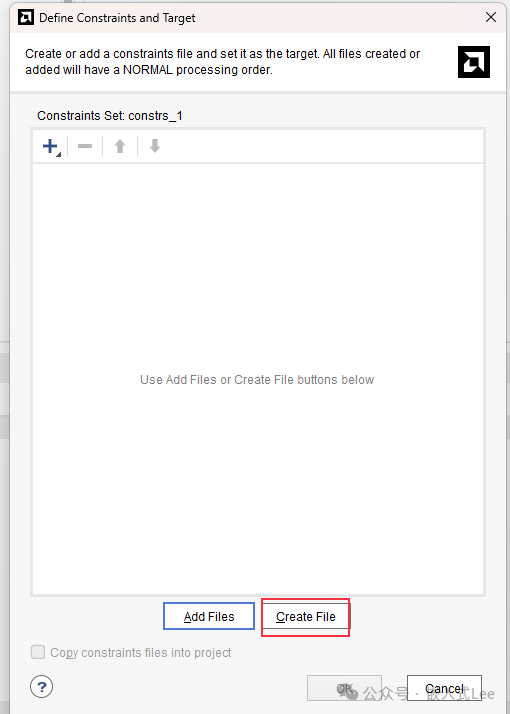

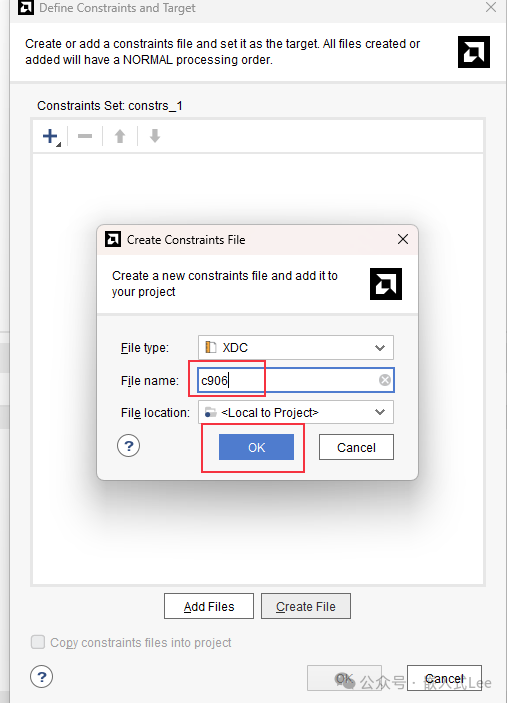

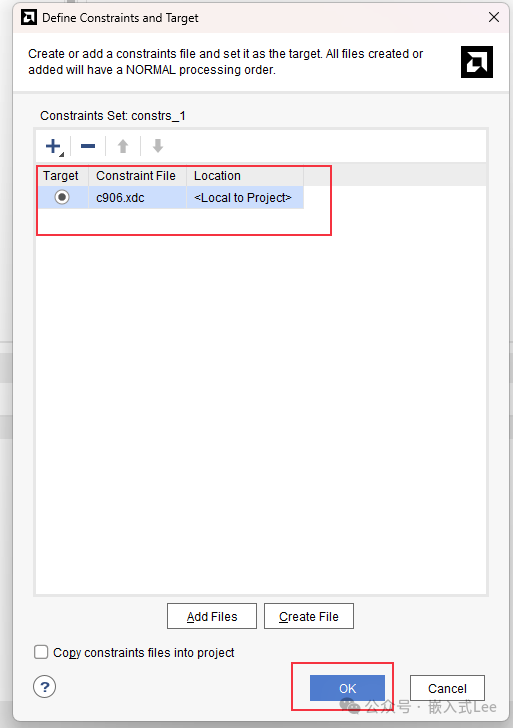

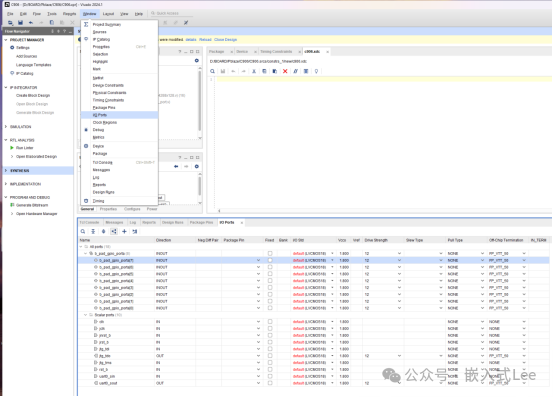

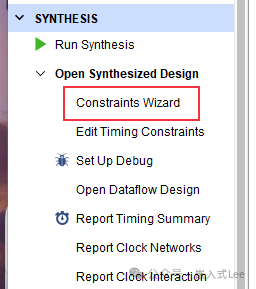

打开约束向导

左侧Flow导航选中SYNTHSIS,菜单栏Window->I/O ports显示对应界面

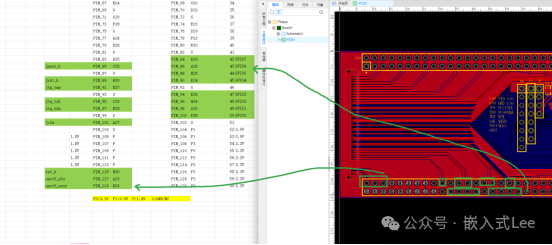

我们对应JK1插座的如下引脚

对应我们设计的IO扩展板的如下位置

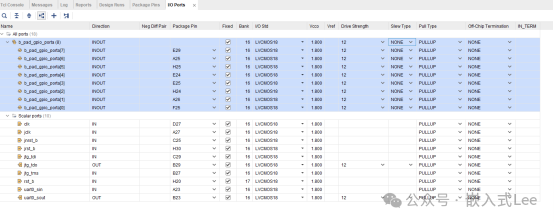

配置如下

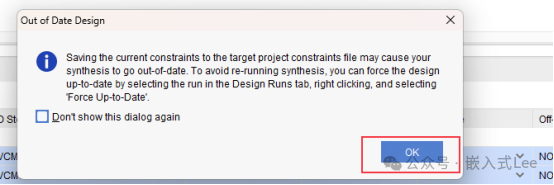

Ctrl+s保存

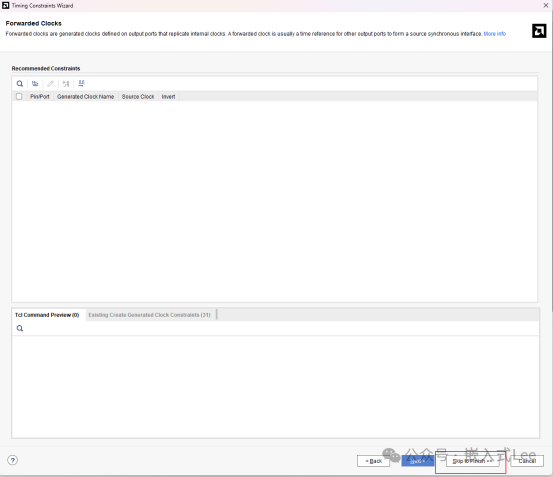

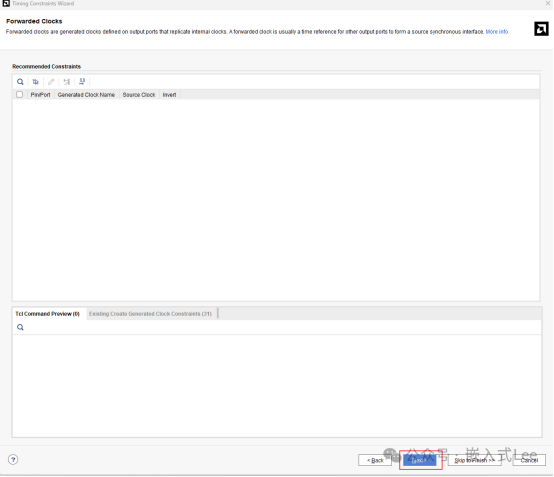

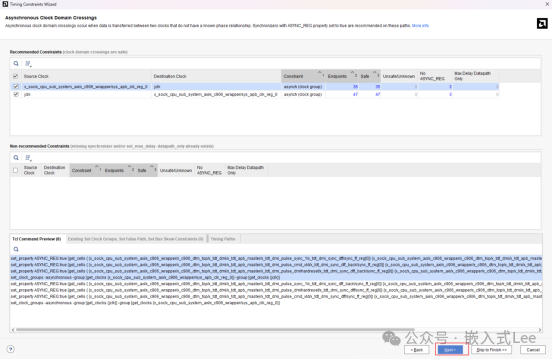

打开SYNTHSIS下的约束向导

CLK为50M,JCLK为jtag仿真器输出soc输入,先按照1M设计,如果不行以后再降低(最低100KHz)

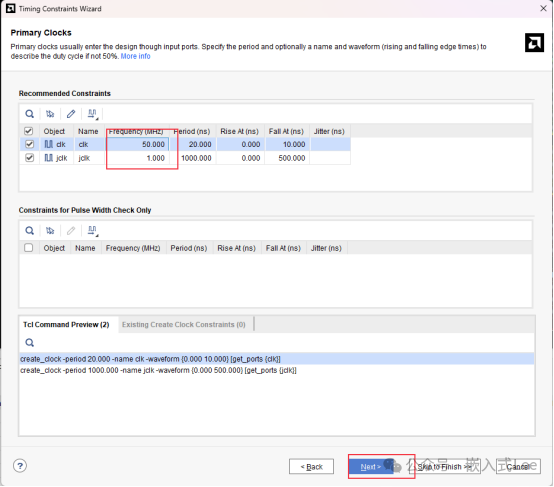

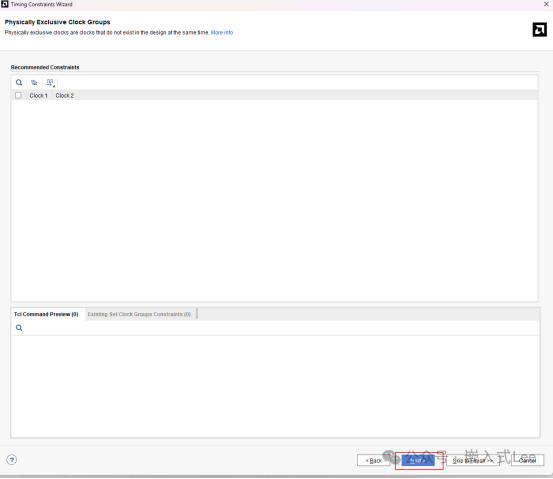

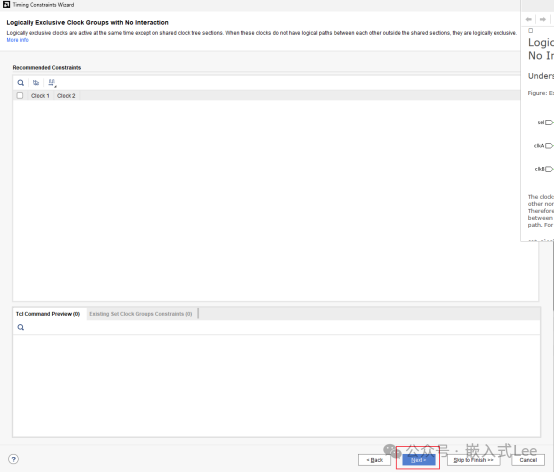

所有子时钟分批都设置为1

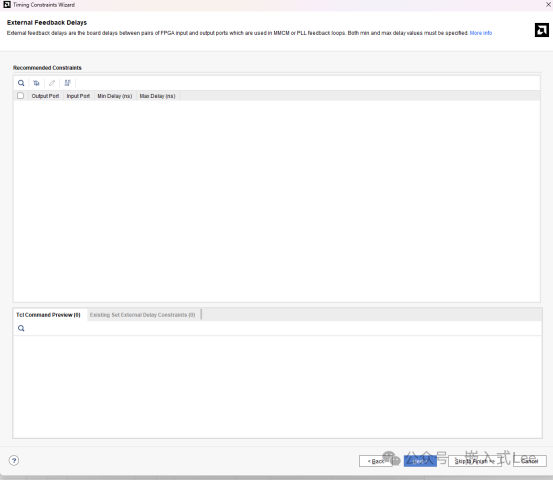

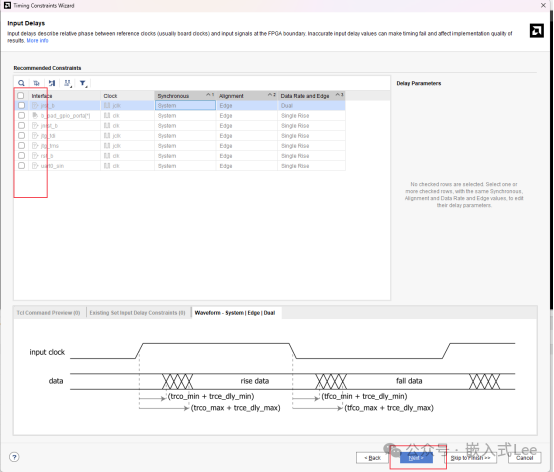

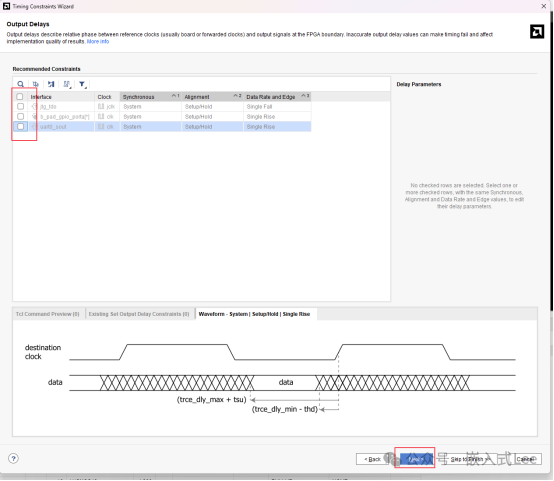

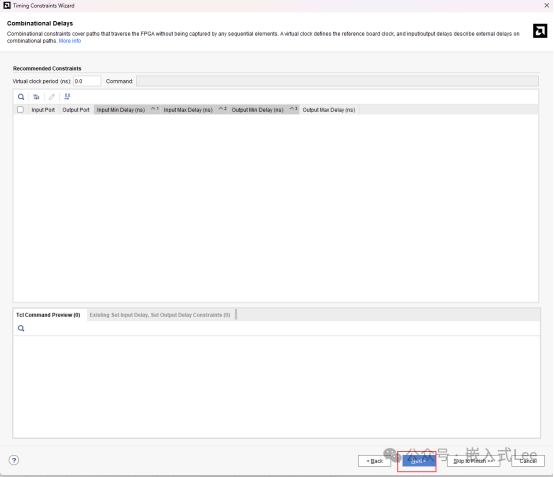

输入延迟先不设置

输出延迟也不设置

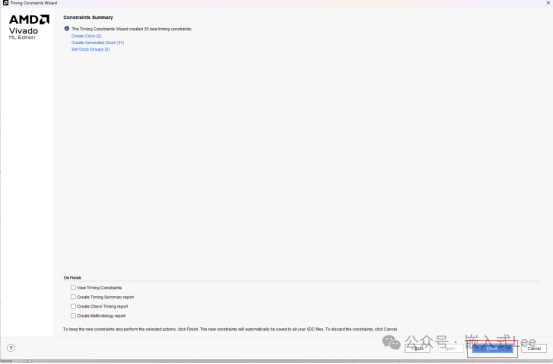

最终约束文件xdc内容如下

set_property DRIVE 12set_property PACKAGE_PIN E29set_property PACKAGE_PIN A25set_property PACKAGE_PIN H25set_property PACKAGE_PIN E24set_property PACKAGE_PIN E25set_property PACKAGE_PIN H24set_property PACKAGE_PIN A26set_property PACKAGE_PIN F25set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PACKAGE_PIN D27set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property IOSTANDARD LVCMOS18set_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PULLTYPE PULLUPset_property PACKAGE_PIN A27set_property PACKAGE_PIN C25set_property PACKAGE_PIN H30set_property PACKAGE_PIN C29set_property PACKAGE_PIN B29set_property PACKAGE_PIN B27set_property PACKAGE_PIN H20set_property PACKAGE_PIN A23set_property PACKAGE_PIN B23set_property SLEW SLOWset_property SLEW SLOWset_property SLEW SLOWset_property SLEW SLOWset_property SLEW SLOWset_property SLEW SLOWset_property SLEW SLOWset_property SLEW SLOWcreate_clock -period 20.000 -name clk -waveform {0.000 10.000}create_clock -period 1000.000 -name jclk -waveform {0.000 500.000}set_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property ASYNC_REG trueset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEset_property OFFCHIP_TERM NONEcreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[12]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[13]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[14]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[15]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[16]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[17]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[18]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[19]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[20]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[21]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[22]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[23]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[24]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[25]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[26]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[27]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[28]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[29]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[30]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[31]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[32]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[33]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[34]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[35]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[36]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[37]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[38]} -sourcecreate_generated_clock -name {x_soc/x_apb/x_apb_bridge/apb_xx_paddr_reg_n_0_[39]} -sourcecreate_generated_clock -name x_soc/x_apb/x_apb_bridge/apb_xx_psel -sourcecreate_generated_clock -name x_soc/x_apb/x_apb_bridge/apb_xx_pwrite -sourcecreate_generated_clock -name x_soc/x_cpu_sub_system_axi/x_c906_wrapper/sys_apb_clk_reg_0 -sourceset_clock_groups -asynchronous -groupset_clock_groups -asynchronous -group

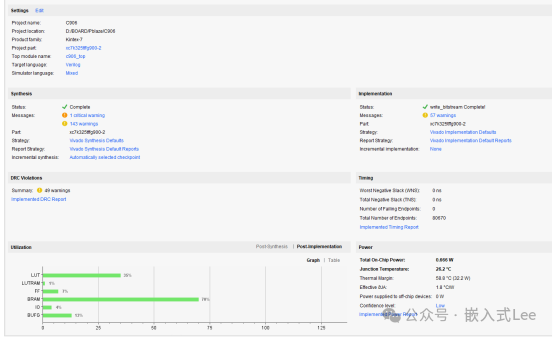

再重新综合,实现

报如下错误

现在xdc文件前加一行暂时忽略这个错误

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets jclk_IBUF]

最后生成bit文件

有一些告警先不管,等IO扩展板回来了先试一下能不能连接JTAG再调试。

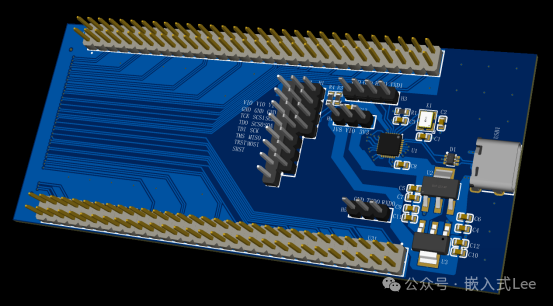

使用嘉立创EDA在线版,简单画了个IO扩展板,先不考虑其他的,线拉出来就行,目前仅仅是方便测试,调通了之后后面再专门设计对应功能的扩展板。

扩展板打样大概三四天能到,顺便也采购下板对板插座等元器件,基本也是三四天才能到。

这里基于CH347设计了一个JTAG工具,后面考虑使用openocd配合这个工具调试,可以openocd有一些适配开发工作。

以上完成了移植工作,生成了bit文件,后面就等IO扩展板回来,测试jtag是否能连接了。然后接下来就是简单的程序运行测试,再进一步添加ddr控制器提供大的存储方便移植uboot和linux。