前面创建了LED工程进行简单的测试,本文继续分享下使用ILA进行在线信号抓取分析。

ILA即内部逻辑分析仪。使用该IP结合JTAG仿真器可以方便的进行在线信号分析。

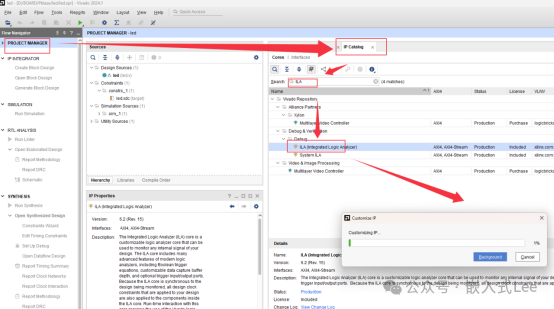

PROJECT MANAGER-> IP Catalog

搜索ILA,双击ILA(Integrated Logic Analyzer)

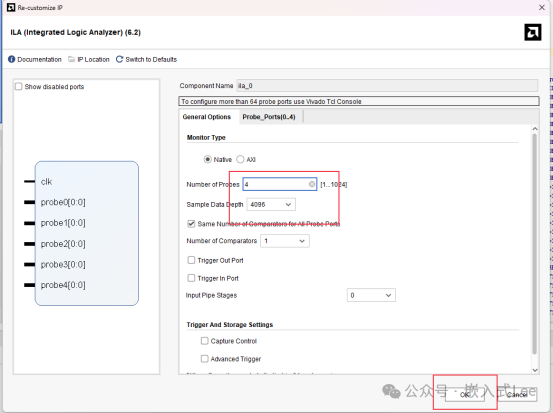

设置需要探测的信号个数,和采样深度

在led.v的

module led中例化ILA

module led(input sys_clk, //system clock 50MHZ on boardinput rst_n, //reset low activeoutput reg[2:0] led //LED use of control the LED signal on board);reg [31:0] timer;//==============================//cle counter : from 0 to 4 sec//==============================always @(posedge sys_clk or negedge rst_n)beginif(~rst_n)timer <= 32'd0; //when the reset signal valid,time counter clearingelse if(timer == 32'd149_999_999) //4 seconds count(50M * 4 - 1 = 199_999_999)timer <= 32'd0; //count done,clearing the time counterelsetimer <= timer + 1'b1; //timer counter = timer counter + 1end//==============================//LED control//==============================always @(posedge sys_clk or negedge rst_n)beginif(~rst_n)led <= 3'b111;else if(timer == 32'd49_999_999)led <= 3'b011;else if(timer == 32'd99_999_999)led <= 3'b110;else if(timer == 32'd149_999_999)led <= 3'b101;endila_0 u_ila(.clk(sys_clk),.probe0(rst_n),.probe1(led[0]),.probe2(led[1]),.probe3(led[2]));endmodule

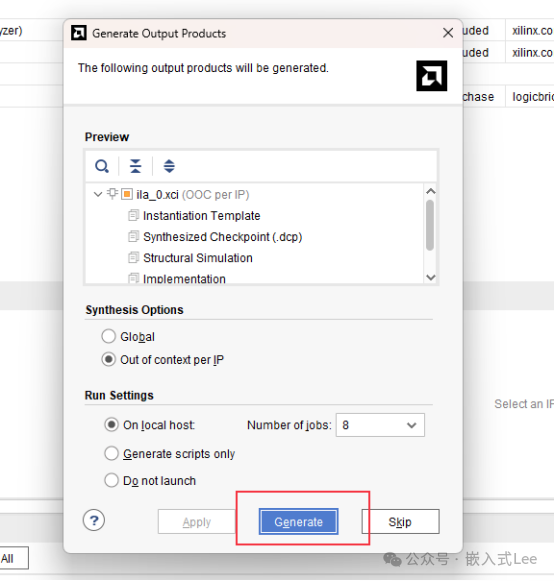

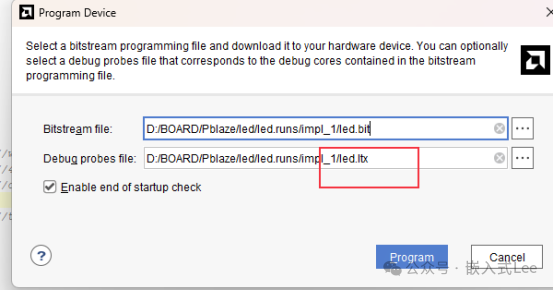

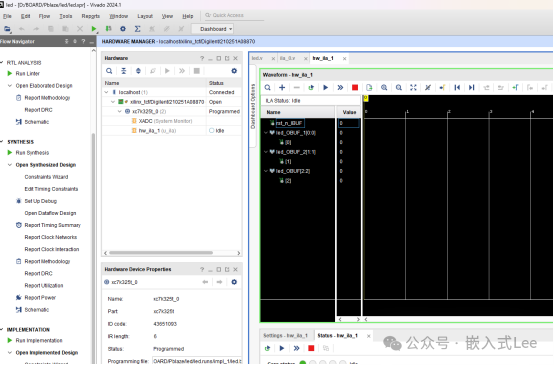

综合实现,下载bit文件

此时会有个ltx文件

Ila选项卡下可以看到信号

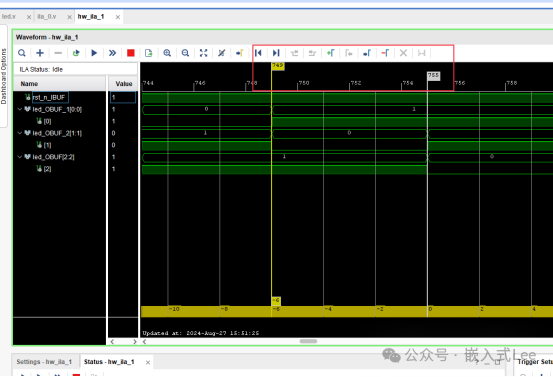

由于时间太长,不便于仿真,可以将闪烁的时间间隔减小

module led(input sys_clk, //system clock 50MHZ on boardinput rst_n, //reset low activeoutput reg[2:0] led //LED use of control the LED signal on board);reg [31:0] timer;//==============================//cle counter : from 0 to 4 sec//==============================always @(posedge sys_clk or negedge rst_n)beginif(~rst_n)timer <= 32'd0; //when the reset signal valid,time counter clearingelse if(timer == 32'd15) //4 seconds count(50M * 4 - 1 = 199_999_999)timer <= 32'd0; //count done,clearing the time counterelsetimer <= timer + 1'b1; //timer counter = timer counter + 1end//==============================//LED control//==============================always @(posedge sys_clk or negedge rst_n)beginif(~rst_n)led <= 3'b111;else if(timer == 32'd5)led <= 3'b011;else if(timer == 32'd10)led <= 3'b110;else if(timer == 32'd15)led <= 3'b101;endila_0 u_ila(.clk(sys_clk),.probe0(rst_n),.probe1(led[0]),.probe2(led[1]),.probe3(led[2]));endmodule

可以看到依次间隔6个时钟依次点亮

以上分享了使用内部逻辑分析仪ILA进行在线信号抓取分析,该方式无需外部逻辑分析仪,方面进行信号的抓取分析,比较方便。