《ESD与Latch-up: 高抗性与解决方案》

随着小芯片(chiplet )设计的出现,半导体行业正在经历重大变革,小芯片设计是一种模块化方法,可将复杂的芯片分解成更小的功能块,称为小芯片。基于 chiplet 的设计方法具有许多优势,例如提高性能、降低开发成本和加快上市时间。这种方法通过将缺陷隔离到单个模块来提高产量,通过允许不同组件使用不同的制造节点来优化晶体管成本,并利用先进的封装技术来增强性能。小芯片的模块化支持可扩展、可定制的设计,可加快产品上市时间,并实现性能、功耗和成本的有针对性优化。然而,广泛采用的最重大障碍之一是这些小芯片之间的通信方式缺乏标准化。Universal Chiplet Interconnect Express (UCIe) 标准有望改变这种状况,使 Chiplet 设计更易于访问,并为整个行业的创新开辟新的机遇。

标准化和互操作性

在标准化小芯片接口之前,需要为每个小芯片进行定制设计,这导致了更高的成本、更长的开发时间和有限的互操作性。公司必须为其小芯片开发专有接口,因此很难集成来自不同供应商的组件。这种互操作性的缺乏增加了开发成本,并限制了可用的小芯片池。

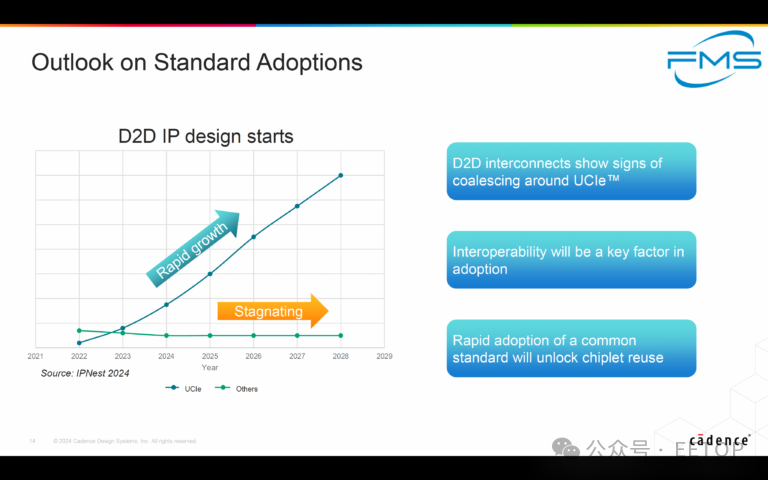

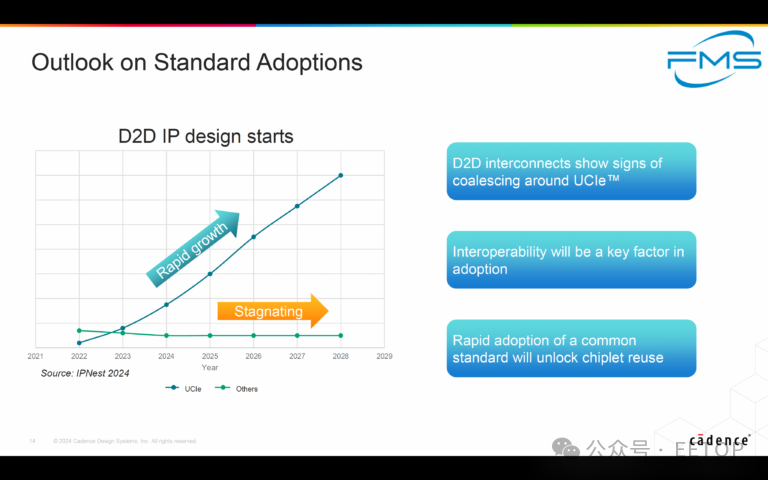

小芯片接口标准的采用简化了这一过程,使设计人员能够专注于核心创新,同时使用预先验证的接口进行通信。这减少了定制设计工作,加快了开发速度,并确保了无缝集成。公司现在可以利用经过验证的小芯片,降低成本并提高质量。总体而言,标准化简化了设计,减少了资源使用,并加快了上市时间。最近,已经制定了许多小芯片到小芯片接口标准。

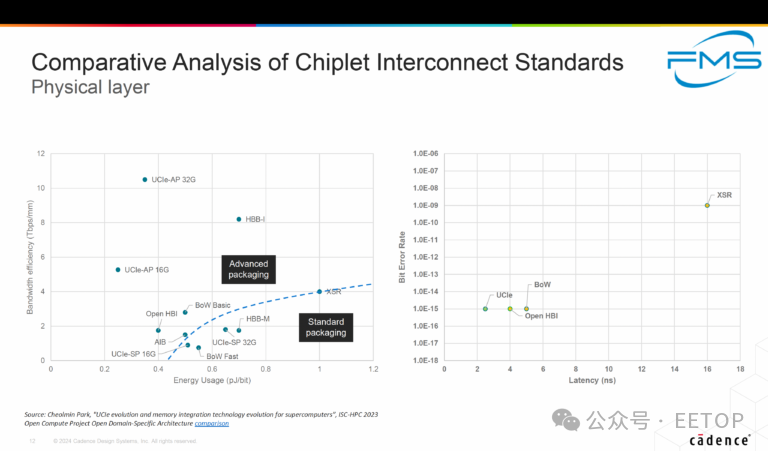

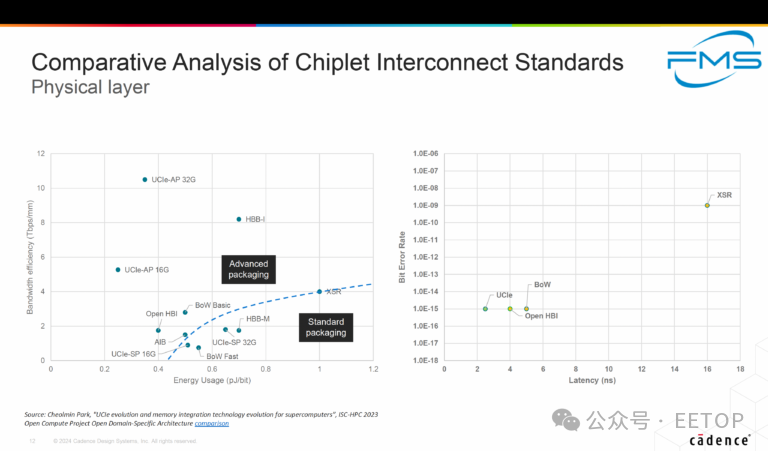

对这些不同标准的比较分析表明,在带宽效率、能源使用效率和延迟方面,UCIe表现出色。

UCIe在Chiplet设计中的作用

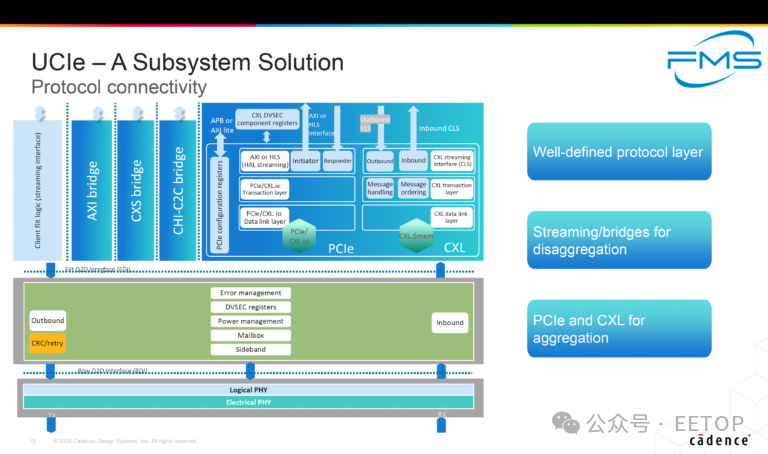

UCIe 或 Universal Chiplet Interconnect Express 是一种开放的行业标准,它定义了用于连接小芯片的高带宽、低延迟互连协议。UCIe 为 chiplets 提供了一个用于通信的通用接口,就像 PC 行业中 USB 标准化外设连接的方式一样。

借助 UCIe,公司可以混合和匹配来自不同供应商的小芯片,从而促进更具竞争力的市场并推动创新。它使设计人员能够专注于核心创新和高度定制的内核,并利用外设的标准化接口。通过将高度定制的内核与标准外设围绕在一起,设计人员可以最大限度地提高其市场覆盖范围和效率。实现专业化和定制化解决方案

UCIe实现的最令人兴奋的可能性之一是高度专业化和定制化解决方案的潜力。过去,公司不得不依赖昂贵的单片 SoC,或者求助于可能并不完全适合其特定应用的通用 SoC。借助小芯片和 UCIe,公司可以根据自己的确切需求构建定制系统,从各种供应商中选择最佳组件。例如,一家开发 AI 加速器的公司可以从一个供应商那里选择高性能 CPU 小芯片,从另一个供应商那里选择一个专用神经处理单元 (NPU),从第三个供应商那里选择内存。UCIe 确保这些组件能够有效通信,使公司能够创建高度优化的解决方案,而无需昂贵的单片定制 SoC。面向 AI 应用的定制芯片

由于需要针对特定 AI 应用(如训练、推理、数据挖掘和图形分析)优化硬件,对定制芯片的需求正在迅速增加。AI 训练需要高性能的并行处理能力来管理大型数据集和复杂模型,而 AI 推理需要低延迟、高吞吐量的处理以实现实时预测和决策。数据挖掘受益于为特定数据处理和提取任务量身定制的定制芯片,而图形分析需要设计用于处理图形处理复杂性和大规模并行性的芯片。利用 UCIe 的基于 chiplet 的方法在性能、电源效率和可扩展性方面为这些应用提供了显著的优势。促进创新与协作

作为一个开放的行业标准,UCIe不仅降低了进入壁垒,而且还鼓励了半导体行业内部的合作和创新。通过建立小芯片通信的通用平台,UCIe使公司能够专注于其核心竞争力,无论是开发尖端处理器、先进的内存技术还是专用加速器。这种协作环境可以促进开发新的创新产品,而这些产品在传统 SoC 设计的限制下可能无法实现。随着越来越多的公司采用UCIe并为生态系统做出贡献,可用小芯片的种类和质量将继续增长,从而进一步推动创新。总结

UCIe代表了小芯片设计发展向前迈出的重要一步,降低了各种规模公司的进入门槛。通过标准化小芯片之间的通信,UCIe 使公司能够更轻松地开发定制的高性能系统,而无需昂贵且复杂的 SoC 设计。因此,UCIe有望使半导体行业民主化,促进更大的创新和竞争,同时实现新一轮的专业化和定制解决方案。芯片设计的未来是模块化的,有了UCIe,这个未来比以往任何时候都更容易实现。对用于 AI 应用的定制芯片的需求不断增长,将推动 UCIe 技术的进一步发展和机遇。

本文由EETOP编译自semiwiki

5折优惠即将结束

(本课提供在线答疑,购课后课添加微信:ssywtt 拉你入群)