----追光逐电 光赢未来----

01

——

芯片制作流程

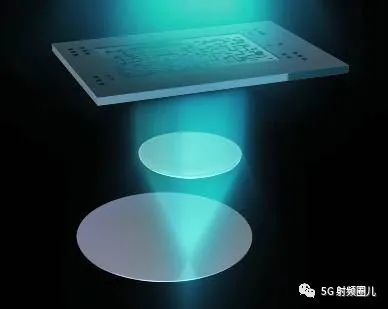

芯片制作完整过程包括:芯片设计、晶片制作、封装制作、成本测试等几个环节,其中晶片片制作过程尤为的复杂。下面图示让我们共同来了解一下芯片制作的过程,尤其是晶片制作部分。首先是芯片设计,根据设计的需求,生成的“图样”

1,芯片的原料晶圆,晶圆的成分是硅,硅是由石英沙所精练出来的,晶圆便是硅元素加以纯化(99.999%),接着是将些纯硅制成硅晶棒,成为制造集成电路的石英半导体的材料,将其切片就是芯片制作具体需要的晶圆。晶圆越薄,成产的成本越低,但对工艺就要求的越高。

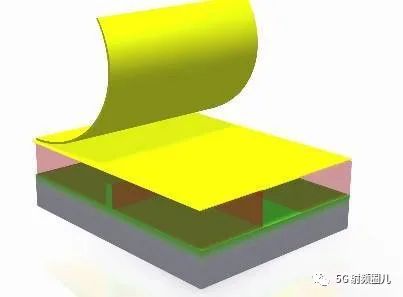

2,晶圆涂膜晶圆涂膜能抵抗氧化以及耐温能力,其材料为光阻的一种。

3,晶圆光刻显影、蚀刻该过程使用了对紫外光敏感的化学物质,即遇紫外光则变软。通过控制遮光物的位置可以得到芯片的外形。在硅晶片涂上光致抗蚀剂,使得其遇紫外光就会溶解。这是可以用上第一份遮光物,使得紫外光直射的部分被溶解,这溶解部分接着可用溶剂将其冲走。这样剩下的部分就与遮光物的形状一样了,而这效果正是我们所要的。这样就得到我们所需要的二氧化硅层。

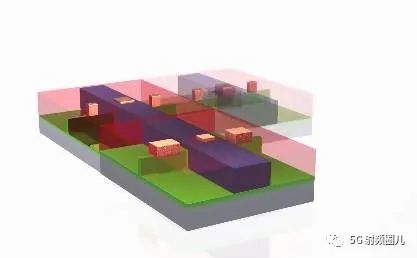

4、搀加杂质将晶圆中植入离子,生成相应的P、N类半导体。具体工艺是是从硅片上暴露的区域开始,放入化学离子混合液中。这一工艺将改变搀杂区的导电方式,使每个晶体管可以通、断、或携带数据。简单的芯片可以只用一层,但复杂的芯片通常有很多层,这时候将这一流程不断的重复,不同层可通过开启窗口联接起来。这一点类似所层PCB板的制作制作原理。更为复杂的芯片可能需要多个二氧化硅层,这时候通过重复光刻以及上面流程来实现,形成一个立体的结构。

5、晶圆测试经过上面的几道工艺之后,晶圆上就形成了一个个格状的晶粒。通过针测的方式对每个晶粒进行电气特性检测。一般每个芯片的拥有的晶粒数量是庞大的,组织一次针测试模式是非常复杂的过程,这要求了在生产的时候尽量是同等芯片规格构造的型号的大批量的生产。数量越大相对成本就会越低,这也是为什么主流芯片器件造价低的一个因素。

6、封装将制造完成晶圆固定,绑定引脚,按照需求去制作成各种不同的封装形式,这就是同种芯片内核可以有不同的封装形式的原因。比如:DIP、QFP、PLCC、QFN 等等。这里主要是由用户的应用习惯、应用环境、市场形式等外围因素来决定的。

7、芯片制造的最后一道工序为测试,其又可分为一般测试和特殊测试,前者是将封装后的芯片置于各种环境下测试其电气特性,如消耗功率、运行速度、耐压度等。经测试后的芯片,依其电气特性划分为不同等级。而特殊测试则是根据客户特殊需求的技术参数,从相近参数规格、品种中拿出部分芯片,做有针对性的专门测试,看是否能满足客户的特殊需求,以决定是否须为客户设计专用芯片。经一般测试合格的产品贴上规格、型号及出厂日期等标识的标签并加以包装后即可出厂。而未通过测试的芯片则视其达到的参数情况定作降级品或废品。

02

——

芯片制作流程分解说明

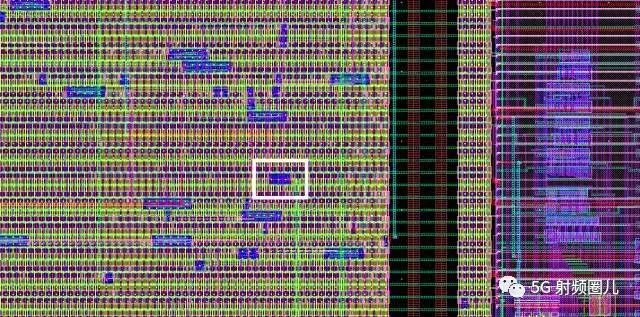

那么要想造个芯片,首先,你得画出来一个长这样的玩意儿给Foundry (外包的晶圆制造公司)▼

再放大▼

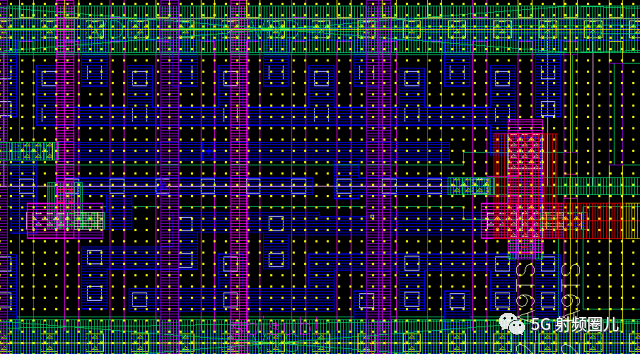

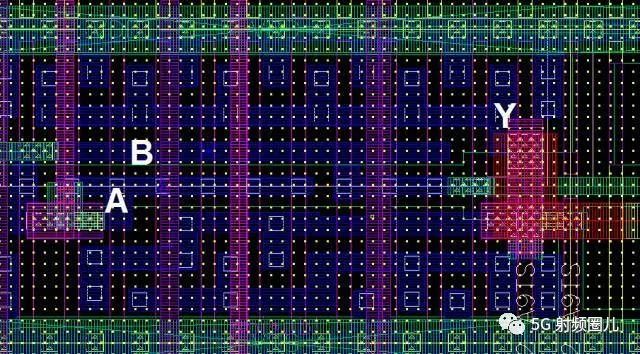

我们终于看到一个门电路啦! 这是一个NAND Gate(与非门),大概是这样▼

A, B 是输入, Y是输出

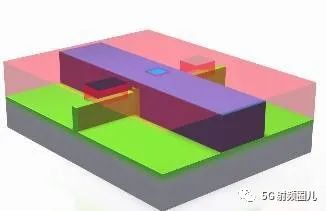

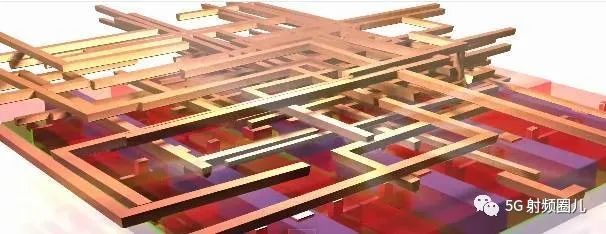

其中蓝色的是金属1层,绿色是金属2层,紫色是金属3层,粉色是金属4层。那晶体管(“晶体管”自199X年以后已经主要是 MOSFET, 即场效应管了 ) 呢?仔细看图,看到里面那些白色的点吗?那是衬底,还有一些绿色的边框?那些是Active Layer (也即掺杂层)。

Foundry是怎么做的呢? 大体上分为以下几步:

首先搞到一块圆圆的硅晶圆, (就是一大块晶体硅, 打磨的很光滑, 一般是圆的)

图片按照生产步骤排列. 但是步骤总结单独写出.

1、湿洗 (用各种试剂保持硅晶圆表面没有杂质)

2、光刻 (用紫外线透过蒙版照射硅晶圆, 被照到的地方就会容易被洗掉, 没被照到的地方就保持原样. 于是就可以在硅晶圆上面刻出想要的图案. 注意, 此时还没有加入杂质, 依然是一个硅晶圆. )

3、 离子注入 (在硅晶圆不同的位置加入不同的杂质, 不同杂质根据浓度/位置的不同就组成了场效应管.)

4.1、干蚀刻 (之前用光刻出来的形状有许多其实不是我们需要的,而是为了离子注入而蚀刻的。现在就要用等离子体把他们洗掉,或者是一些第一步光刻先不需要刻出来的结构,这一步进行蚀刻).

4.2、湿蚀刻 (进一步洗掉,但是用的是试剂, 所以叫湿蚀刻)—— 以上步骤完成后, 场效应管就已经被做出来啦,但是以上步骤一般都不止做一次, 很可能需要反反复复的做,以达到要求。

5、等离子冲洗 (用较弱的等离子束轰击整个芯片)

6、热处理,其中又分为:

6.1 快速热退火 (就是瞬间把整个片子通过大功率灯啥的照到1200摄氏度以上, 然后慢慢地冷却下来, 为了使得注入的离子能更好的被启动以及热氧化)

6.2 退火

6.3 热氧化 (制造出二氧化硅, 也即场效应管的栅极(gate) )

7、化学气相淀积(CVD),进一步精细处理表面的各种物质

8、物理气相淀积 (PVD),类似,而且可以给敏感部件加coating

9、分子束外延 (MBE) 如果需要长单晶的话就需要。

10、电镀处理

11、化学/机械表面处理

12、晶圆测试

13、晶圆打磨就可以出厂封装了。

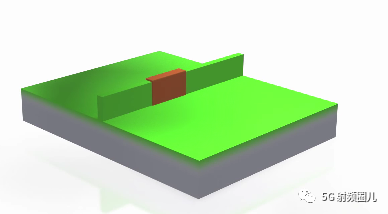

再通过图示来一步步看▼

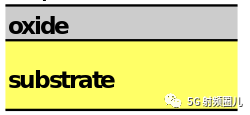

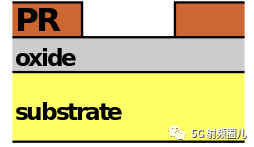

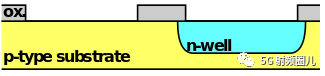

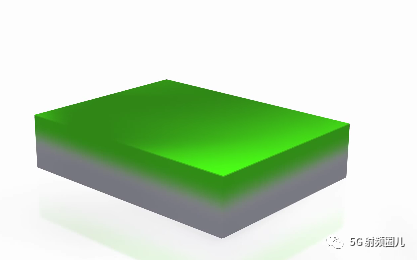

1、上面是氧化层, 下面是衬底(硅)——湿洗

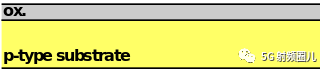

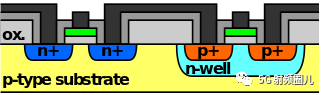

2、一般来说, 先对整个衬底注入少量(10^10 ~ 10^13 / cm^3) 的P型物质(最外层少一个电子),作为衬底——离子注入

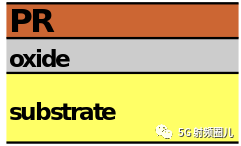

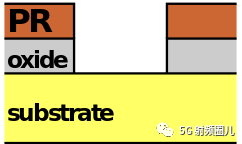

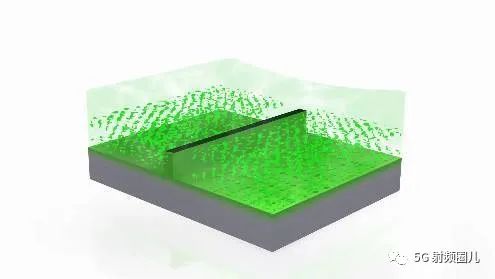

3、先加入Photo-resist, 保护住不想被蚀刻的地方——光刻

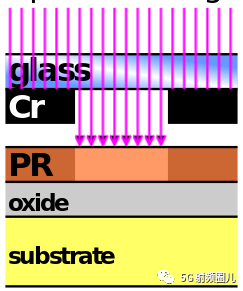

4、上掩膜!(就是那个标注Cr的地方。中间空的表示没有遮盖,黑的表示遮住了。) —— 光刻

5、紫外线照上去,下面被照得那一块就被反应了——光刻

6、撤去掩膜——光刻

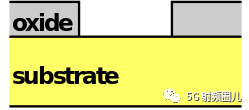

7、把暴露出来的氧化层洗掉, 露出硅层(就可以注入离子了)——光刻

8、把保护层撤去. 这样就得到了一个准备注入的硅片. 这一步会反复在硅片上进行(几十次甚至上百次)——光刻

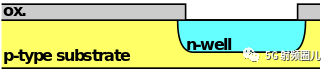

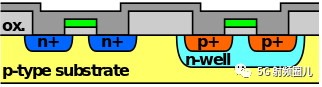

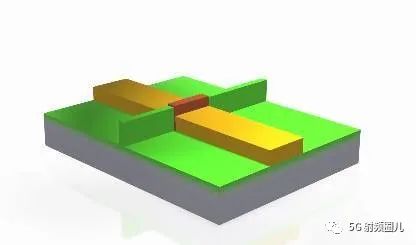

9、然后光刻完毕后, 往里面狠狠地插入一块少量(10^14 ~ 10^16 /cm^3) 注入的N型物质就做成了一个N-well (N-井)——离子注入

10、用干蚀刻把需要P-well的地方也蚀刻出来,也可以再次使用光刻刻出来——干蚀刻

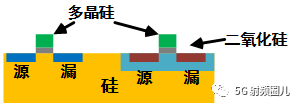

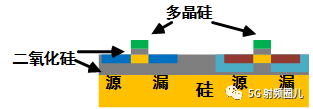

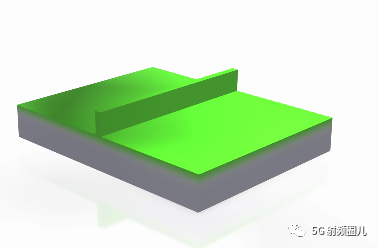

11、上图将P-型半导体上部再次氧化出一层薄薄的二氧化硅—— 热处理

12、用分子束外延处理长出的一层多晶硅,该层可导电——分子束外延

13、进一步的蚀刻,做出精细的结构。(在退火以及部分CVD)—— 重复3-8光刻 + 湿蚀刻

14、再次狠狠地插入大量(10^18 ~ 10^20 / cm^3) 注入的P/N型物质,此时注意MOSFET已经基本成型——离子注入

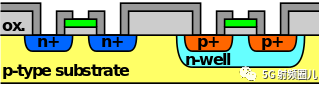

15、用气相积淀 形成的氮化物层 —— 化学气相积淀

16、将氮化物蚀刻出沟道——光刻 + 湿蚀刻

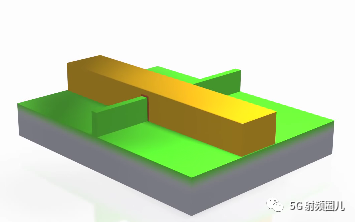

17、物理气相积淀长出 金属层——物理气相积淀

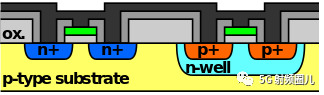

18、将多余金属层蚀刻。光刻 + 湿蚀刻重复 17-18 次长出每个金属层。

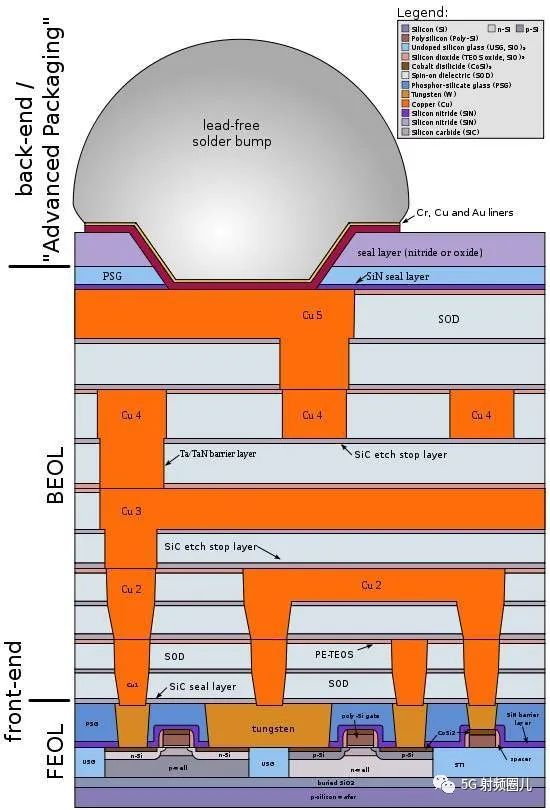

附图的步骤在每幅图的下面标注,一共18步。

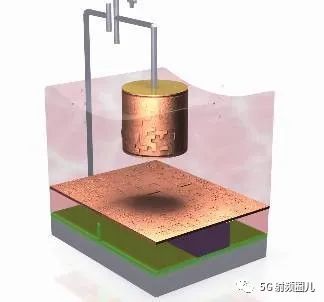

最终成型大概长这样:

其中,步骤1-15 属于 前端处理 (FEOL),也即如何做出场效应管。步骤16-18 (加上许许多多的重复) 属于后端处理 (BEOL),后端处理主要是用来布线。最开始那个大芯片里面能看到的基本都是布线!一般一个高度集中的芯片上几乎看不见底层的硅片,都会被布线遮挡住。

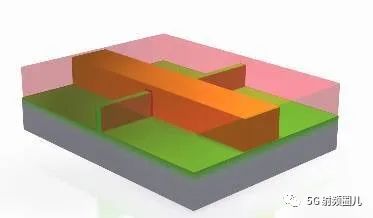

SOI (Silicon-on-Insulator) 技术:

传统CMOS技术的缺陷在于:衬底的厚度会影响片上的寄生电容,间接导致芯片的性能下降。SOI技术主要是将 源极/漏极 和 硅片衬底分开,以达到(部分)消除寄生电容的目的。

传统:

SOI:

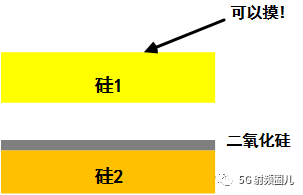

制作方法主要有以下几种(主要在于制作硅-二氧化硅-硅的结构,之后的步骤跟传统工艺基本一致。)

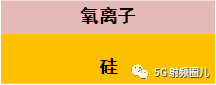

1. 高温氧化退火:

在硅表面离子注入一层氧离子层

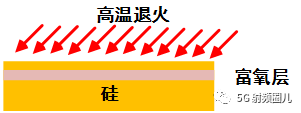

等氧离子渗入硅层, 形成富氧层

高温退火

成型

或者是

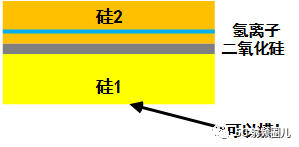

2. Wafer Bonding(用两块! )不是要做夹心饼干一样的结构吗? 爷不差钱! 来两块!

对硅2进行表面氧化

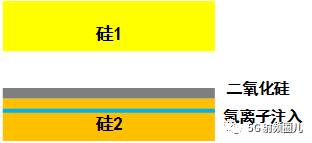

对硅2进行氢离子注入对硅2进行氢离子注入

翻面

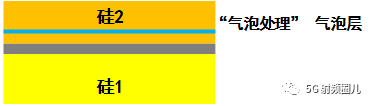

将氢离子层处理成气泡层将氢离子层处理成气泡层

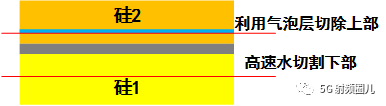

切割掉多余部分切割掉多余部分

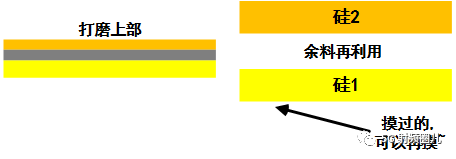

成型 + 再利用

光刻

离子注入离子注入

微观图长这样:

再次光刻+蚀刻

撤去保护, 中间那个就是Fin撤去保护, 中间那个就是Fin

门部位的多晶硅/高K介质生长门部位的多晶硅/高K介质生长

门部位的氧化层生长门部位的氧化层生长

长成这样

源极 漏极制作(光刻+ 离子注入)

初层金属/多晶硅贴片

蚀刻+成型

物理气相积淀长出表面金属层(因为是三维结构, 所有连线要在上部连出)

机械打磨(对! 不打磨会导致金属层厚度不一致)

成型! 成型!

03

——

芯片封装

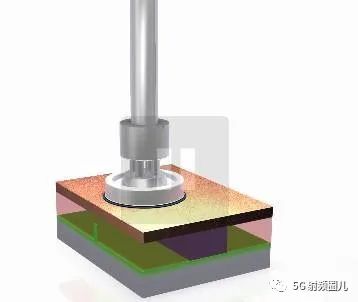

封装,就是指把硅片上的电路管脚,用导线接引到外部接头处,以便与其它器件连接.封装形式是指安装半导体集成电路芯片用的外壳。它不仅起着安装、固定、密封、保护芯片及增强电热性能等方面的作用,而且还通过芯片上的接点用导线连接到封装外壳的引脚上,这些引脚又通过印刷电路板上的导线与其他器件相连接,从而实现内部芯片与外部电路的连接。

芯片为什么要封装?

一方面因为芯片必须与外界隔离,以防止空气中的杂质对芯片电路的腐蚀而造成电气性能下降。另一方面,封装后的芯片也更便于安装和运输。由于封装技术的好坏还直接影响到芯片自身性能的发挥和与之连接的PCB(印制电路板)的设计和制造,因此它是至关重要的。

衡量一个芯片封装技术先进与否的重要指标是芯片面积与封装面积之比,这个比值越接近1越好。封装时主要考虑的因素:

1、 芯片面积与封装面积之比为提高封装效率,尽量接近1:1;

2、 引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能;

3、 基于散热的要求,封装越薄越好。

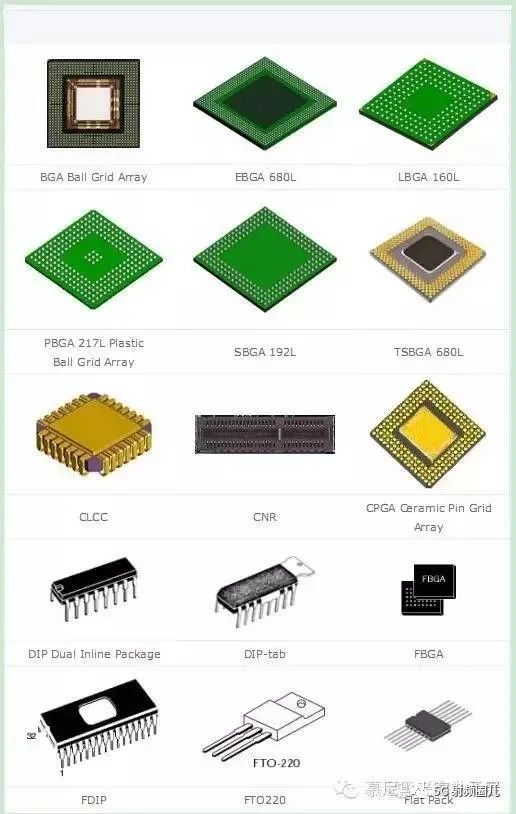

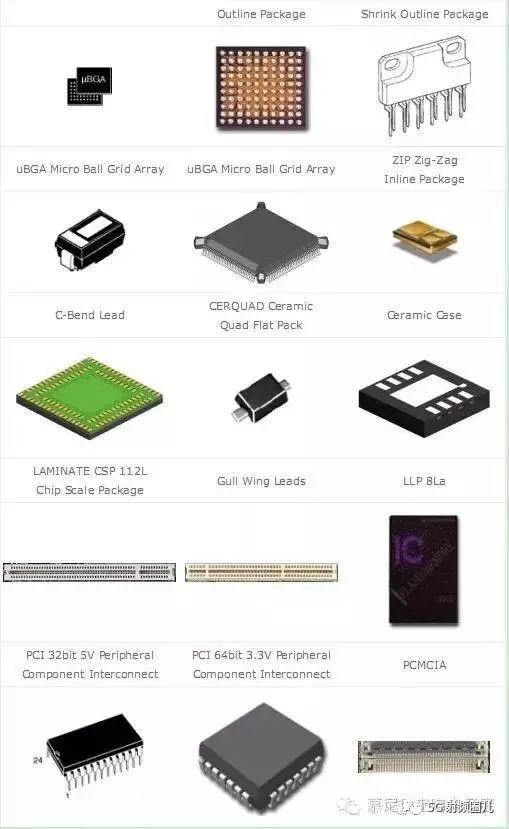

封装主要分为DIP双列直插和SMD贴片封装两种。从结构方面,封装经历了最早期的晶体管TO(如TO-89、TO92)封装发展到了双列直插封装,随后由PHILIP公司开发出了SOP小外型封装,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。从材料介质方面,包括金属、陶瓷、塑料、塑料,目前很多高强度工作条件需求的电路如军工和宇航级别仍有大量的金属封装。

封装大致经过了如下发展进程:

结构方面:TO->DIP->PLCC->QFP->BGA ->CSP;

材料方面:金属、陶瓷->陶瓷、塑料->塑料;

引脚形状:长引线直插->短引线或无引线贴装->球状凸点;

装配方式:通孔插装->表面组装->直接安装

具体的封装形式

1、 SOP/SOIC封装

SOP是英文Small Outline Package 的缩写,即小外形封装。SOP封装技术由1968~1969年菲利浦公司开发成功,以后逐渐派生出SOJ(J型引脚小外形封装)、TSOP(薄小外形封装)、VSOP(甚小外形封装)、SSOP(缩小型SOP)、TSSOP(薄的缩小型SOP)及SOT(小外形晶体管)、SOIC(小外形集成电路)等。

2、 DIP封装

DIP是英文 Double In-line Package的缩写,即双列直插式封装。插装型封装之一,引脚从封装两侧引出,封装材料有塑料和陶瓷两种。DIP是最普及的插装型封装,应用范围包括标准逻辑IC,存贮器LSI,微机电路等。

3、 PLCC封装

PLCC是英文Plastic Leaded Chip Carrier 的缩写,即塑封J引线芯片封装。PLCC封装方式,外形呈正方形,32脚封装,四周都有管脚,外形尺寸比DIP封装小得多。PLCC封装适合用SMT表面安装技术在PCB上安装布线,具有外形尺寸小、可靠性高的优点。

4、 TQFP封装

TQFP是英文thin quad flat package的缩写,即薄塑封四角扁平封装。四边扁平封装(TQFP)工艺能有效利用空间,从而降低对印刷电路板空间大小的要求。由于缩小了高度和体积,这种封装工艺非常适合对空间要求较高的应用,如 PCMCIA 卡和网络器件。几乎所有ALTERA的CPLD/FPGA都有 TQFP 封装。

5、 PQFP封装

PQFP是英文Plastic Quad Flat Package的缩写,即塑封四角扁平封装。PQFP封装的芯片引脚之间距离很小,管脚很细,一般大规模或超大规模集成电路采用这种封装形式,其引脚数一般都在100以上。

6、 TSOP封装

TSOP是英文Thin Small Outline Package的缩写,即薄型小尺寸封装。TSOP内存封装技术的一个典型特征就是在封装芯片的周围做出引脚, TSOP适合用SMT技术(表面安装技术)在PCB(印制电路板)上安装布线。TSOP封装外形尺寸时,寄生参数(电流大幅度变化时,引起输出电压扰动) 减小,适合高频应用,操作比较方便,可靠性也比较高。

7、 BGA封装

BGA是英文Ball Grid Array Package的缩写,即球栅阵列封装。20世纪90年代随着技术的进步,芯片集成度不断提高,I/O引脚数急剧增加,功耗也随之增大,对集成电路封装的要求也更加严格。为了满足发展的需要,BGA封装开始被应用于生产。

采用BGA技术封装的内存,可以使内存在体积不变的情况下内存容量提高两到三倍,BGA与TSOP相比,具有更小的体积,更好的散热性能和电性能。BGA封装技术使每平方英寸的存储量有了很大提升,采用BGA封装技术的内存产品在相同容量下,体积只有TSOP封装的三分之一;另外,与传统TSOP封装方式相比,BGA封装方式有更加快速和有效的散热途径。

BGA封装的I/O端子以圆形或柱状焊点按阵列形式分布在封装下面,BGA技术的优点是I/O引脚数虽然增加了,但引脚间距并没有减小反而增加了,从而提高了组装成品率;虽然它的功耗增加,但BGA能用可控塌陷芯片法焊接,从而可以改善它的电热性能;厚度和重量都较以前的封装技术有所减少;寄生参数减小,信号传输延迟小,使用频率大大提高;组装可用共面焊接,可靠性高。

说到BGA封装就不能不提Kingmax公司的专利TinyBGA技术,TinyBGA英文全称为Tiny Ball Grid Array(小型球栅阵列封装),属于是BGA封装技术的一个分支。是Kingmax公司于1998年8月开发成功的,其芯片面积与封装面积之比不小于1:1.14,可以使内存在体积不变的情况下内存容量提高2~3倍,与TSOP封装产品相比,其具有更小的体积、更好的散热性能和电性能。

采用TinyBGA封装技术的内存产品在相同容量情况下体积只有TSOP封装的1/3。TSOP封装内存的引脚是由芯片四周引出的,而TinyBGA则是由芯片中心方向引出。这种方式有效地缩短了信号的传导距离,信号传输线的长度仅是传统的TSOP技术的1/4,因此信号的衰减也随之减少。这样不仅大幅提升了芯片的抗干扰、抗噪性能,而且提高了电性能。采用TinyBGA封装芯片可抗高达300MHz的外频,而采用传统TSOP封装技术最高只可抗150MHz的外频。

TinyBGA封装的内存其厚度也更薄(封装高度小于0.8mm),从金属基板到散热体的有效散热路径仅有0.36mm。因此,TinyBGA内存拥有更高的热传导效率,非常适用于长时间运行的系统,稳定性极佳。

国际部分品牌产品的封装命名规则资料

1、 MAXIM

MAXIM前缀是“MAX”。DALLAS则是以“DS”开头。MAX×××或MAX××××

说明:

1.后缀CSA、CWA 其中C表示普通级,S表示表贴,W表示宽体表贴。

2.后缀CWI表示宽体表贴,EEWI宽体工业级表贴,后缀MJA或883为军级。

3.CPA、BCPI、BCPP、CPP、CCPP、CPE、CPD、ACPA后缀均为普通双列直插。

举例MAX202CPE、CPE普通ECPE普通带抗静电保护

MAX202EEPE 工业级抗静电保护(-45℃-85℃),说明E指抗静电保护MAXIM数字排列分类

1字头 模拟器;

2字头 滤波器 ;

3字头 多路开关 ;

4字头 放大器 ;

5字头 数模转换器 ;

6字头 电压基准 ;

7字头 电压转换 ;

8字头 复位器 ;

9字头 比较器 ;

DALLAS命名规则

例如DS1210N.S. DS1225Y-100IND

N=工业级 S=表贴宽体 MCG=DIP封 Z=表贴宽体 MNG=DIP工业级 ;

IND=工业级 QCG=PLCC封 Q=QFP ;

2、 ADI

AD产品以“AD”、“ADV”居多,也有“OP”或者“REF”、“AMP”、“SMP”、“SSM”、“TMP”、“TMS”等开头的。

后缀的说明:

1. 后缀中J表示民品(0-70℃),N表示普通塑封,后缀中带R表示表示表贴。

2.后缀中带D或Q的表示陶封,工业级(45℃-85℃)。后缀中H表示圆帽。

3.后缀中SD或883属军品。

例如:JN DIP封装 JR表贴 JD DIP陶封

3、 BB

BB产品命名规则:

前缀ADS模拟器件 后缀U表贴 P是DIP封装 带B表示工业级 前缀INA、XTR、PGA等表示高精度运放 后缀U表贴 P代表DIP PA表示高精度

4、 INTEL

INTEL产品命名规则:

N80C196系列都是单片机;

前缀:N=PLCC封装 T=工业级 S=TQFP封装 P=DIP封装 ;

KC20主频 KB主频 MC代表84引角 ;

举例:TE28F640J3A-120 闪存 TE=TSOP DA=SSOP E=TSOP。

5、 ISSI

以“IS”开头

比如:IS61C IS61LV 4×表示DRAM 6×表示SRAM 9×表示EEPROM ;

封装:PL=PLCC PQ=PQFP T=TSOP TQ=TQFP ;

6、 LINEAR

以产品名称为前缀

LTC1051CS CS表示表贴 ;

LTC1051CN8 **表示*IP封装 8脚 ;

后缀C为民用级 I为工业级 后面数字表示引脚数量!

7、 IDT

IDT的产品一般都是IDT开头的

后缀的说明:

1. 后缀中TP属窄体DIP

2. 后缀中P 属宽体DIP

3. 后缀中J 属PLCC

比如:IDT7134SA55P 是DIP封装

IDT7132SA55J 是PLCC

IDT7206L25TP 是DIP

8、 NS

NS的产品部分以LM 、LF开头的

LM324N 3字头代表民品 带N圆帽 ;

LM224N 2字头代表工业级 带N塑封 ;

LM124J 1字头代表军品 带J陶封 ;

9、 HYNIX

封装:DP代表DIP封装 DG代表SOP封装 DT代表TSOP封装。

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

联系邮箱:uestcwxd@126.com

QQ:493826566