来源:EETOP Blog 作者:mervin_li

链接:https://blog.eetop.cn/1582944

众所周知,芯片项目是一个复杂的系统工程,每个环节都可能对最终的交付产生重要的影响。经验看来,好的项目管理包含资源调配,风险预估,过程把控和交付验收等重要环节。这几点如何做到独立又统一呢?check list、action item等过程管理和验收标准的制定和持续跟进,就可以打造一个简单高效的规范流程。把流程制度化,标准化,可以很大程度上避免人为的失误。

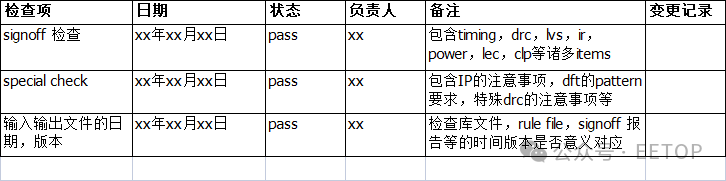

通常,交付前会有一个signoff的标准,保证每一项检查都达标。主要包括但不限于timing clean;drc clean,lvs pass。当然每一项大的signoff检查要求下,还会细分诸多细节的检查,case by case,因此需要在前期就开始研讨,规划,敲定这一系列标准。例如,timing clean,不仅仅包含setup,hold的clean,还包括drv(max trans,load, min period, min pulse width等)的clean,data check,max delay,clock cell的VT类型,特殊路径的skew,以及其他的special check等。drc,lvs也一样,很多大型芯片还需要严格通过erc检查,perc检查等等。当然,功耗,IR,clp,formal/lec等等。这些都需要一个系统的表格来跟进,时间,日期,状态,负责人等。这是验收的标准检查。

那么,在验收前夕,我们为了避免验收时出现效率低下,返工等问题,需要提前做好check list的review。那么制定这个check list的item就很有讲究了。可以在项目后期就定期进行更新,保持数据和时间的一致性。那么,本着能够更好的帮助交付验收,我们的check list通常包含哪些内容呢?简单归纳,三大部分,1,signoff 标准的预验收;2,special check的检查;3,文件日期,版本的确认

大型项目的模块众多,每个owner需要严格确保自己的部分等风险可控。因此有必要持续的进行过程把控,风险预警。因此,这个check list不仅仅是在交付前去对照,在项目中期就可以持续更新,跟进,从而避免人为的疏忽造成项目延期等问题。

项目初期,就需要规划schedule,管理项目资源,也可以独立制成表格。项目过程中制定action item list,时刻对齐进度,预警风险。项目后期,检查check list,确保文件无误。项目收尾,检查各个signoff item,确保交付验收顺利通过。

实践出真知,与诸君共勉。

作者更多精彩日志截屏:

欢迎大家访问作者博客

觉得有帮助可以关注并点赞支持作者

(第一次注册需要在电脑端进行)

点击阅读原文访问作者博客