了解半导体器件的故障模式是创建筛选、鉴定和可靠性测试的关键,这些测试可以确保器件在数据表规定的范围内运行,并满足汽车和其他电源转换应用中要求的越来越严格的十亿分之一故障率。

时间相关的介电击穿测试,通常在加速条件下对处于恒定应力下的电容器进行,以得出额定条件下时间曲线中的故障

高温栅极偏置鉴定,在封装器件上进行,在最大栅极和温度规格下具有恒定栅极偏置,漏源电压 (V DS ) 为 0 V

在恒定偏置下进行的偏置温度不稳定性 (BTI) 可靠性测试

在直流偏置条件下,SiC MOSFET 中的V th漂移通常大于硅 MOSFET 中的 V th 漂移。此外,许多努力都旨在测试器件通常切换的特定应用条件下的这种偏移。这些开关瞬变可能导致栅极源电压 (V GS ) 的过冲/下冲,而这取决于多种因素,例如开启和关闭转换速率、内部器件电容以及可能设计入的外部组件(例如栅极电阻)或寄生参数(例如键合线电感)。已经提出了 GSS 测试,其中栅极在器件的最高指定温度下经受重复的开关循环,其中 V DS为 0 V。此测试现已成为JEDEC JEP195 指南的一部分。

对GSS行为的研究表明:

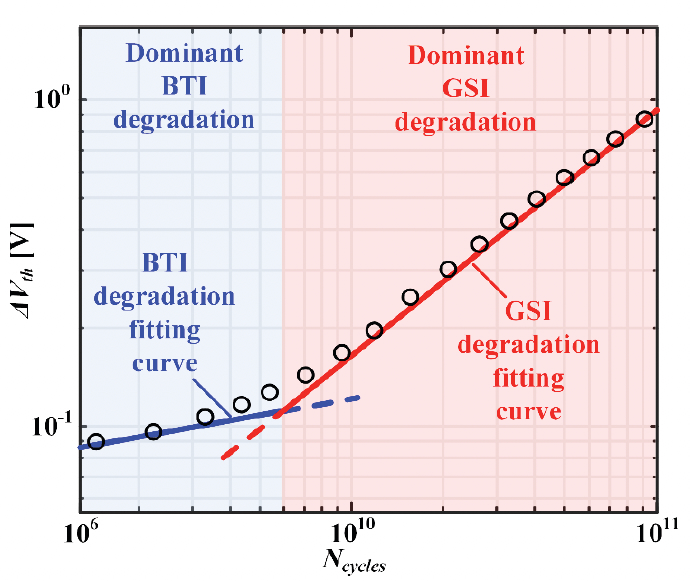

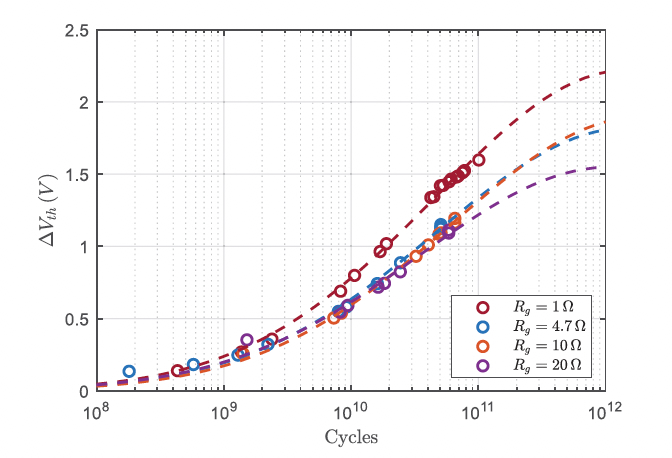

交流循环引起的 V th漂移取决于开关周期数(N周期),可表示为 ∆ V th = A o × N周期n,其中指数n是变化的。

当循环次数低于约 10 7 N时,性能退化遵循常数n ≈ 0.16,这通常在 DC-BTI 应力下表现出来。

超过 10 8 N循环后,n增加至 ≈ 0.32,这是直流应力下未见的行为。图 1 显示了此变化的表示。

图 1:GSS 测试下 SiC MOSFET 中的 V th偏移(来源:Gómez 等人,2024 年)

图 1:GSS 测试下 SiC MOSFET 中的 V th偏移(来源:Gómez 等人,2024 年)

应力时间长于 ≈ 1e11 N个周期显示出饱和的较低偏移率,其中n ≈ 0.1。

V th偏移在很大程度上取决于最大和最小 V GS开关电平,V GS_low值越负,偏移越强。通常建议使用负 V GS来关闭 SiC MOSFET,尤其是在硬开关条件下,以最大限度地降低米勒电容耦合导致误开启的风险,并最大限度地减少开关损耗。

与 DC-BTI 应力不同的是,GSS 引起的V th偏移很大程度上是不可恢复的。

从测量角度来看,高频测试可确保在合理的时间范围内实现足够多的循环次数,同时仍能观察到 GSS 偏移。例如,500 kHz 开关可在 1,000 小时内实现超过 1e12 个循环。

在某些应用中,例如太阳能逆变器,这可能不足以模拟预期的 20 年使用寿命,但随后可以合理地使用推断。2一旦将零件从应力炉中卸下,非恢复特性也使执行原位 V th测量变得更加容易。

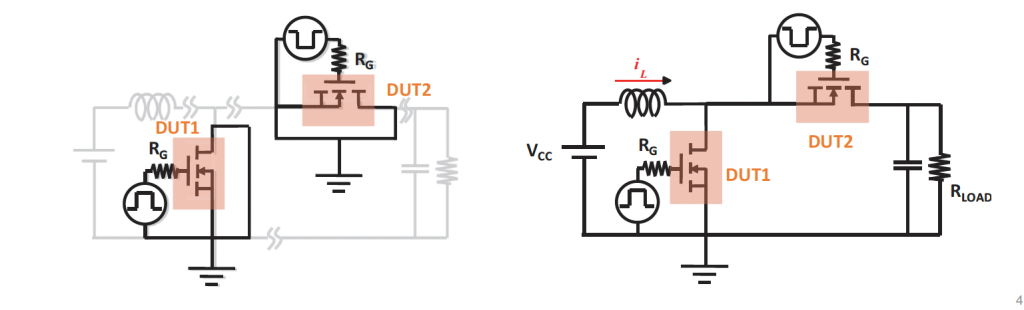

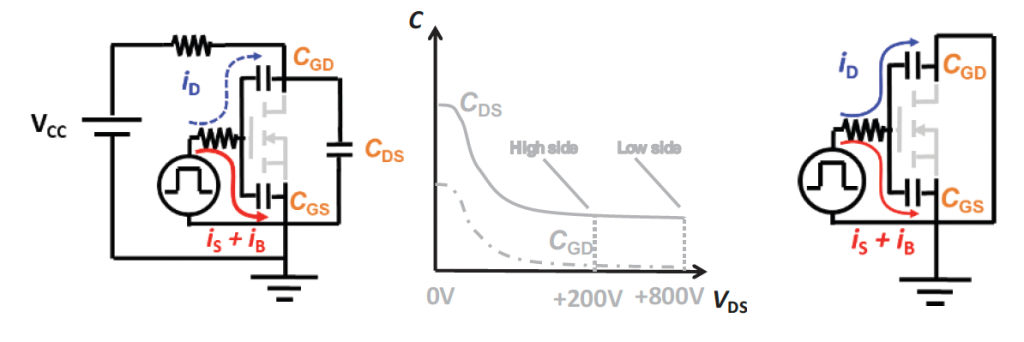

出现的一个重要问题是 GSS 测试是否准确反映了应用切换应力 (ASS) 下的压力。Gómez 等人尝试使用图 2 中所示的测试设置来回答这个问题。ASS 配置为升压转换器,但其他类似设置可用于规范其他测试条件,尤其是栅极驱动。

图 2:GSS(左)和 ASS(右)的测试设置(来源:Gómez 等人,2024 年)

图 2:GSS(左)和 ASS(右)的测试设置(来源:Gómez 等人,2024 年)

所用器件为额定电压为 1,200 V 的 SiC MOSFET。测试所用的一些条件如下:

开关频率 = 100 kHz

V GS_high = 18V,V GS_low = –8V

栅极电阻(R G) = 4.7 Ω

对于 ASS,V cc = 400 V,负载电流 (i L ) 为 1.2 A,∆i L (峰峰值) 为 1.6 A

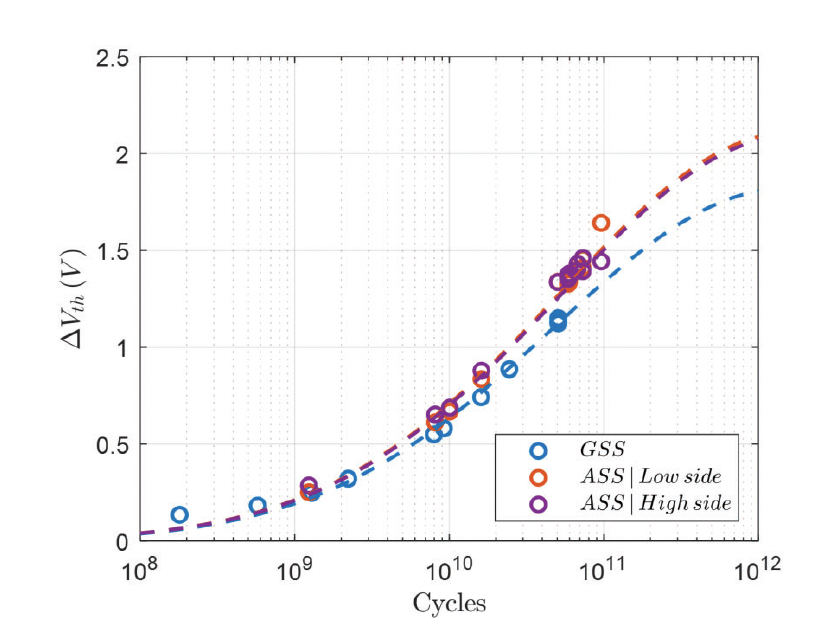

定期进行非原位 V th测量。图 3 显示了每种情况下观察到的偏移结果。

图 3:GSS 和 ASS 应力引起的 V th偏移(来源:Gómez 等人,2024 年)

图 3:GSS 和 ASS 应力引起的 V th偏移(来源:Gómez 等人,2024 年)

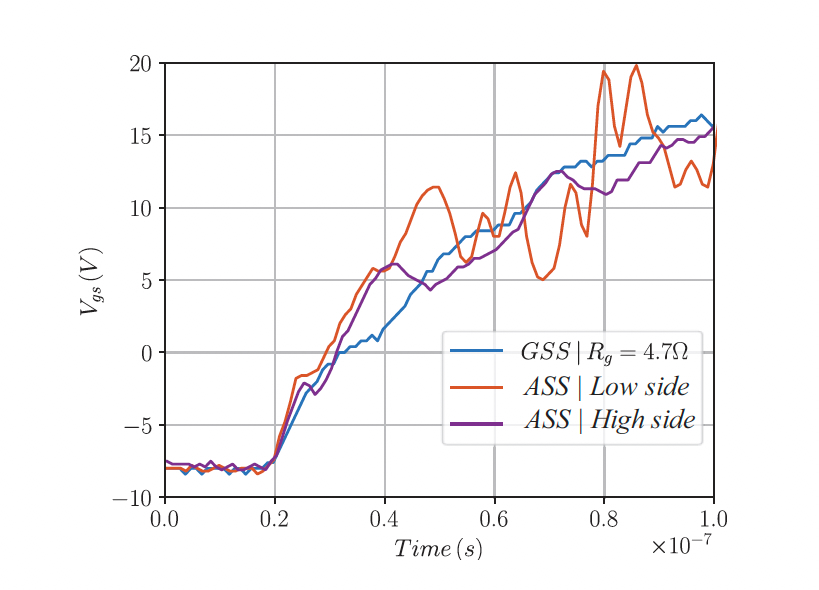

受到 ASS 影响的 DUT 表现出更大的 V th偏移,升压转换器中使用的低侧和高侧 DUT 显示出类似的趋势。为了确定原因,作者检查了栅极开关波形并进行了模拟。开启波形如图 4 所示。虽然 10% 到 90% 的开关时间看起来相当,但 ASS 期间的最大 dV GS /dt 斜率更高,并表现出更多的振荡行为。

图 4:GSS 和 ASS 期间的栅极导通波形(来源:Gómez 等人,2024 年)

图 4:GSS 和 ASS 期间的栅极导通波形(来源:Gómez 等人,2024 年)

在这些测试期间,电容充电和放电产生的内部瞬态电流分布在低于 V th 的范围内有所不同,这被怀疑是 V th偏移差异的原因。MOSFET 的米勒栅极漏极电容 (C GD ) 和输出电容 (C DS ) 是 V DS电压的函数。这在图 5 中进行了描述,其中还显示了这些电流。

在 GSS 测试中,V DS为 0 V。从 V DS开关瞬变中 C GD路径电流的影响的基本推导可得出:

∆VGS =( 1 ÷(1+(CGS ÷ CGD )))× ∆VDS

这可以解释两次测量之间瞬态最大 dV GS /dt的差异。实际上,进行 GSS 可靠性测试要简单得多,而改善最大 dV GS /dt 与 ASS 测试匹配的解决方案将是应用中净 V th偏移的更好预测因素。当然,结果也高度依赖于外部组件,例如 R G和电感路径。图 6 显示了R G对 V th偏移的影响的示例。

图 6:栅极电阻对 GSS V th偏移的影响(来源:Gómez 等人,2024 年)

图 6:栅极电阻对 GSS V th偏移的影响(来源:Gómez 等人,2024 年)

GSS 测试是 SiC MOSFET 整体可靠性检查的重要组成部分。在最终应用中,V th偏移会导致 R DS(on)从较小的栅极过驱动中增加。在太阳能逆变器等应用中,部件的使用寿命可能超过 1e13 个开关周期,准确预测器件行为的这种变化对于确保整个系统的正常运行非常重要。将 GSS 栅极波形与实际 ASS 条件相匹配可以确保这一点。

1 Gómez 等人(2024 年)。“深入研究栅极开关应力和应用开关应力下 SiC MOSFET 性能的退化。”APEC 2024。

2 Salmen 等人(2021 年)。“一种新测试程序,用于实际评估开关操作中 SiC MOSFET 的寿命终止电气参数稳定性。”2021 年 IEEE 国际可靠性物理研讨会 (IRPS),第 1-7 页。