三大晶圆代工厂计划最早在 2025 年为 18 埃代工应用High NA EUV 光刻技术,但用标准 EUV(NA = 0.33)取代单次曝光高High NA(0.55)而非双重图案化,取决于它是否能以合理的每片晶圆成本提供更好的结果。

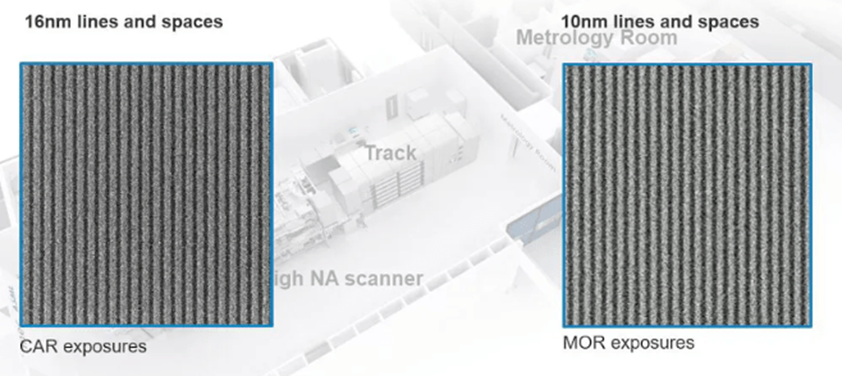

到目前为止,2024 年是高数值孔径 EUV 光刻技术的辉煌一年。英特尔代工厂已接收了一台高数值孔径 EUV 扫描仪。英特尔、imec、ASML、IBM 以及即将加入的台积电正在努力为新扫描仪加强光刻胶堆栈、EUV 掩模技术和首批工艺。2 月份,业界还在 SPIE 上收到了突破性消息,imec 宣布使用化学放大光刻胶解决了 16nm 线和空间问题,并使用金属氧化物光刻胶和高数值孔径图案化解决了 10nm 特征问题(见图 1)。

’图 1:High NA EUV 扫描仪使用化学放大光刻胶 (CAR) 打印 16nm 特征,但能够使用金属氧化物光刻胶 (MOR) 解析 10nm 特征。来源:imec

在本月的 Semicon West 和 imec 技术论坛上,来自 ASML、IBM、imec、Lam Research 和 TEL 的光刻专家齐聚一堂,分享High NA EUV 的进展和生产率提升。从这些和其他信息来看,EUV 晶圆厂很可能准备采用金属氧化物光刻胶堆叠、新的随机还原策略、角度蚀刻以及可能的曲线掩模,以从 2nm 器件节点(22nm 间距)过渡到 10A 节点(18nm 间距、9nm CD),用于未来的大型 AI SoC 和加速器芯片。DRAM 制造商预计将在 10A 节点范围内采用高 NA EUV。

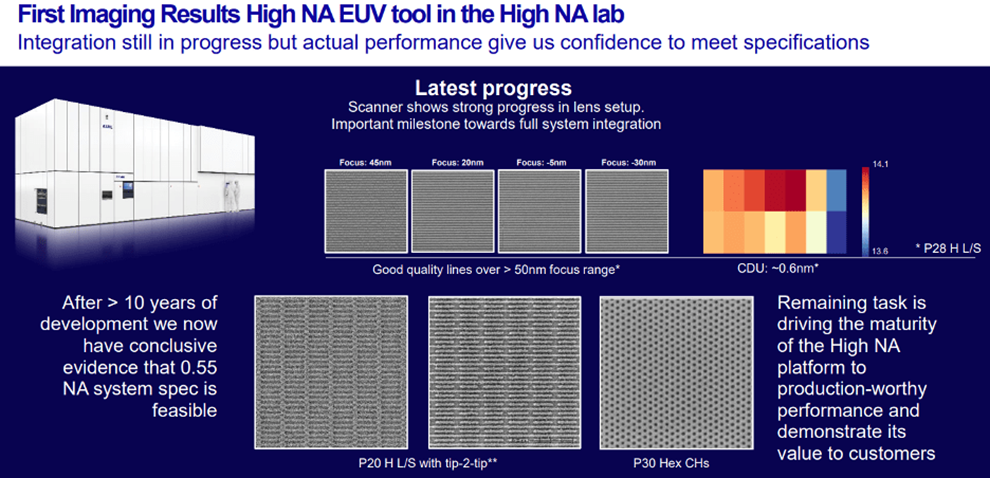

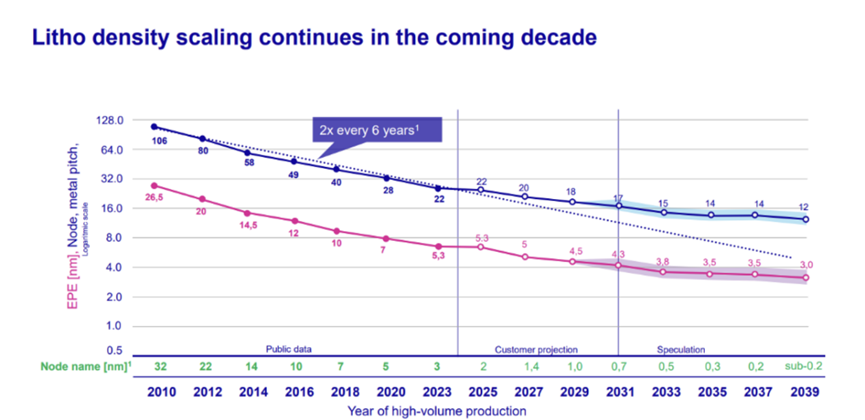

ASML 全球客户战略营销主管 Michael Lercel 表示:“2039 年的发展路线图清楚地表明,需要将关键尺寸降至 20nm 间距以下,到下个十年末,间距可能降至 14nm 和 10nm。”High-NA 已展示出领先的性能(见图 2),包括打印 20nm 线条和空间以及 30nm 通孔。在 28nm 线条和空间上实现了 >50nm 的焦深和 0.6nm 的 CD 均匀性。

图2:0.55NA EUV 产生 20nm 线条和空间或 30nm 接触孔。来源:ASML

打印变异性控制与首先能够打印一个小特征同样重要。“我们发现,缩放基本上是在边缘放置错误方面我们可以做的极限,” Lam Research副总裁 Rich Wise 说。他重点介绍了流行的 RLS 三角形,该三角形说明了分辨率 R、线边缘粗糙度 L(“在某些情况下也是缺陷率和良率的代表)和 S(灵敏度或速度)之间的权衡。我们基本上可以满足其中任何两个指标,但满足所有三个指标才是最具挑战性的。只关注分辨率和线边缘粗糙度的结果通常会减慢扫描仪的速度,而我们希望尽可能地提高速度。”

寻找High NA 的临界点

晶圆厂通常会将新扫描仪的过渡时间安排在技术要求与投资回报率一致时。imec 副总裁 Ru-Gun Liu 表示:“尺寸缩放的关键驱动因素由著名的瑞利方程定义,R = k1λ/NA 2,其中主要分辨率缩小是使用较短波长和较大镜头实现的。在等待 EUV 成熟并达到具有竞争力的成本时,193nm 浸没式多重图案化技术对此进行了补充,而这大致就是我们现在再次看到的情况。High NA EUV 将通过用单一曝光解决方案取代复杂且昂贵的多重图案化工艺来启用逻辑 A14 节点。”

最近的晶圆运行表明,High NA 足以应对全栅纳米片的挑战。IBM 研究部光刻和计量高级经理 Luciana Meli 表示:“直接片图案化可实现设计灵活性和有效的栅极长度缩放,同时性能可与 SADP/SAQP 图案化片相媲美。”她指出,在单元末端插入单扩散断层 (SDB:single diffusion break) 是实现与 finFET 类似的设计灵活性的关键缩放旋钮。

Meli 指出,High NA 的一个突出需求是减少特征尖端间距。她表示,MOR 光刻胶平台可以在这方面提供帮助,将尖端间距扩展到 22nm,值得注意的是,其产量高于使用 CAR 平台获得的产量。即便如此,仍需要切割掩模来满足 20nm 规格。

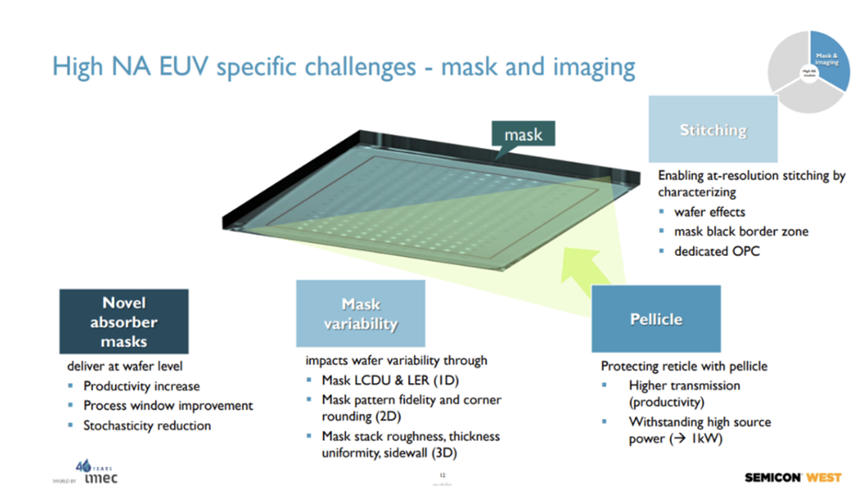

但High NA 的最大挑战似乎是较小的曝光场大小造成的。由于High NA EUV 光学元件上的镜头在 xy 方向上将掩模上的特征缩小了 4 倍和 8 倍(变形镜头),因此晶圆上的场大小只有 0.33NA EUV 和 193nm 光刻的一半(26 x 16.5 毫米 vs. 26 x 33 毫米)。两个曝光场必须精确拼接在一起。

芯片内拼接是一件大事。围绕设计、掩模、光学邻近校正 (OPC)、工艺和扫描仪设置的拼接优化只是高 NA 特定挑战之一。由于 SRAM 芯片已停止扩展,并且 SRAM 可占用 SoC 面积的 50%,因此只有堆叠芯片解决方案才能避免高 NA EUV 和拼接。

IBM 的 Meli 指出,挑战来自于High NA EUV 层与全场 0.33NA 层的结合,包括块和金属堆栈之间的叠加误差。

Imec 及其合作伙伴正在开发大规模场内拼接方法,这将减少应对场尺寸缩小的设计需求。Imec 正在为High NA EUV 寻求的另一项技术是使用定向自组装 (DSA) 来减少粗糙度和缺陷并降低剂量。第一步是将 DSA 图案缩小到 24nm 间距以下,从业界目前的 PS-b-PMMA 型嵌段共聚物转换为所谓的高 χ 嵌段共聚物。

Imec 还展示了在开发低 n 掩模吸收器方面取得的进展,该吸收器能够以更宽的工艺窗口和 20% 的线和空间剂量减少的形式提高性能,而不会增加粗糙度或随机故障(见图 3)。该研发机构还发现,尖端到尖端的尺寸不会受到剂量减少的负面影响,剂量减少会直接影响扫描仪的吞吐量。掩模上的 LWR/LER 的更大降低也在进行中,因为粗糙度意味着晶圆上的粗糙度会更大。

图 3:EUV 掩模中的新型低 n 吸收剂改善了工艺窗口并降低了剂量。需要在规模拼接、降低掩模变异性和碳纳米管薄膜开发方面取得更多进展。来源:imec

High NA扫描仪本身旨在提高生产率,包括更快的光罩和晶圆台、更强大的CO2激光源和更高效的光子转换效率,从而提高扫描仪的吞吐量。

ASML 的 Lercel 表示:“为了提高原始产量,我们希望提高驱动激光器的功率,同时也希望提高光源的重复率。因此,EUV 光源加速单个锡滴穿过真空室,然后它们受到高功率红外激光器的撞击。如今,这种情况每秒发生 50,000 次。借助新的High NA EUV 系统,我们的重复率上升到 62 千赫兹,而 500 瓦的更高功率使我们能够实现每小时 220 片晶圆的产量,这是关键因素。”

业界对 EUV 扫描仪高能耗的持续担忧推动了变革。每一代 EUV 扫描仪都降低了每片晶圆加工所消耗的能源。2023 年,每片曝光晶圆的能源消耗量是 2018 年的 42%。工具可用性为 93%。

减少随机性

随着特征的规模扩大,粗糙度在整个特征尺寸中所占的比例越来越大。LER 和 LWR 可解释 3nm 节点边缘位置误差的 50%。2nm 节点允许的边缘位置误差仅为 5 至 6nm,预计 1nm 节点将降至 4.5nm(见图 4)。

这种工艺变化会侵蚀工艺窗口,并会因线路之间的桥接、断裂的碎片线路、闭合的通孔或合并的相邻孔而导致电气故障。因此,光刻师和蚀刻团队不断开发减少 EPE 的策略,EPE 是一个涵盖覆盖(层/层偏移)、CD 均匀性和随机性的术语。

图 4:允许的变异性(边缘位置误差)随着可实现的分辨率而缩小。来源:ASML

另一种看待这个问题的方式是使用有用的工艺窗口。高良率的图案化工艺由所谓的“无故障范围”(failure free latitude,)定义,它指的是在不看到线条断裂的情况下可以打印的最小特征,以及在不看到线条合并的情况下可以打印的最大特征。它由聚焦窗口 (DOF) 和曝光窗口来表征。

“在许多情况下,随着间距的缩小,这种宽容度会趋于零,因此,为了帮助继续缩小间距,我们共同优化了干式金属氧化物光刻胶及其底层,以减少分辨率、LER 和灵敏度之间的权衡。底层有助于加速光刻胶在后处理过程中的激活,尤其是在烘烤过程中,”Lam Research 的 Wise 说道。

MOR 与 CAR 材料

旋涂化学放大光刻胶是 193nm immersion (193i) 和 EUV 图案化中的主力材料,但近年来,干式光刻胶以新的化学配方出现,即所谓的金属氧化物光刻胶 (MOR)。JSR(前身为 Inpria)以旋涂形式提供 MOR,Lam Research 则以干式系统提供 MOR。

干法(基于 CVD)光刻胶工艺的性能优势包括比有机材料更高的吸收率和图案坍塌的可能性有限。“还有机会优化后续转移蚀刻,无论是原位还是非原位,以消除缺陷和线宽粗糙度等问题。而且它在厚度方面非常可调,甚至可以从光刻胶顶部到光刻胶底部改变工艺,”Wise 说。

使用干光刻胶在 0.33NA 扫描仪上制作了 12nm(24nm 间距)的线条和空间。另一个优点是,与旋涂晶圆轨道光刻胶处理相比,使用干光刻胶堆栈可以将材料浪费降低 5 到 10 倍。成像堆栈包括硅上的光刻胶、底层和硬掩模(例如 PECVD 碳、氮化硅或 SiOC)。

关于硬掩模层的转移蚀刻,Wise 透露,Lam Research 最近开发了一种更强大的等离子源,可以更有效地分解等离子体中的物质。“转移蚀刻之所以如此重要,是因为我们利用这种蚀刻来纠正图案转移过程中出现的一些随机缺陷。”

蚀刻技术的另一项创新是改变 300 毫米晶圆与等离子源之间的角度,所有主要供应商都提供此功能。所谓的横向或角度蚀刻解决了减少尖端间距的需求,而无需使用单独的切割掩模曝光和蚀刻步骤。此类蚀刻还有可能减少整个芯片的尖端之间的差异,从而提高产量。

TEL 研究员 Tomonari Yamamoto 介绍了其公司使用新蚀刻源和倾斜晶圆台的定向 CD 修改工艺。改变系统中的角度可以调整横向蚀刻速率,从而无需使用双重图案化即可制造椭圆形或其他结构。新源还旨在减少浮渣缺陷并降低图案粗糙度。

但这种系统更重要的结果可能是降低粗糙度和随机缺陷,而这些缺陷无法通过其他方式解决,同时提供在 y 方向上扩展特征的能力。imec 的刘说:“应用角度蚀刻光束来推动线尖到尖的间距并降低线/空间图案的粗糙度。”他将这项技术称为反式图案化,并指出它可能用于将接触孔拉伸为椭圆形结构,甚至将孔拉伸为线。“人们可以使用这项技术将图案从孔更改为线,并进一步减小间距——就像变形金刚一样”,这启发了反式图案化这个名字。

然而,刘警告称,现在还为时过早。“这只是跨图案化相关研究的开始,因为其在工艺、OPC 设计合规性和成本效益方面的价值和可行性仍在研究中。”

Lam 公司的 Wise 讨论的另一项工艺改进涉及使用选择性钝化层,然后进行蚀刻,以降低 LER 和 LWR。Wise 描述了解决小块光刻胶(以浮渣或底脚的形式出现在线条底部)的情况。“在晶圆上,我们可以看到这样的缺陷,但通过使用我们的新源并沉积一层钝化层,该钝化层可以很好地粘附在完全形成的光刻胶线条上,但与这些浮渣区域结合较差,我们可以突破并去除这些缺陷。”钝化工艺还有助于平滑 LER 和 LWR。

TEL 的 Yamamoto 介绍了旋涂金属氧化物光刻胶的结果,表明 MOR(尤其是采用新的显影剂化学方法)可以改善工艺窗口并降低 24nm 间距线和空间的特征粗糙度。相对于 CAR 光刻胶,MOR 在较小特征尺寸下还具有更大的抗图案塌陷能力。他进一步指出,High NA EUV 所需的薄光刻胶更容易受到随机缺陷的影响。

Brewer Science新兴材料技术总监 Joyce Lowes 表示,EUV 光刻胶的底层对于工艺的可扩展性起着至关重要的作用。为了帮助图案转移,底层需要以更薄的层提供比其前身更好的抗蚀刻性。底层还需要与硬掩模和硅很好地粘附在一起,同时在宽工艺窗口下工作,而不会增加图案缺陷率。

曲线结构

曲线图案(curvilinear patterns)似乎将成为必需品,因为设备需要更短的连接。曲线结构可缩短层与层之间以及同一平面内线与线之间的连接。

“我们提出并证明,在设计中加入曲线形状可以降低制造成本,提高芯片的功率和性能,”imec 的刘说。此外,我们计划使用曲线设计来增加晶体管密度。我们已经开发出一种在标准单元中使用曲线设计的方法,并提供了设计解决方案,例如设计规则应用和寻找 OPC 解决方案。”

几乎无限的计算资源可用于 EUV 掩模的掩模写入过程。与多光束掩模写入器结合使用,光学邻近校正 (OPC) 掩模过程可大大加快。曲线掩模的写入时间与正交掩模的写入时间相同。

专家指出,行业可能正在接近曲线(弯曲)掩模图案的临界点,这种图案可以缩短互连距离并降低成本。D2S 董事长兼首席执行官 Aki Fujimura 表示:“曲线图案目前已用于 193i 和 EUV 的生产掩模中。但不同的公司使用方式不同。有些公司只在芯片上需要它的热点处使用它。”

标准 EDA 集成将实现完整的芯片/晶圆曲线实施。但首先,需要有一个测量曲线均匀性的惯例。“当谈到软件校正工具时,你会做一些校正,试图让实际形状符合你的设计,”Fujimura 说。“凭借曼哈顿特征(正交),业界不久前确定了测量 CD 和 CD 均匀性的标准方法。我们没有这样的曲线结构惯例,那么如何比较轮廓与轮廓呢?这还没有确定。”

尽管如此,晶圆厂仍在向前发展。Fujimura 补充道:“在最近的 Synopsys 技术论坛上,台积电讨论了其庞大的 GPU 基础设施,重点介绍了其‘大型 GPU 农场’以及他们进一步扩展这一能力的计划,因为 GPU 具有诸多优势,尤其是在涉及曲线掩模形状的处理方面。”

结论

现在是从事前沿工作的有趣时期,工程师可以打印和控制 10nm 特征。展望 18A 至 14A 节点,标准 EUV(0.33 NA)可能会通过多重图案化尽可能延长,同时在工具、材料和掩模方面取得许多进步,这些进步协同作用,大规模图案化和蚀刻设备。

在某种程度上,该行业似乎准备采用围绕金属氧化物光刻胶、底层和显影工艺(湿法、干法或两者兼有)构建的新型光刻胶平台,这些平台将与新的蚀刻平台协同工作,通过多种策略组合来延长 CD 并减少随机缺陷。

对于High NA,片内拼接尚处于起步阶段,这是一项由变形镜头引发的全新技术,而掩模中的新吸收材料有望扩大工艺窗口。似乎每一项在不降低其他关键指标的情况下提高性能和吞吐量的开发都将找到进入生产使用的方法。