据麦姆斯咨询报道,为应对6G射频前端设计挑战,英国MEMS初创公司Nanusens利用其开创性的MEMS-within-CMOS™技术,开发了一种新颖的射频数字可调电容器(DTC)解决方案。

Nanusens首席执行官(CEO)Josep Montanyà解释说:“这是我们利用自主技术实现低成本5G高频段工作的进一步扩展。我们已向客户提供了相关测试芯片,客户对芯片的性能印象深刻,并建议我们利用这项技术为6G开发解决方案,因为该行业确实面临着挑战。”

6G需要处理比5G更多甚至更高的频率。为此,需要在手机中集成更多的天线,以处理更多的频段,但由于要在手机中安装更多的天线,天线必须更小,因此效率会降低。为了使每根天线获得最佳性能,需要对每根天线进行调谐,以便重新配置不同的频段,并避免与功率放大器不匹配。目前,通过可调电容器能够实现这一目标。

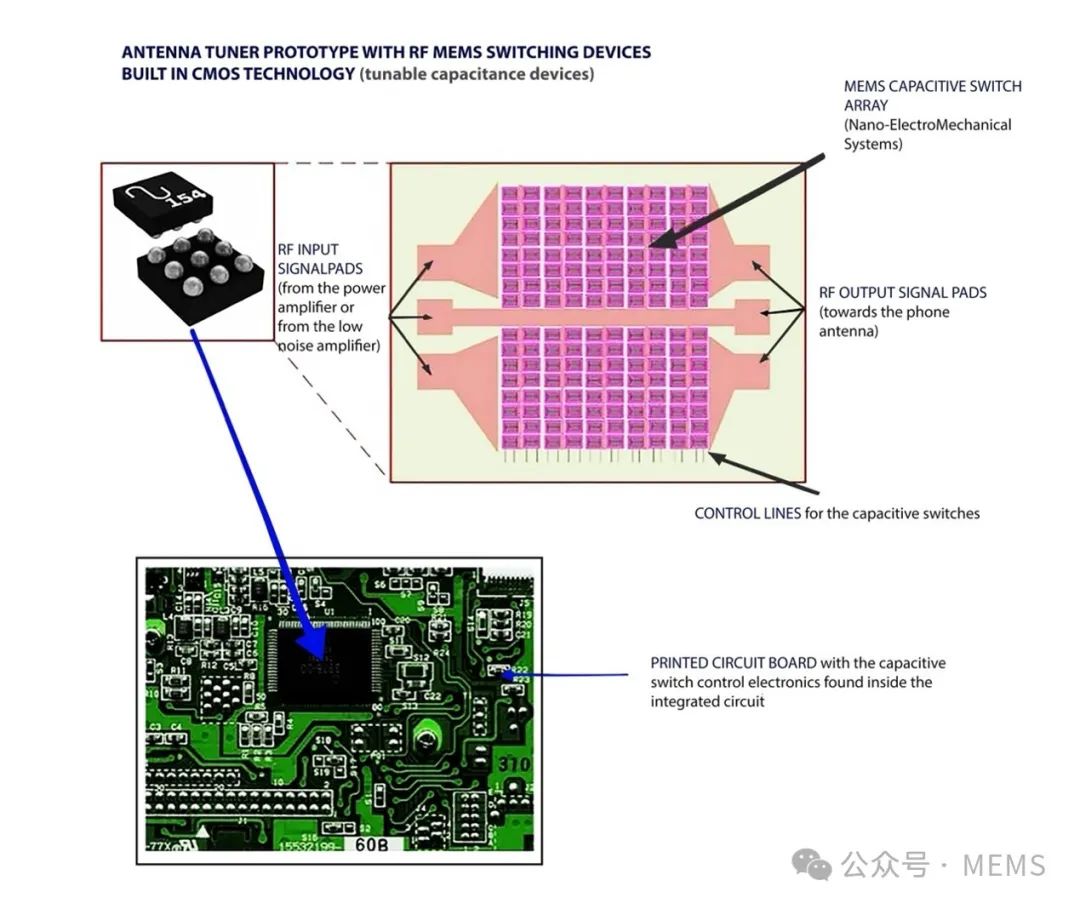

Nanusens利用其经过硅验证的专利技术,采用标准CMOS工艺构建MEMS结构,在芯片的CMOS层内创建了大量可进行数字调谐的纳米级电容器及控制电路。这种单芯片集成解决方案比竞争型解决方案更小,并凭借更好的线性度(意味着失真几乎为零)提供了更好的性能。此外,由于纳米电容器功率效率更高,通话时间最多可延长30%,从而解决了目前效率下降的问题。

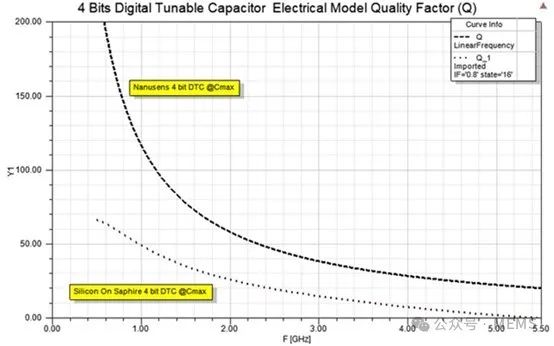

Nanusens射频数字可调电容器(DTC)还解决了当前天线解决方案在更高频段功耗越来越大的问题。其关键在于1 GHz超过100的极高Q值,而且重要的是,其Q值在更高频段仍能保持较高水准,以保持极低的功率损耗,而在更高频段,竞争技术的Q值会显著下降。实际效果是通讯覆盖范围增加了约14%甚至更多,减少了掉线或接收不良的情况,从而改善了用户体验。

Nanusens首席技术官(CTO)Marc Llamas博士说:“我们为5G和6G射频前端提供的独特解决方案,令我们提供展示的主要射频厂商感到非常兴奋,他们一直渴求更优的解决方案。我们相信,这就是他们一直在寻找的射频前端解决方案,有望使6G市场真正起飞。该解决方案不仅适用于手机,还适用于工业和汽车领域的其它应用,因为其延迟更低,数据传输速率是5G的50倍(每秒1000千兆比特)。在人工智能(AI)、虚拟现实(VR)、增强现实(AR)和物联网(IoT)等数据密集型应用需求快速增长的推动下,6G市场潜力巨大,预计每年新增设备数以亿计。而我们的独特技术,可以在任何IC代工厂采用标准CMOS工艺制造,意味着我们几乎可以无限量地生产以满足巨大的市场需求。”

固态开关和RF MEMS解决方案

固态开关的问题在于其Q值较低,Q值是衡量性能的一个指标,Q值越高越好,因为Q值越高表明工作时的损耗越低。固态开关解决方案的Q值较低是由于其导通态电阻(Ron)造成的。当频率上升到更高的5G频段时,这种情况会变得更糟,已成为有效利用更高频段的限制因素。RF MEMS可调谐电容器的问题在于可靠性差,因为它们使用电介质。电介质充电是RF MEMS器件失效的主要原因,同时也限制了电介质击穿前可承受的峰-峰值电压。

Nanusens开发了一种解决方案,可以避免这两个问题。Nanusens采用一种射频电容开关阵列,为更高的6G频段提供了天线调谐功能。这解决了低Q值的问题,因为在这种设计中没有导通态电阻,因此在1 GHz实现了超过100的极高Q值。而且,重要的是,其Q值在更高频段仍能保持较高水准,使损耗非常低,而竞争技术的Q值在更高频段会显著下降。此外,RF MEMS不存在电介质充电和/或击穿的问题,因为这种创新设计中没有使用电介质。因此,Nanusens射频数字可调电容器在实验室中成功通过了40多亿次开关循环,而没有出现性能下降。它们还非常坚固耐用,已成功通过冲击、振动、热循环、MSL 1和HTSL测试。

主要性能参数

射频数字可调电容器的关键因素包括Q值和线性度。Nanusens射频数字可调电容器的Q值在1 GHz超过100,与最先进的RF MEMS解决方案不相上下,远高于固态开关解决方案。它们还展现了出色的线性度,IMD3超过90 dBc,这也是5G的要求。

其最小电容可以保持在非常小的范围,单个电容关闭状态下的关断电容(Coff)可低至30 fF(意味着4位射频数字可调电容器的Cmin为0.45 pF),未来迭代后甚至可以更低。

同样,目前其电容比为2.2,Nanusens希望在下一次产品迭代中将电容比提高到4。

解决日益严重的寄生问题

随着器件性能逐渐接近理想性能(极低的Coff和极高的Q值),以及新的分配频段开始转向微波区域,互连寄生对性能的负面影响将越来越大。

采用标准CMOS工艺制造意味着Nanusens射频数字可调电容器可以和其它射频前端元件(如功率放大器、低噪声放大器和收发器)同时在同一芯片上制造,从而大大降低互连寄生,同时实现可重新配置。这些单芯片可重新配置解决方案适用于超小型、扁平化、低成本的晶圆级芯片封装(WLCSP),与竞争技术的多元件解决方案相比,这种集成还降低了物料成本(BOM),节省了电路板面积。

标准CMOS工艺

采用标准CMOS工艺使Nanusens器件能够从CMOS的规模经济中获益,因此成本远低于竞争产品,后者往往采用的是更昂贵的绝缘体上硅(SOI)/硅基蓝宝石工艺或特色MEMS制造工艺。此外,Nanusens还受益于IC代工厂的高良率,产量几乎不受限制,并且可以使用任何IC代工厂进行生产。产品生产时间是典型CMOS产品的生产时间,不像某些竞争技术的非标准产品需要更长的时间。

Nanusens如何使用标准CMOS工艺

Nanusens使用气相氢氟酸(vHF)通过钝化层上的焊盘开口蚀刻金属间介质(IMD)以形成纳米结构。然后根据需要封孔和封装芯片。由于只使用标准的CMOS工艺,仅需极少的后处理,芯片可根据需要直接与有源电路集成,具有与CMOS芯片类似的高良率。这也意味着生产不受代工厂的限制。

关于Nanusens

Nanusens由Josep Montanyà博士和Marc Llamas博士于2014年创立,总部位于英国德文郡派恩顿,在西班牙巴塞罗那和中国深圳设有研发办事处。该公司充分利用了创始人的前公司Baolab Microsystems开发的研究成果和专业知识。Nanusens获得了Inveready、Caixa Capital Risc和Dieco Capital以及一些超高净值投资者的风险投资。

延伸阅读:

《5G和6G封装天线(AiP)技术及市场-2024版》

《射频(RF)声波滤波器专利全景分析-2024版》