动动手指,关注公众号并加星标哦

(1)

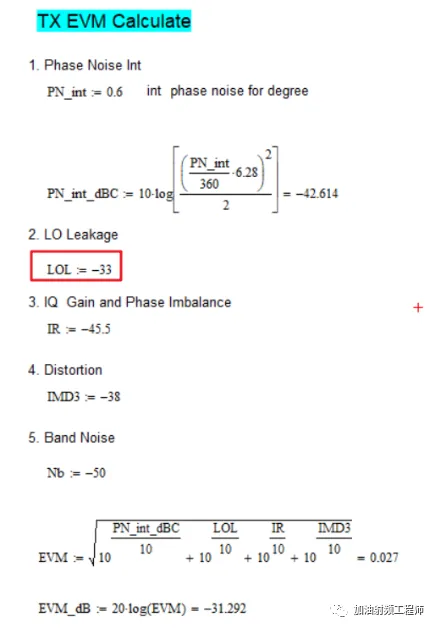

以下是仿真验证目标。

需要先理解师姐给的这幅图中每一项指标的意思。因为要对系统链路建模,除了知道大概框架之外,还需要知道每个器件的具体性能。

(2)

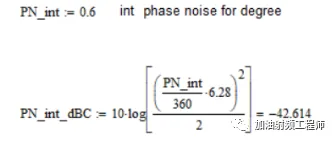

首先第一项,标题为Phase Noise Int。

这里,又可以复习一下相噪的概念。

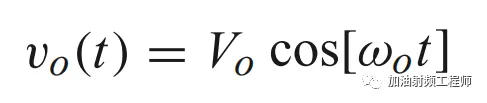

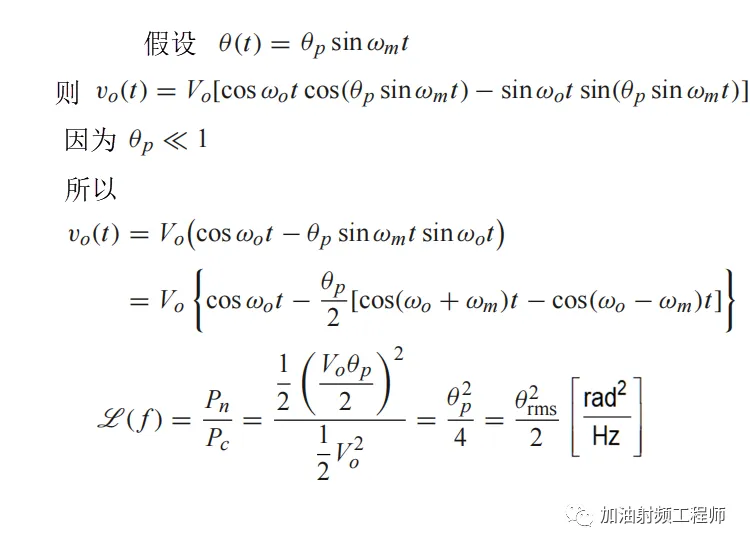

一个理想的信号,可以用下式进行表示:

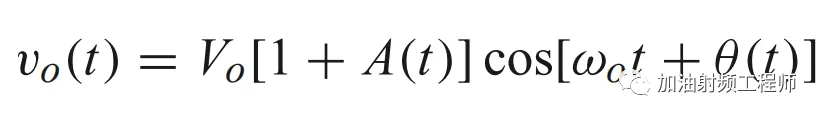

但是,在现实世界中,信号是这样的:

其中,A(t)代表幅度噪声,通常可忽略;θ(t)表示相位噪声。

L ( f )的单位是rad^2/Hz,对其取10*log(),即得到我们常见的dBc/Hz。

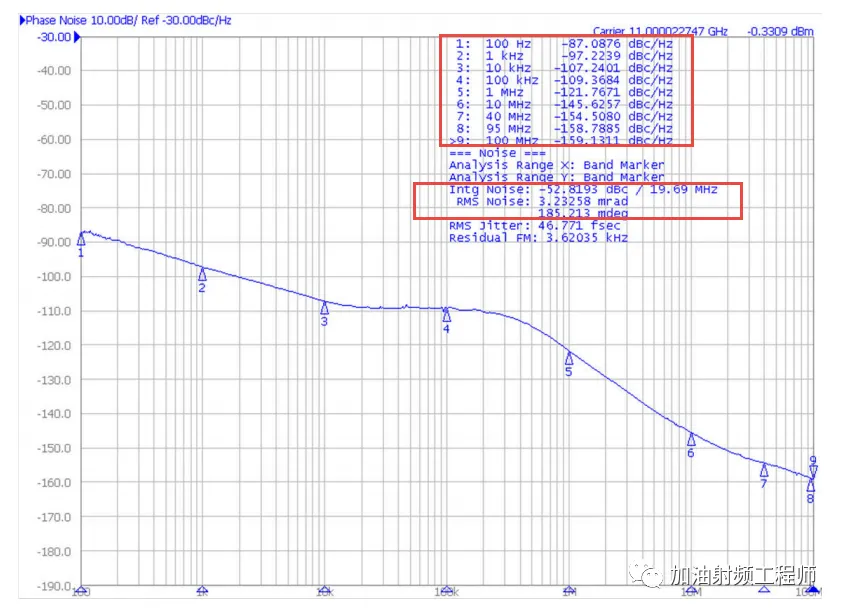

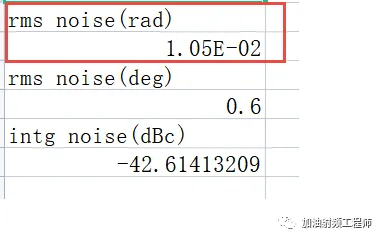

相噪可以用指定偏移频率处的相噪来表示,也可以用指定带宽内的积分RMS噪声表示,比如下面的相噪曲线图所示。

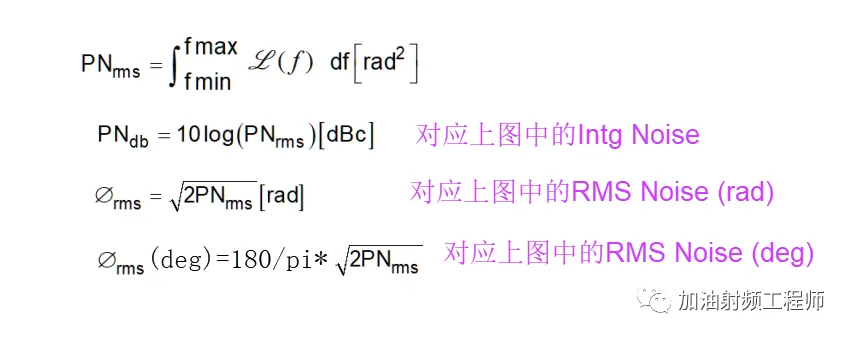

假设fmin,fmax分别是积分带宽的下限和上限。

那么:

相噪曲线图中的数值如下图:

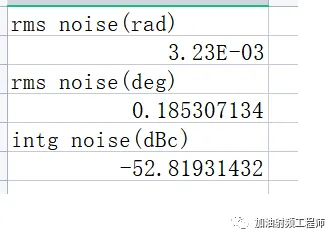

RMS noise: 3.23258 mrad,185.213 mdeg

Intg Noise:-52.8193 dBc/19.69 MHz

用excel列出上面的公式,来复算一下上面的数值,完全符合。

再回到验证目标图中的第一项,即:

对应的rad值为:

积分带宽是1K~10MHz,通过小软件,来拟合出一种相噪的可能。

(3)

LO leakage:

LOL=-33dBc

即本振泄露到输出端的大小,这个指标,在现在用的仿真模板中,用一个信号源来模拟。

(4)

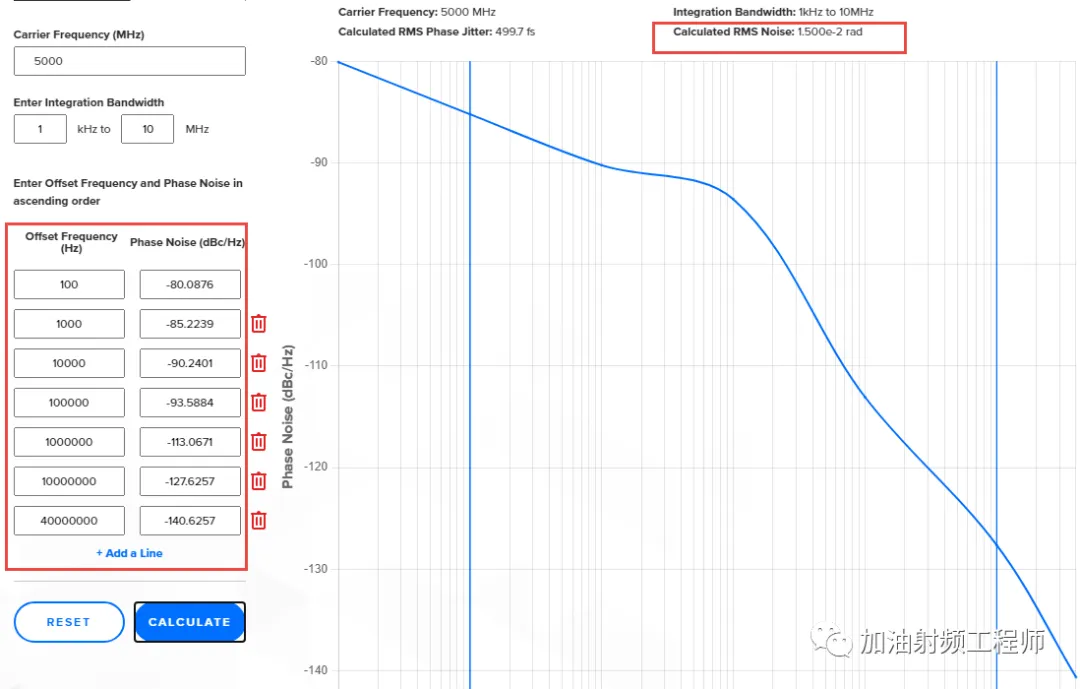

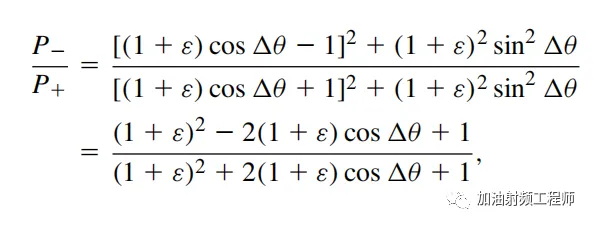

IQ Gain and Phase Imbalance

IR = -45.5dBc

因为IQ信号增益和相位的不平衡,会导致边带抑制变差,但是IR这个值是结果,需要拟合出IQ 增益和相位的不平衡的程度,才能在ADS里面进行建模。

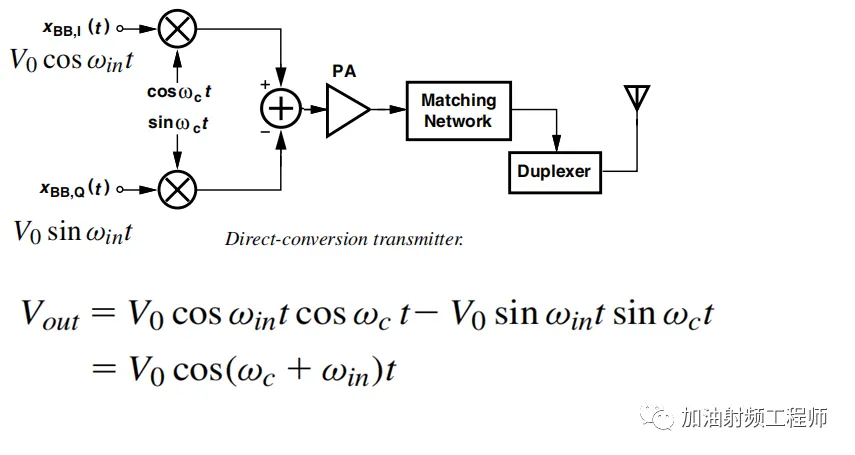

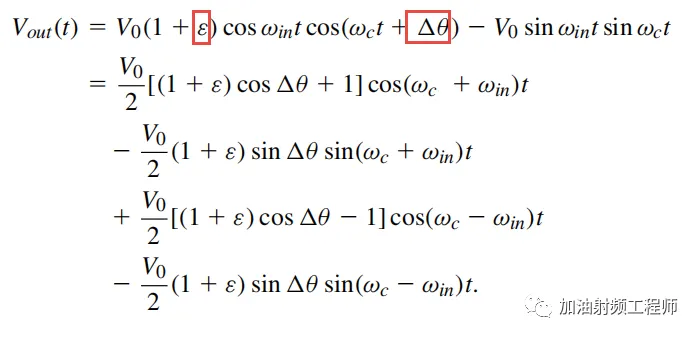

如下图所示的直接变频发射机,理想情况下,即IQ完全匹配(增益失配和相位失配都为0)时,当输入I和Q信号分别为V0cos(win*t)和V0sin(win*t)时,可以得到输出信号的表达式为:

但是,当存在增益失配和相位失配时,输出会变为:

其中,上图中第一个红框中,表示幅度失配;第二个红框,表示相位失配。

所以,IR即是不想要的边带wc-win上的功率与有用边带wc+win的功率的比值,即:

用excel来模拟一下上述公式,来拟合出IR=-45.5dBc时,对应的幅度和相位失配。因为用的仿真模板,加入幅度失配比较容易,所以按下图进行设置,仿真出来的IR结果,与理论计算吻合。

(5)

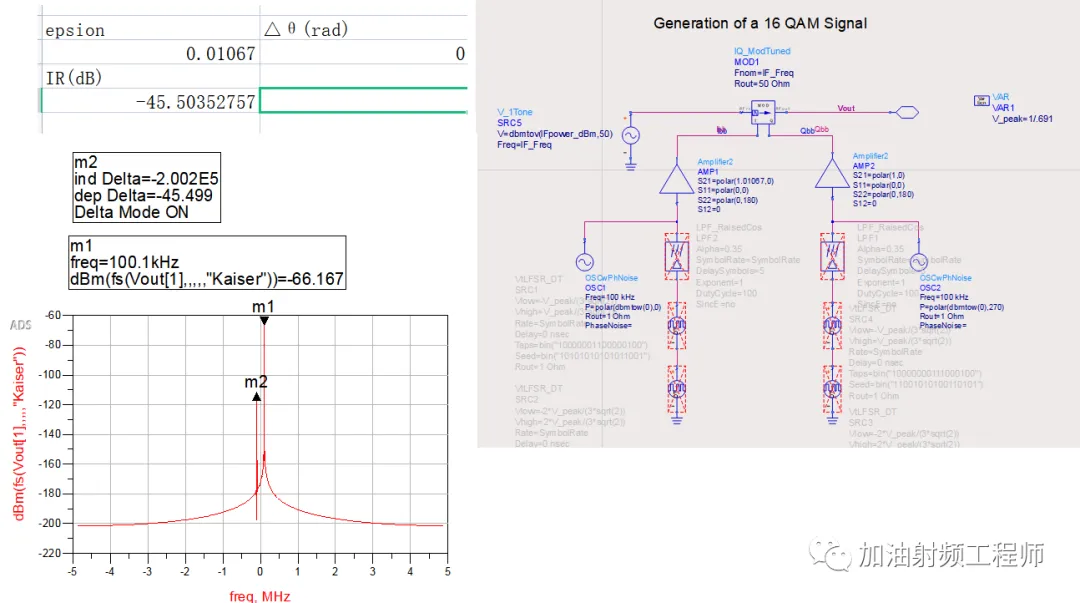

IMD3=-38 dBc,可以估算出整机的三阶互调截点。

假设输出功率是15dBm,那么输出三阶互调截点约为34dBm,这个是在输入信号比较小的时候,出来的结果。如果信号使得放大器进入了一点点非线性的话,会有少许的差别。

所以,对放大器的TOI调整了一下,变为34.6dBm,使得仿真出来的结果,在输出功率为15dBm时,IMD3=-38dBc。

(6)

Band Noise:-50dBc@1KHz~20MHz。

设置链路的噪声系数,使得带内噪声为-50dBc。通过HB仿真,来确认设置的正确性。

(7)

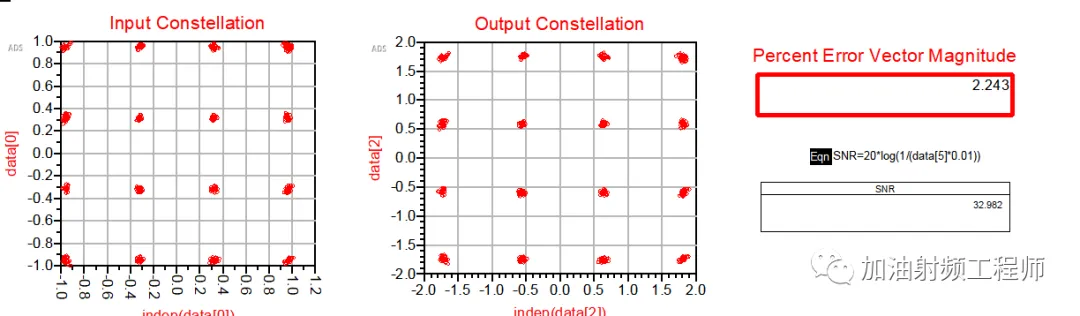

现在开始仿真了哈。

首先,调制是16QAM,把symbolrate设置为14.44MHz。

仿真出来的结果,和理论计算的差一点,这边是0.022,理论计算是0.027。(也有一部分带外噪声计入带内了,因为ENV计算的是时域,所以带内的EVM,可能比0.022还要小一点)。

(8)

如果用射频层面的调制信号仿真的话,流程是这么一个流程。

参考文献:

[1] TI应用文档:Impact of PLL Jitter to GSPS ADC's SNR and

Performance Optimization

[2] David M. Pozar,Microwave Engineering

[3] 相噪与抖动转换的小工具:Abracon | Phase Noise Calculator

https://abracon.com/phase-noise-and-jitter-calculator

[4]razavi, 射频微电子

完结接收机课程吆喝处哈(已在平台上购买的同学,加我微信,领课件资料哈!)

想了解接收机的底层理论知识,可以选择这门课;

想了解ADS的系统仿真,可以选择这门课;

想了解SystemVue的系统仿真,可以选择这门课。

每个分指标的计算后面,都跟着一个仿真验证。所有指标都分配完了以后,还会有一个整体链路的仿真。

整体链路仿真,还分单音时候的验证+调制信号的验证;ADS仿完,再用SystemVue走一遍。

这些仿真步骤,该采用什么模板,各个参数该怎么设置,该用什么等价标准来判断,都是我花了很长时间探索,才联通起来的。

我觉得大概率是全网独一份,因为这些都是我结合软件自带的help文件和模板,再结合项目,一点一点探索出来的,有很多自己的想法在里面。

想报名的同学,可以海报底部扫码哈!

☜左右滑动查看更多

Slide for more photos