虽然关于计算和新内存类型(例如高带宽内存 (HBM))的讨论很多,但人工智能应用的兴起也对 NAND 存储提出了新的要求。这些应用需要不断增加的容量来支持内存密集型处理和人工智能训练模型的数据需求。

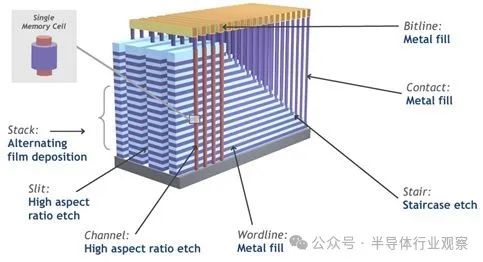

3D NAND 制造商面临的挑战是继续扩大密度和容量,同时仍以适合市场的成本提供这些产品。3D NAND 存储的扩展主要通过堆叠一层又一层的氧化物和氮化物层 (ONON) 并在其中蚀刻孔(也称为存储通道)来实现。ONON 堆栈中的氮化物是牺牲层,被钨取代以形成字线(图 1)。然而,近年来,扩展变得更加困难和复杂。

Lam Research 集团副总裁兼蚀刻产品部总经理 Harmeet Singh 博士表示:“随着行业目前着眼于本世纪末或之后不久实现 1,000 层路线图,我们面临着一些关键挑战。我们正在与主要客户积极合作,通过蚀刻创新以及其他先进制造工艺步骤及时解决这些问题。”

Lam 在蚀刻领域拥有丰富的经验,包括 20 多年担任干式等离子蚀刻市场领导者的经验,以及 10 多年担任 NAND 高深宽比蚀刻市场领导者的经验,涉及 7 代设备。“超过 1 亿片 NAND 晶圆的内存通道都是由 Lam 介电蚀刻机创建的,”Singh 说道。

在创建 3D NAND 时,氧化物和氮化物层的数量基本上决定了存储单元的数量,从而决定了设备的存储密度和容量。每个垂直存储串都从创建一个圆柱形孔开始,该孔的直径可能约为 100nm,深度为 5-6 μm(纵横比为 50-60:1),并穿透 128 层。

蚀刻非常深且精确的高纵横比 (HAR) 圆柱形孔的难度只会随着层数和相应的堆叠厚度而增加。当数百层 ONON 膜被图案化以创建临界尺寸为 100-115 纳米的孔时,这会将蚀刻纵横比(深度/宽度)推高至 100:1 以上。

“孔的深度与直径之比现在已超过 50:1,”Singh 说道。“随着垂直缩放的发生,层数和孔深度都在增加,但直径通常保持不变。”这意味着由多个层组成的 1,000 层 3D NAND 可能需要纵横比高达 100:1 的孔。“这要求内存通道蚀刻具有原子级精度,”他说道。

在如此小的尺寸下创建如此高纵横比的孔是难以理解的,尤其是当你考虑到孔的“轮廓”必须从上到下接近完美时,并且在生产中,可能在 300 毫米晶圆上形成 100 万亿个这样的孔。Singh 表示,创建这种高精度通道形状对于垂直缩放、横向缩放和逻辑缩放(例如从 TLC 到 QLC 及更高)至关重要。

“通常,当我们蚀刻时,物理和化学因素会导致圆柱体的底部小于圆柱体的顶部,因为反应物到达特征底部存在内在限制,”Singh 解释道。“圆柱体有变成圆锥体的趋势。”

Singh 表示,打造完美圆柱体的一个解决方案是采用 Lam 开发的脉冲功率等离子技术,该技术可在极短的脉冲中使用极高功率。“随着堆栈越来越高,我们一直在提高离子能量,”他说。“这样做的好处在于,我们一直保持平均功率不变,但增加脉冲的峰值功率。这提高了离子的效率,”他说。

Lam 还采用了新的“低温”蚀刻技术,这种技术可以使用特殊的蚀刻气体混合物,与其他蚀刻创新技术相结合,有助于在高纵横比的孔中获得近乎完美的轮廓。低温蚀刻是指低于 0°C 的蚀刻工艺。根据 Lam Research 最近的一篇论文,在如此低的温度下,会发生从化学吸附到物理吸附的转变,物理吸附是指吸附时不形成化学键的过程。由于未解离的中性物质的物理吸附,这会导致表面的中性物质浓度更高,蚀刻速率也更高。蚀刻副产物的吸附增强,无需添加聚合气体即可控制轮廓。

“由于堆栈变得如此之高,我们对低温蚀刻所用的化学方法进行了转变和创新,并增加了与参与蚀刻的中性物质的协同作用,从而获得了比以前更高的蚀刻速率,”Singh 说。

Lam低温蚀刻技术结合了高峰峰值电压处理、低温晶圆温度和工艺化学创新,与传统 HAR 蚀刻相比,蚀刻速度提高了 2.5 倍,轮廓精度提高了 2 倍。

Lam 是第一家在 2019 年将低温 HAR 蚀刻引入大批量生产的公司,目前拥有超过 7,500 台投入生产的 HAR 电介质蚀刻室。在已安装的近 1,000 台蚀刻室上,已有超过 500 万片晶圆使用 Lam 低温工艺进行了蚀刻。

“这对我们来说是一次硕果累累的旅程。我们帮助客户将 NAND 从 2D 过渡到 3D NAND,并将 3D NAND 扩展到今天的水平。蚀刻技术的持续创新将是实现 1,000 层 3D NAND 的关键,”Singh 说道。

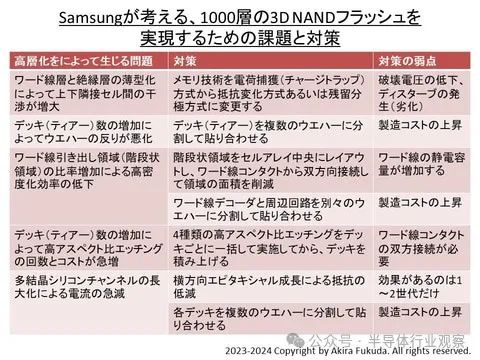

三星的1000层NAND思考

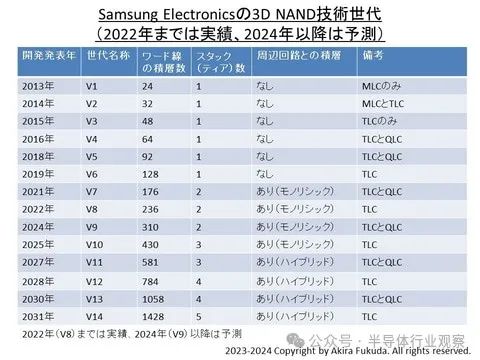

3D NAND 闪存不断变得更加复杂。3D NAND闪存的堆叠层数从2013年的24层(堆叠字线数量)开始,到9年后的2022年增加了约10倍,达到236层。次年(2023年),宣布开发出321层3D NAND闪存(以下简称3D NAND闪存)。

增加层叠字线(单元晶体管的栅极线)数量的“高层技术”是提高3D NAND闪存存储密度(单位面积的存储容量)的最重要技术。这是因为,如果将字线层数加倍,根据简单计算,存储密度也会加倍。

最大的3D NAND闪存制造商三星电子(以下简称三星)预计,在不久的将来,堆叠字线的数量将超过1,000层,并正在进行技术开发,目标是实现1,000层。其中一部分是在2023年12月9日至13日在美国举行的国际学术会议“IEDM 2023”(上公布的。

当前的3D NAND闪存技术一代(最先进的一代)正处于第8代(“第8代V-NAND”或三星称之为“V8”)到第9代(“V9”)的风口浪尖。第8代(V8)最多有236层,原型芯片已在2022年2月的国际会议ISSCC上公布。同年11月7日,三星正式宣布开始量产采用V8技术和TLC技术(3bit/cell技术)相结合的存储容量为1Tbit的3D NAND闪存。

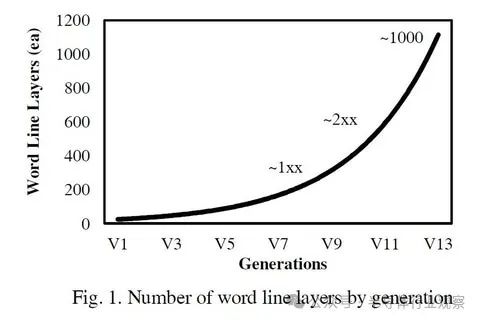

根据以往的发展趋势,假设每代高度增加1.35倍左右,可以预测2030年V13代的层叠字线数量将超过1000条。2022 年 12 月,三星在其技术博客上宣布,其目标是“到 2030 年将 3D NAND 技术发展到 1,000 层”。

在IEDM 2023的邀请演讲中,达到1000层左右的3D NAND一代被称为“V13”一代,毫无疑问,其发展目标是“将堆叠字线数量增加到1000层”。2030 年的“V13”一代。”就是这样。

三星在 IEDM 邀请演讲开始时指出,3D NAND 闪存层的速度正在呈指数级增长。最初,大约需要五代才能达到 100 层。

对于三星来说,第5代(V5)有92层,第6代(V6)有128层。然而,从第六代(V6)的128层开始,只过了两代就增加了100层。V6之后的下一代第8代(V8)的堆叠字线数量已达到最大236层。这意味着 V6 之上堆叠了 108 层。

如果继续这样下去,第9代(V9)将达到300层以上,第10代(V10)将达到430层,第11代(V11)将达到580层不是吗)。一代增加了100层,一代在上面增加了150层。

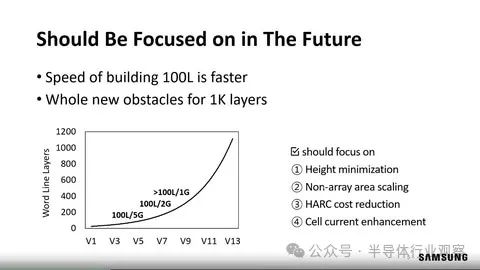

当然,这种高度的增加极大地增加了通道通孔(通道孔)等的纵横比。随着蚀刻和成膜难度的增加,工艺成本(制造设备的价格增加和产量下降)增加。

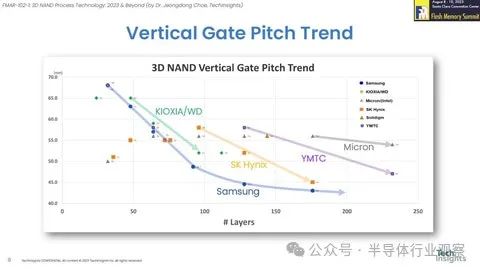

为了尽可能地降低纵横比,需要减小字线层和层间绝缘膜的厚度。根据芯片分析服务公司TechInsights公布的数据,在2023年8月的闪存相关活动“闪存峰会(FMS)”上,三星的字线间距(垂直方向)是各大3D NAND闪存公司中最高的。它比那个更窄。换句话说,我们主动将字线(栅极层)和绝缘膜(间隔层)做得更薄。

然而,字线间距的减小意味着垂直相邻单元晶体管之间的电干扰增加。过去终止平面 NAND 闪存小型化的同样问题也出现在 3D NAND 闪存上。

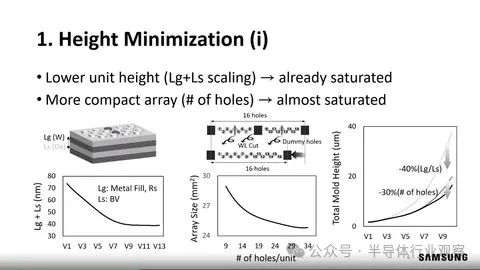

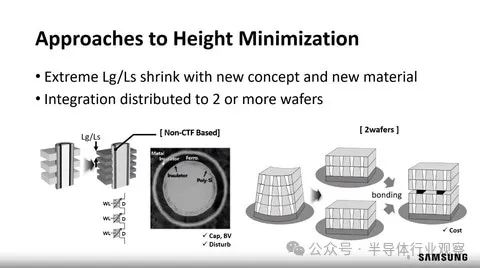

字线和绝缘层的厚度已经达到了40nm左右的薄化极限(合计值:节距),并且从第8代(V8:236层)开始,栅节距无法做得更窄,除非采取某种措施的改进。另外,对于与建造高层建筑同样重要的横向小型化,有一种方法是增加单位(per unit)通道孔的数量,但这种方法几乎已经达到了极限。

然后会发生什么?假设字线的最小间距为45nm,则100层等于45×100或4,500nm(4.5μm)。实际的存储单元阵列具有源极线、虚拟字线等,并且当转换为存储单元串时,物理100层减少到大约92层。也就是说,相当于5代(V5)。反过来说,一个存储单元中的1000层字线物理上超过了1050层。45×1,050 等于 47,250nm (47.3μm)。

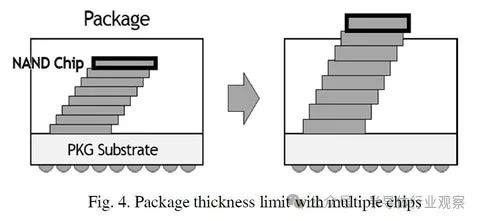

3D NAND 闪存封装具有四个或更多堆叠硅芯片的情况并不罕见。还有8张和16张的产品示例。假设存储单元阵列有1,000层且厚度为50μm,底层外围电路为30μm厚,则包括芯片堆叠间隔件在内的总厚度将达到100μm。

如果封装(仅模制树脂部分)的厚度为0.9mm(900μm),则当堆叠8个芯片时,芯片数量将达到最大值。目前,堆叠16层还有足够的空间,但我可以预见,到2030年代,堆叠16层将变得困难。

存储器技术的变化被认为是减轻上下相邻单元晶体管之间电干扰的一种手段。闪存通过注入和提取电荷来控制单元晶体管的阈值电压来存储数据。单元晶体管必须防止由于电荷泄漏而对相邻单元造成干扰。这会阻碍变薄。

三星正在开发的是铁电薄膜单元晶体管。将单元晶体管的栅极绝缘膜(多层)的一部分变为铁电膜,并通过改变铁电膜的极化方向来存储数据。原则上,垂直相邻单元晶体管之间的极化差异不会产生干扰。

三星在 IEDM 的同一会议上宣布了用于铁电单元晶体管的 3D NAND 结构原型设计的结果。它还通过控制多个偏振域来支持多值存储。在论文中,三星还提出了单元晶体管的想法,其中相变存储元件布置在沟道侧。

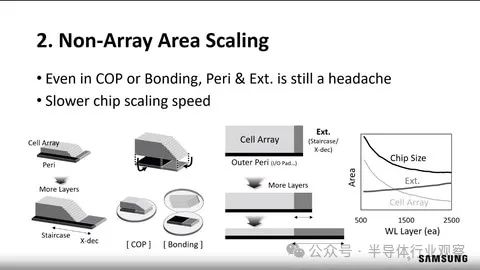

存储单元阵列的堆栈(甲板)需要一个称为“楼梯”的区域,其中字线垂直引出。随着沟道孔阵列(单元晶体管阵列)区域中堆叠字线数量的增加,阶梯区域的面积也增加。此外,字线解码器(X-dec)电路的面积也增加。

阶梯和字线解码器的总硅面积将比增加字线堆叠数量更快地扩大,因此未来会出现增加字线堆叠数量不会减小硅芯片尺寸的情况。

三星预测,当堆叠字线数量超过1500层时,阶梯和解码器的总硅面积将超过单元晶体管阵列的面积。在具有1,500至2,500个字线堆叠的超高层区域中,增加字线堆叠的数量并不会使硅芯片变得更小(存储密度不会提高)。

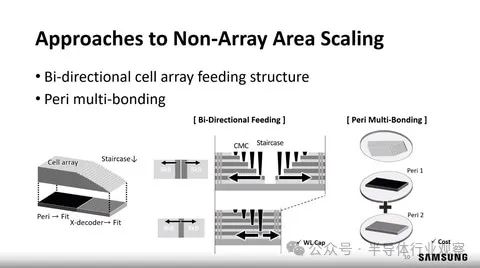

因此,三星设计了一种方法来减少楼梯区域的面积。当前的字线接触孔(从阶梯向上或向下延伸)位于字线的端部。字线只能在一个方向上连接。对策技术是将字线接触件放置在字线的中央,并将其连接到字线的左右两侧。不要创建像楼梯这样的阶梯区域。

此外,外围电路和字线解码器电路被创建在单独的晶片上,然后接合到存储单元阵列的晶片。通过这些努力,我们将继续减少硅芯片面积(提高存储密度)。

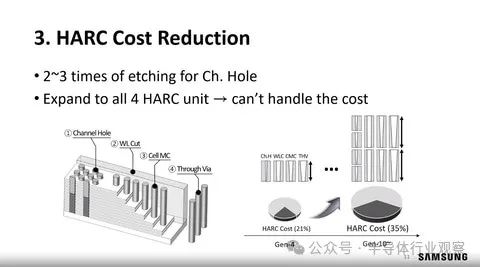

在3D NAND闪存的制造过程中,会重复进行高深宽比蚀刻(HARC(高深宽比接触)蚀刻)。有四种典型的 HARC 蚀刻。

Channel Hole(CHH)、Word Line Cut(WLC)、Cell Metal Contact(CMC)、Through Via(THV) 连接侧面和顶层外围电路的过孔必须进行至少四次蚀刻工艺(靠近单元阵列的漏极侧)。这些蚀刻步骤产生的成本(HARC成本)占总制造成本的相当大的比例。

然而,在制造第4代(V4:最多64层)3D NAND闪存时,HARC成本仅占整个工艺的21%。然而,从第10代(V10)开始,仅CHH就重复蚀刻四次,其他HARC则重复蚀刻两次,使总工艺成本的比例增加到35%。严格来说,HARC成本的快速增加将把整体制造成本推高到不可接受的水平。

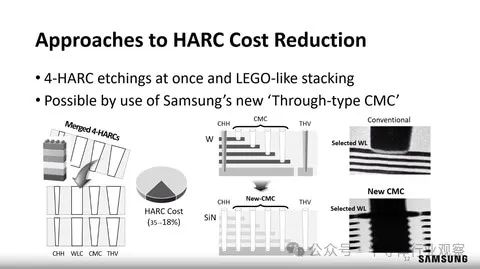

降低HARC刻蚀成本的基本方法是减少刻蚀次数。三星考虑通过同时对 CHH、WLC、CMC 和 THV 进行 HARC 蚀刻来减少蚀刻步骤数。这里的问题是,仅在CMC中,蚀刻深度根据字线的高度而变化。这使得一次性蚀刻 CHH、WLC 等变得极其困难。

因此,我们决定采用与CHH和WLC相同的方式对存储单元阵列的底部进行CMC蚀刻,使得蚀刻深度均匀。然后,将数量等于堆叠字线数量的CMC孔单独连接到适当的字线(具体连接方法未知)。

换言之,同时形成四种类型的HARC堆栈来创建块)。建造高层及哦啊狗是通过堆叠方块来实现的。该方法将 HARC 蚀刻成本大幅降低至制造成本的 18%。

说到2030年,距离现在已经是六年了(2024年)。如果计划在六年内开始量产,那么除非现在开始开发,否则不可能及时完成。而新的基础技术往往会带来问题,我们希望尽可能分布式地引入多种新技术,而不是集中在某一代。

最安全的选择是改进传统技术,但它已经达到了极限。从第9代(V9)到第13代(V13),共五代,每一代都将采用一项新的基本技术。这大概就是极限了。

来源:半导体行业观察

参考链接

免责声明

本平台所刊载的所有资料及图表仅供参考使用。刊载这些文档并不构成对任何股份的收购、购买、认购、抛售或持有的邀约或意图。投资者依据本网站提供的信息、资料及图表进行金融、证券等投资项目所造成的盈亏与本网站无关。除原创作品外,本平台所使用的文章、图片、视频及音乐属于原权利人所有,因客观原因,或会存在不当使用的情况,如部分文章或文章部分引用内容未能及时与原作者取得联系,或作者名称及原始出处标注错误等情况,非恶意侵犯原权利人相关权益,敬请相关权利人谅解并与我们联系及时处理,共同维护良好的网络创作环境。

芯通社

- SemiWebs -

专注半导体-手机通信-人工智能

请长按下面二维码关注芯通社

▼

伙伴们

错过也许就是一辈子

还不快关注我们?