作者:Meng Fancheng,AMD工程师;来源:AMD开发者社区

Mgmt(Configuration Management Interface)接口简介

配置管理接口可用于客户对PCIE的配置空间进行读写,本篇blog主要介绍配置管理接口的使用方法及其验证。

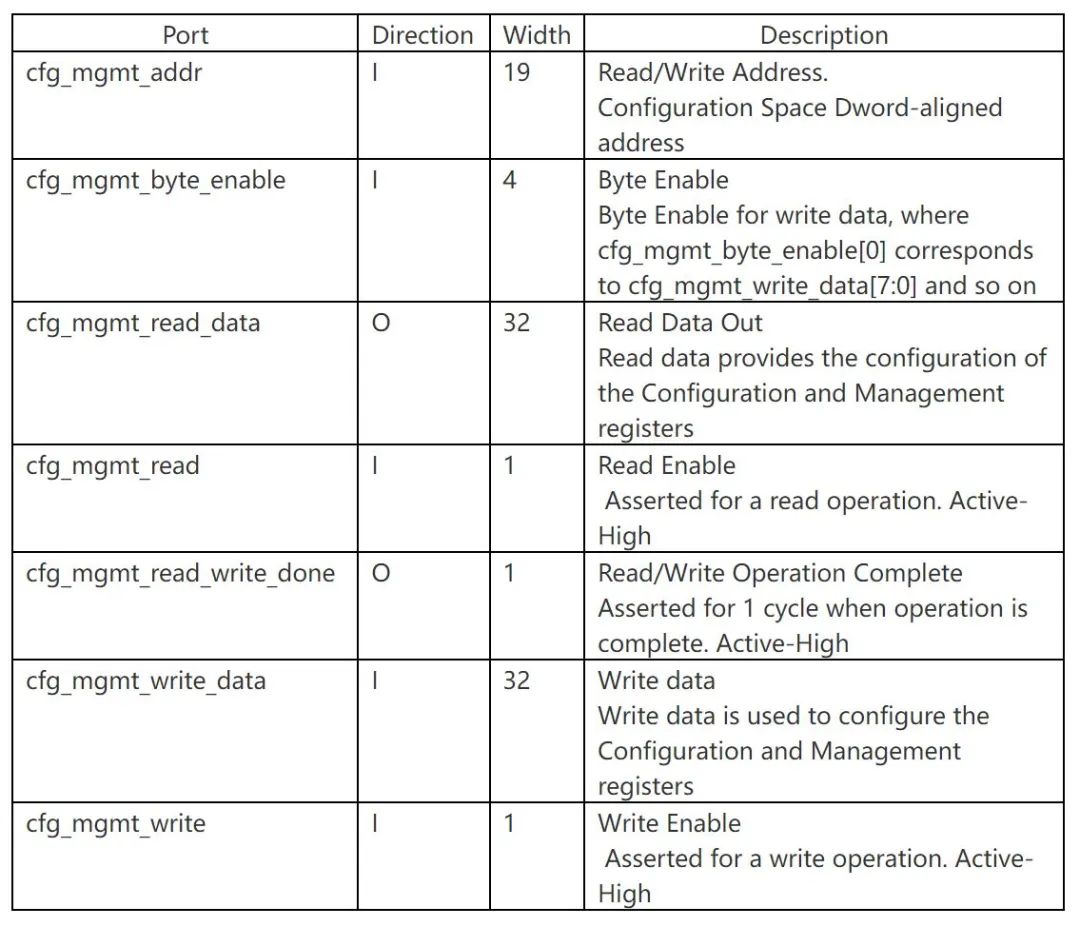

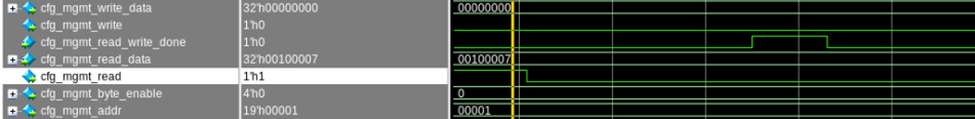

cfg_mgmt_addr是读写PCIe配置空间的地址,此输入的地址是实际要访问的地址除以4,例如下图1的中的Command寄存器的地址为04h,如果要改写此寄存器的值,cfg_mgmt_addr输入的数值为01h,cfg_mgmt_byte_enable为向配置接口写入的数据使能标志信号,位宽为4bit,每一位对应于写入数据的一个byte,数据总位宽为32bit。cfg_mgmt_read_data即为读出的相应配置空间寄存器的数值,在拉高配置管理接口的read信号后,cfg_mgmt_read_data将会输出对应于cfg_mgmt_addr地址的寄存器数值。cfg_mgmt_read为配置接口的读使能信号,此信号的使能代表读操作的启动。当cfg_mgmt_read_write_done置一时表一次读/写操作的完成。cfg_mgmt_write为配置接口的写使能信号,当此信号拉高时会将cfg_mgmt_write_data的值写入到地址为cfg_mgmt_addr的寄存器中。

图1

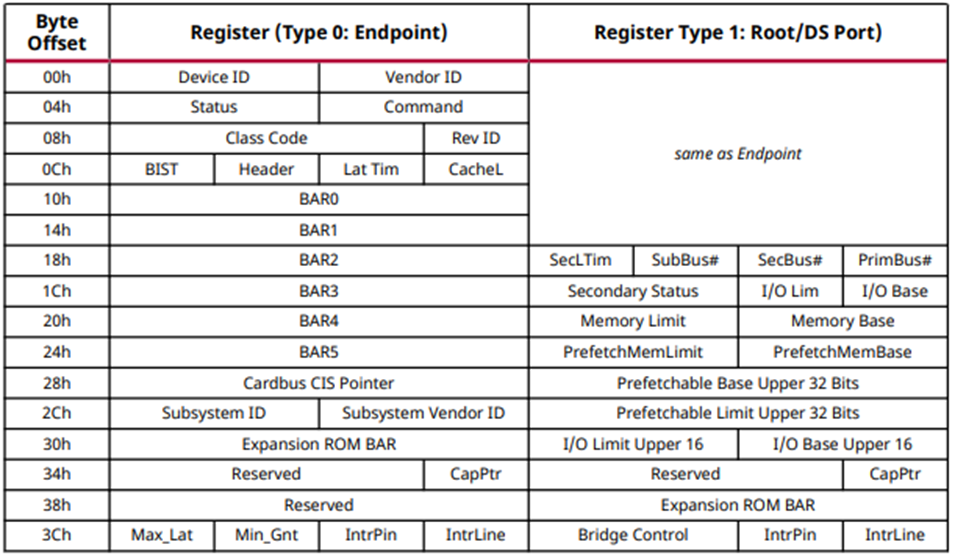

PCIE的Advanced Error Reporting Capability

PCIE的AER是PCIe debug时经常使用的capability,通常会根据此寄存器来判断PCIe在传输时所遇到的问题,其大致可以分为correctable和uncorrectable error。对于某些uncorrectable error,PCIe在上报后,可能对系统产生较大影响,频繁的上报错误中断会对CPU的处理进程产生影响,故有用户反馈需要对部分uncorrectable error进行mask,用户只需要使用配置管理接口并参照PCIe的协议以及AMD的手册,确定配置管理接口所需输入的地址和data即可完成相应uncorrectable error的mask。

图2

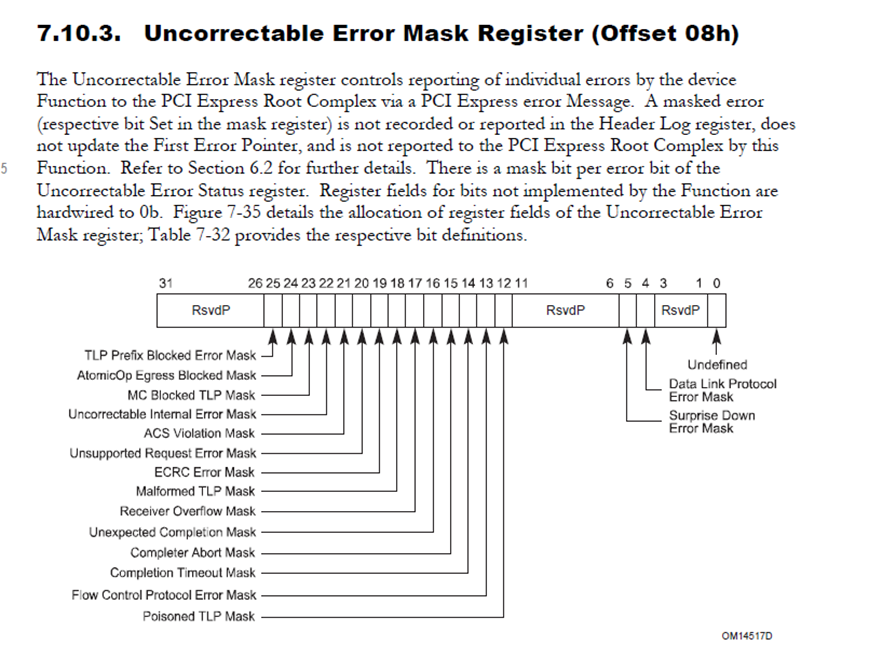

本篇blog主要使用配置管理接口对图3的命令寄存器的数值进行了改写,本次使用的设计是XDMA的example design,XDMA example design的仿真模块的RP(RootPort)部分在枚举时会对EP(EndPoint)的配置空间进行配置读写,其中的RP会对EP的命令寄存器进行写操作,代码如下:

TSK_TX_TYPE0_CONFIGURATION_WRITE(DEFAULT_TAG, 12'h04, 32'h00000007, 4'h1);DEFAULT_TAG = DEFAULT_TAG + 1;TSK_TX_CLK_EAT(100);

其含义为将命令寄存器的前3 bit位写为1,即Enable下图3的IO space,memory space和bus master。本篇blog对example进行了修改,即在RP将命令寄存器的前3bit全置为1后,通过配置管理接口改写命令寄存器的值,disable命令寄存器的IO space,memory space和bus master。随后修改XDMA example design 仿真模型的RP模块对命令寄存器进行配置读操作来验证配置管理接口成功修改了PCIe的配置空间寄存器。

图3

如图4所示,在RP使能EP配置空间的命令寄存器后,先使用配置管理接口对命令寄存器进行读操作。使用配置管理接口对命令寄存器进行读操作时,如图1所示,命令寄存器的地址为0x4h,只需要将cfg_mgmt_addr的值配置为0x1,并拉高cfg_mgmt_read,读出的数值为0x00100007,RP完成了对EP 命令寄存器的配置。

图4

如图5所示,使用配置管理接口对EP配置空间的命令寄存器的前3 bit赋值为0。如下图所示,拉高cfg_mgmt_write信号,将cfg_mgmt_addr输入的值设置为0x100000,将cfg_mgmt_byte_enable的值设置为0xf。

图5

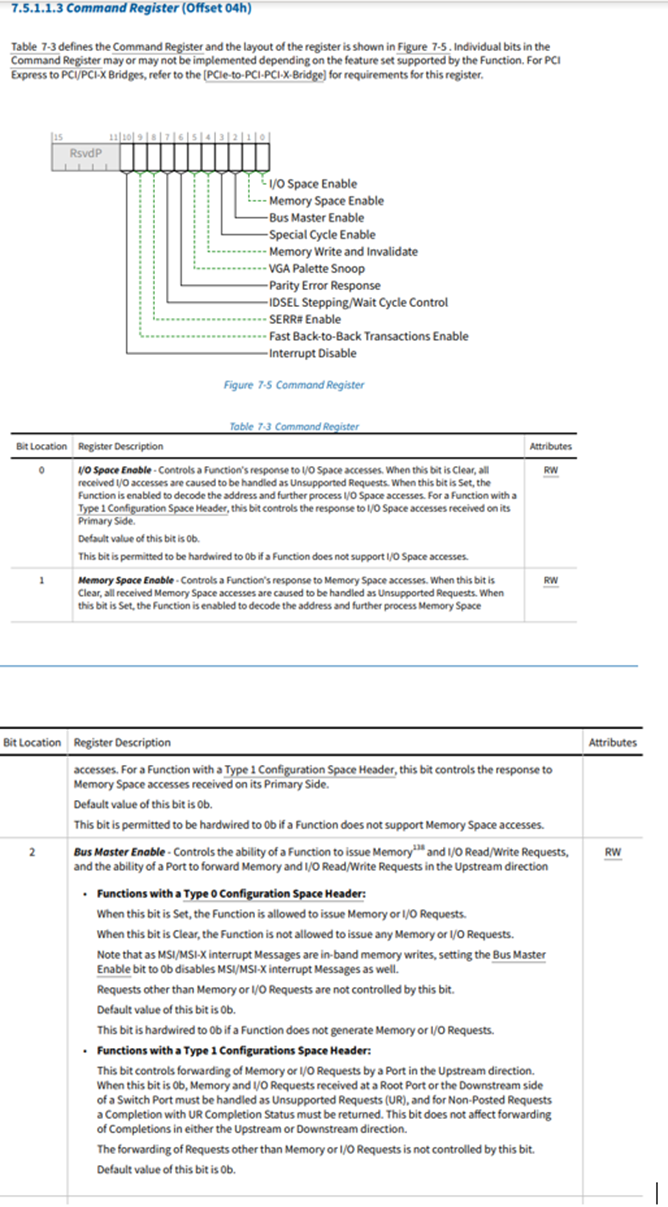

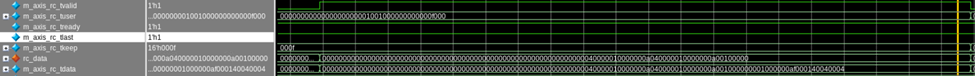

如图6所示,在使用配置管理接口对EP配置空间的命令寄存器进行改写后,使用RP的配置读读取EP配置空间的命令寄存器,验证配置管理接口是否对命令寄存器的数值改写成功。RP侧RQ接口发包的波形图不再进行描述,只看RC返回cpld,如下图RC_tvalid拉高期间,RC_tdata的前12bit为0xh004,表明读取的配置空间寄存器为命令寄存器,命令寄存器的数值为0x00100000。RP读出的数值与配置管理接口写入的数值一致,配置管理接口改写配置空间寄存器成功。

图6

【直播预告】