在进入High NA EUV光刻时代的前夕,imec计算技术与系统/计算系统扩展高级副总裁Steven Scheer谈到了ASML-imec联合高NA EUV光刻实验室对半导体行业的意义。

Steven Scheer表示:“位于荷兰费尔德霍芬的 ASML-imec High NA EUV 联合光刻实验室的开业,标志着High NA EUV 大规模生产应用准备工作取得里程碑式进展。领先的内存和逻辑芯片制造商现在可以使用第一台原型High NA (0.55NA) EUV 扫描仪 (TWINSCAN EXE:5000) 和周边基础设施,包括涂层和开发轨道、计量工具以及晶圆和掩模处理系统。Imec 和 ASML 将支持IDM 和代工厂降低图案化技术的风险,并在扫描仪在其生产工厂投入使用之前开发私有的High NA EUV 用例。

ASML和imec还将向更广泛的供应商生态系统提供访问权限。开发设施将使他们能够走在High NA EUV 专用材料和设备工程的最前沿。第三组用户是imec 和我们在高级图案化项目中的几家合作伙伴,推动图案化生态系统进入下一代High NA EUV。

位于费尔德霍芬的联合高数值孔径 EUV 光刻实验室成立的目的是加速和经济高效地将高数值孔径 EUV 投入生产。在短时间内,ASML 和 ZEISS 开发出了高数值孔径 EUV 扫描仪专用解决方案,涉及光源、光学元件、镜头变形、拼接、减小景深 (DOF)、边缘位置误差 (EPE) 和套准精度。

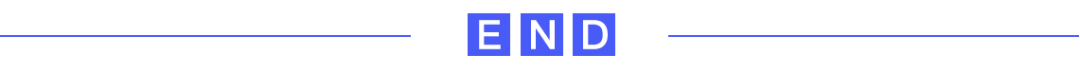

与此同时,imec 与 ASML 和我们扩展的供应商网络紧密合作,准备就绪0.55NA 图案化生态系统——正如在 2024 年 SPIE 先进光刻和图案化会议上宣布的那样。我们确保及时提供先进的光刻胶和底层材料、光掩模、计量技术、(变形)成像策略、光学邻近校正 (OPC) 以及第一代高数值孔径 EUV 的集成图案化和蚀刻技术。所有的准备工作最近都促成了第一批晶圆的曝光。分别在暴露金属氧化物光刻胶 (MOR) 和化学放大光刻胶 (CAR) 后,可以成功打印10nm 和 16nm 宽的线/空间(即 20nm 和 32nm 间距)。

现在,原型扫描仪和基础设施已经准备就绪,预计将在2025-2026 年投入大批量生产。”

图 1 - High NA 实验室中的 EXE:5000 High NA EUV 扫描仪展示了 16nm 线条和单次曝光中获得的首个 10nm 密集线条。

首批用例:14A 逻辑芯片和 D0a DRAM

“High NA EUV将首先应用于14A代逻辑芯片的量产,它将能够在一次曝光中实现间距为24nm的金属线/间距(M0/M2)的图案化,最终目标是达到18nm间距。这将提高产量并缩短周期时间,与现有的多次图案化0.33NA EUV方案相比,甚至可能减少二氧化碳排放。它最终将成为图案化互补场效应晶体管( CFET)芯片特有的复杂结构的关键技术。

随后,它将进入内存芯片制造领域,用于对DRAM 内存最关键的结构进行图案化。High NA EUV 预计可在一次曝光中对存储节点着陆垫和位线外围进行成像。D0a 2D-DRAM 技术将是第一个机会,需要 28nm 中心到中心间距。”

迈向下一代高数值孔径 EUV

“尽管尖端半导体生态系统的目标是短期内将High NA EUV 引入大批量生产,但imec 及其合作伙伴则着眼于更长远的目标——旨在实现下一代High NA EUV。对于这些活动,ASML-imec 联合High NA EUV 光刻实验室将充当 imec 设施的虚拟延伸。虽然曝光将在 Veldhoven 进行,但部分预处理和后处理工作将继续在 imec 的 300 毫米洁净室中进行。

首先,我们将密切监测High NA EUV 原型光刻集群(即连接的扫描仪和轨道)的性能。为此,imec 已准备好专用晶圆堆栈,并将基线工艺转移到原型High NA EUV 集群。我们的团队将从最终分辨率(最终目标是线/空间的金属间距为 18nm,接触孔的间距为 28nm)、稳定性(例如,曝光后结构临界尺寸 (CD) 和缺陷密度的稳定性)和有效焦深 (DOF) 方面评估集群。由于数值孔径较大,DOF 预计比 0.33NA EUV 小 2-3 倍——这是在 0.55NA EUV 中使用更薄光刻胶膜的原因之一。

此外,我们与计量领域的合作伙伴一起,在联合实验室开发并安装了专用检测工具,以监测和改善图案结构的缺陷率。电子束检测已被选为调查超小接触孔缺陷率的主要工具。我们的目标是实现业界雄心勃勃的目标,即在测量的一百万个接触孔中,每个接触孔只有一个缺陷。对于金属线/空间,光学检测工具与电子束相结合,以检测和分类缺陷,并提供指导,以实现每立方厘米缺陷数少于一个。

最后,逻辑和 DRAM 用例正在准备中。更大的工艺模块将接受图案分辨率和缺陷率方面的检查,例如使用检测工具和电气测试的组合。”

扩展 0.33NA EUV 活动,使Low NA EUV 和高 NA EUV 均受益

“我们洁净室中最新一代的 0.33NA EUV 扫描仪仍然是一套互补的工具,有助于改善下一代High NA EUV 的图案化生态系统。此外,并非所有芯片功能都需要High NA EUV——想想中间和全局片上互连线的图案化。因此,我们也将继续改善 0.33NA EUV 的生态系统。此外,一些挑战——例如需要改进抗蚀剂——在 0.33 和 0.55NA 中是共同的。

我们的“0.33NA 扩展活动”的重点领域之一是High NA EUV 的场拼接。场拼接的必要性源于引入变形镜头(即在 x 和 y 方向上具有不同缩小倍率的镜头)与不变的掩模空白尺寸(仅允许晶圆上的半场尺寸)相结合。在 2024 年 SPIE 高级光刻 + 图案会议上,imec 分享了其在实现分辨率场拼接方面的最新见解,这减少了为应对场尺寸减小而进行设计更改的需要。这项工作是在 imec 洁净室的 NXE:3400C 扫描仪上进行的,与 ASML 和我们的掩模合作伙伴合作。

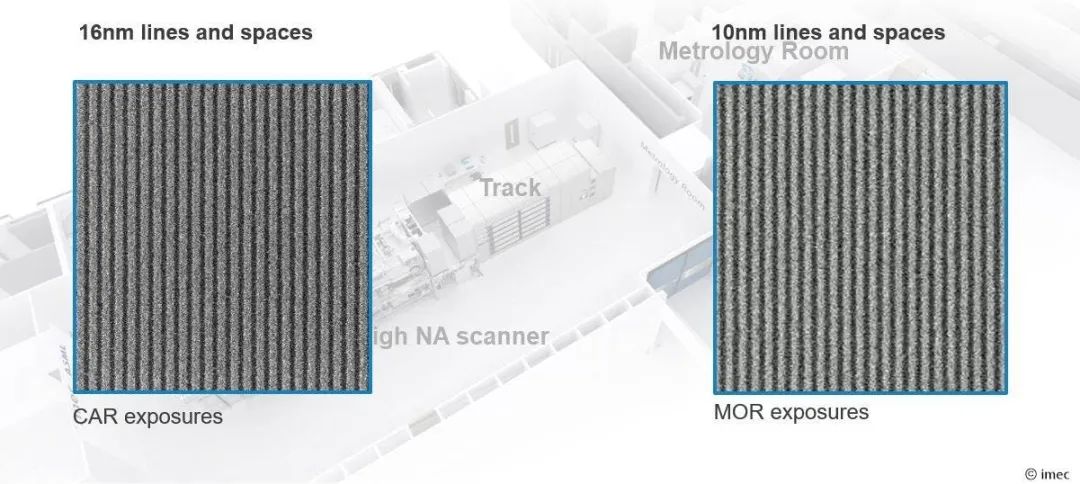

重要。可以通过最大化扫描仪吞吐量(以每小时晶圆片数 (wph) 为单位)来控制电力消耗。降低光刻胶剂量和管理芯片尺寸/光罩布局已被确定为保持该吞吐量的关键因素,因为它们都会影响High NA EUV 扫描仪完成晶圆曝光所需的时间。

图 2 – 图表显示,用High NA 单次曝光替代低 NA LELE 时,CO 2当量排放量减少 30%。两种情况下,假设标称吞吐量为 220wph。

除了光刻之外,蚀刻工艺也是直接二氧化碳排放的重要来源。大多数干蚀刻工艺都依赖于氟化合物,而氟化合物的全球变暖潜能值比二氧化碳高得多。我们开发工艺和设计方向以减少这些氟化合物的排放。

除了排放之外,还有其他值得关注的领域,例如材料稀缺和 PFAS 等有毒物质的使用。PFAS是半导体制造多个方面的内在推动因素,包括CAR和冲洗材料。High NA EUV 可能标志着不含 PFAS 的 MOR 的引入。我们最近展示了在薄 MOR 光刻胶中图案化小线条/空间的良好性能,以及使用带有二元明场掩模的 MOR 光刻胶图案化接触孔的良好性能。但 CAR 仍将是图案化不太重要的芯片特征的主力。我们与供应商社区一起,发起了新的研究计划,探索不含 PFAS 或限量 PFAS 的替代品,并对其性能进行基准测试。

© 滤波器 微信公众号