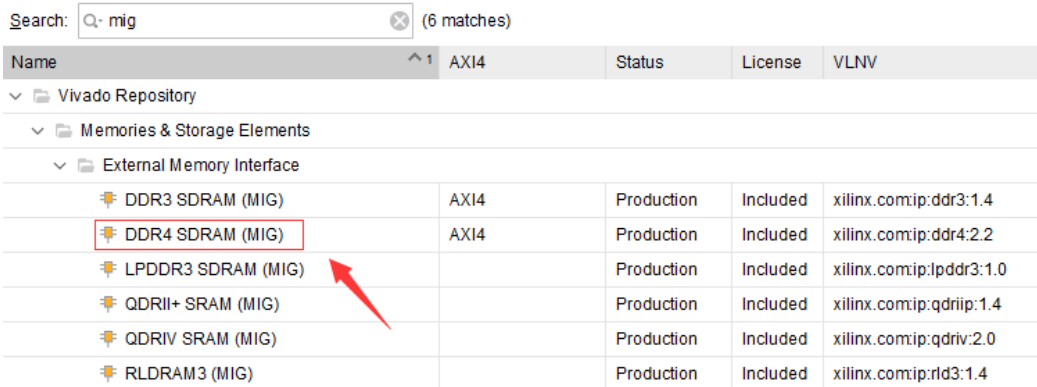

在搜索栏中输入 MIG,此时出现 MIG IP 核,找到 DDR4 SDRAM(MIG)。

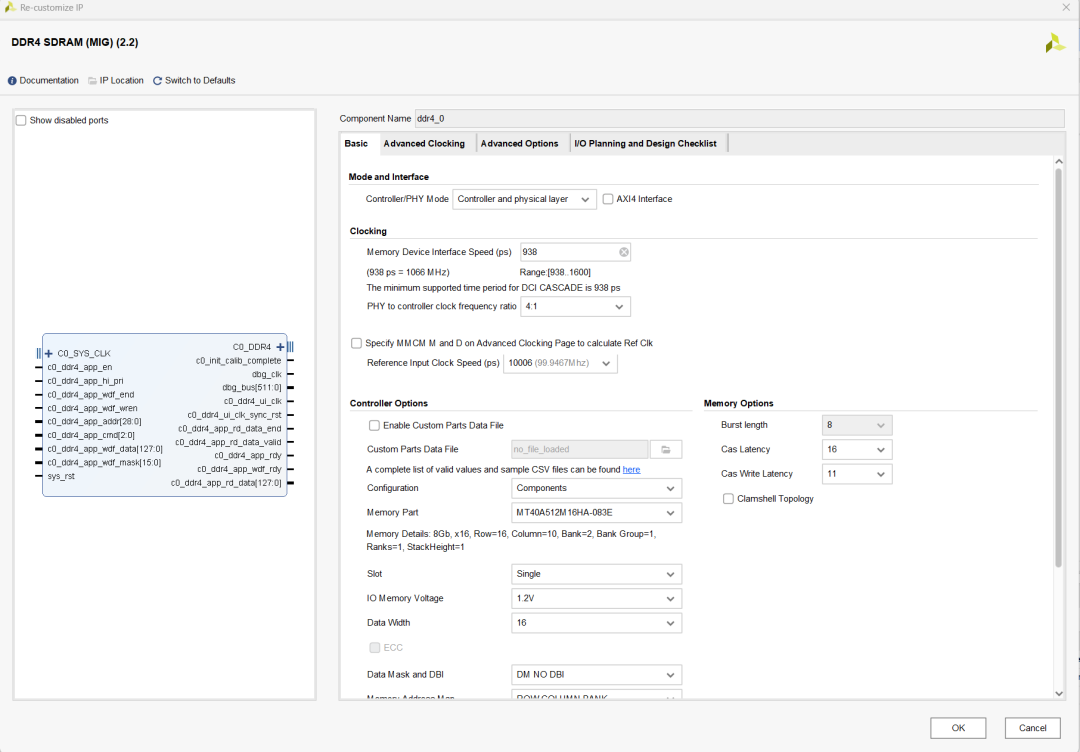

上图所示的是 MIG IP 核的 Basic 配置界面,配置信息作出说明:

Component Name:MIG IP 核的命名,可以保持默认,也可以自己取一个名字。

Mode and Interface:控制器的模式和接口选项,可以选择 AXI4 接口或者普通模式,并生成对应的 PHY组件(详情请参考官方文档 pg150)。

Memory Device Interface Speed:板载 DDR4 芯片的 IO 总线速率。

PHY to controller clock frequency ratio:用户时钟分频系数,这里只能选择 4 比 1,因此时钟频率等于 DDR4 芯片驱动时钟频率的四分之一。

Specify MMCM M and D on Advanced Clocking Page to calculate Ref Clk:特殊参考时钟选择,如果参考

时钟频率在“Reference input Clock Speed”选项列表中没有列出,可以使能这个选项,使能这个选项后

Reference input Clock Speed 时钟可以通过在 Advanced Clocking 配置页面配置 M 和 D 的值,并按照公式计

算出你想要的特殊参考时钟频率值。

Reference input Clock Speed:参考时钟。

Controller Options:控制器配置栏,如果使用 MIG IP 核内部默认的 DDR4 芯片,则只需要在 Memory Part

栏选中对应的 DDR4 芯片型号或者相近的型号即可,例如板载的 DDR4 芯片型号为 K4A8G16 在 MIG 中实际选择的是 MT40A512M16HA。如果使用的 DDR4 芯片型号不在 MIG IP 和的默认配置中也没有相近型号可供选择就需要手动定义 DDR4 芯片的参数文件,这个时候就需要使能定制型号(Enable CustomParts Data File),然后加载配置文件(Custom Parts Data File)。

Memory Options:配置突发长度和 CAS 延迟的,这里保持默认即可(如果需要修改请参考 DDR4 芯片数据手册)。

Configuration:DDR4 的组件类型,Components 代表 DDR4 颗粒,后面几个是内存条,本节实验是对颗

粒进行操作,所以选 Components。

Slot:当 DDR4 类型选择内存条时可以选择插槽数量,本节实验是对颗粒进行操作,所以只能选单槽。

IO Memory Voltage:IO 的电平,这里选择 1.2V。

Data Width:数据位宽,本节实验采用的 DDR4 颗粒位宽是 16 位的。

ECC:ECC 纠错相关的设置。

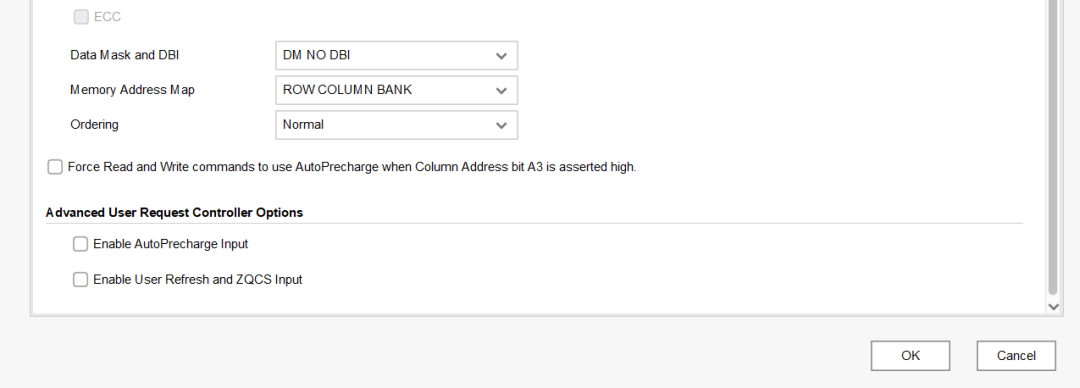

Force Read and Write commands to use AutoPrecharge when Column Address bitA3 is asserted high:当列地址 A3 被拉高强制自动预充电。

Enable AutoPrecharge Input:使能自动预充电输入端口。

Enable User Refresh and ZQCSInput:使能 ZQCS 刷新输入端口。

MIG IP 核配置界面的 Advanced Clocking 界面:

Advanced Clocking 界面主要分三块内容,最上面的 Specify M and D 设置是结合 Basic 界面的“Specify

MMCM M and D on Advanced Clocking Page to calculate Ref Clk”选项共同使用的,当选择使用特殊时钟选

项后,就可以 Specify M and D 设置界面去设置 M 和 D 的值,然后根据界面给出的公式计算出你想要的特殊时钟值。

中间界面 System Clock Option 选项是选择参考时钟的配置,可以选择无缓冲或者差分,本节实验使用的是差分。

最下面的界面是 Additional Clock Outputs 配置,这里可以额外输出四路时钟,如果有需求这里可以生成,

本节实验不需要用到额外时钟,所以全部“None”即可。

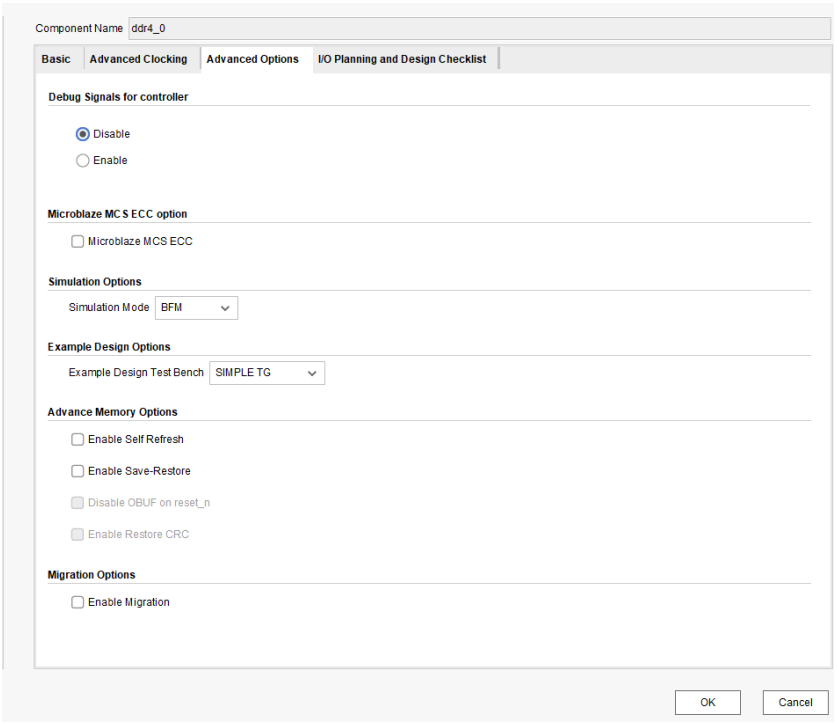

接下来切换至 Advanced Options 界面:

Advanced Options 界面的配置信息如下:

Debug Signals for controller:在 Xilinx 示例设计中,启用此功能会把状态信号连接到 ChipScope ILA 核中。

Microblaze MCS ECC option:Microblaze 的配置选项,选中它 Microblaze 的 MCS ECC 尺寸会增加。

Simulation Options:此选项仅对仿真有效。在选择 BFM 选项时,为 XiPhy 库使用行为模型,以加快模拟运行时间。选择 Unisim 则对 XiPhy 原语使用 Unisim 库。

Example Design Options:示例工程仿真文件的选择。

Advance Memory Options:提高运行性能的选项,可以选择自刷新和校准功能,并将这些信息保存在XSDB BRAM 中,也可以把 XSDB BRAM 中的信息存储在外部存储器中 。

Migration Options:引脚兼容选项,如果想兼容 UlitraScale 和 UltraScale+ fpga,就把这个选项选中。

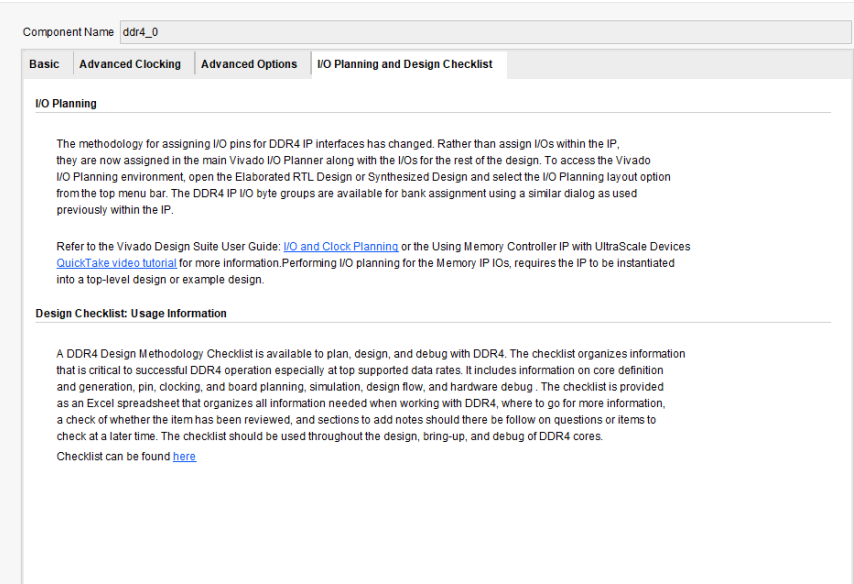

最后再来看看 IO Planning and Design Checklist 界面:

IO Planning and Design Checklist 界面提示我们 DDR4 IO 引脚分配的方式发生改变,不再像之前 DDR3

那样,需要在 MIG IP 核中就分配好管脚,DDR4 可以在 IO Planning 窗口分配管脚(或者直接编写 XDC 文

件)。