在采样速率和可用带宽方面,当今的射频模数转换器(RF ADC)已有长足的发展,其中还纳入了大量数字处理功能,电源方面的复杂性也有提高。那么,RF ADC为什么有如此多不同的电源轨和电源域?

随着硅处理技术的改进,晶体管的几何尺寸不断减小,意味着每 mm2面积上可以容纳更多的晶体管(即特征)。但是,人们仍然希望 ADC 实现与其前一代器件相同(或更好)的性能。

现在,ADC 的设计采取了多层面方法,其中:

1. 采样速度和模拟带宽必须得到改善;

2. 性能必须与前一代相同或更好;

3. 纳入更多片内数字处理功能来辅助数字接收逻辑。

|

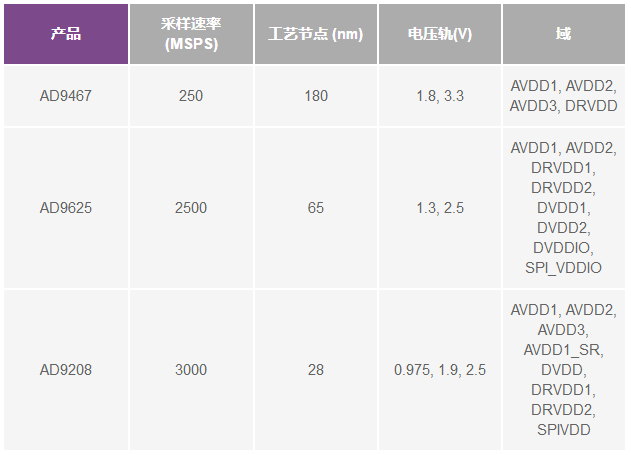

几何尺寸越小,电路设计人员能实现的电路速度就越快,而每MHz每个晶体管的功耗与上一代相同。以 AD9680 和 AD9695为例,二者分别采用65 nm和28 nm CMOS技术设计而成。在1.25 GSPS和1.3GSPS时,AD9680和AD9695的功耗分别为3.7 W和1.6 W。这表明,架构大致相同时,采用28 nm工艺制造的电路功耗比采用65 nm工艺制造的相同电路的功耗要低一半。因此,在消耗相同功率的情况下,28 nm工艺电路的运行速度可以是65 nm工艺电路的一倍。AD9208很好地说明了这一点。

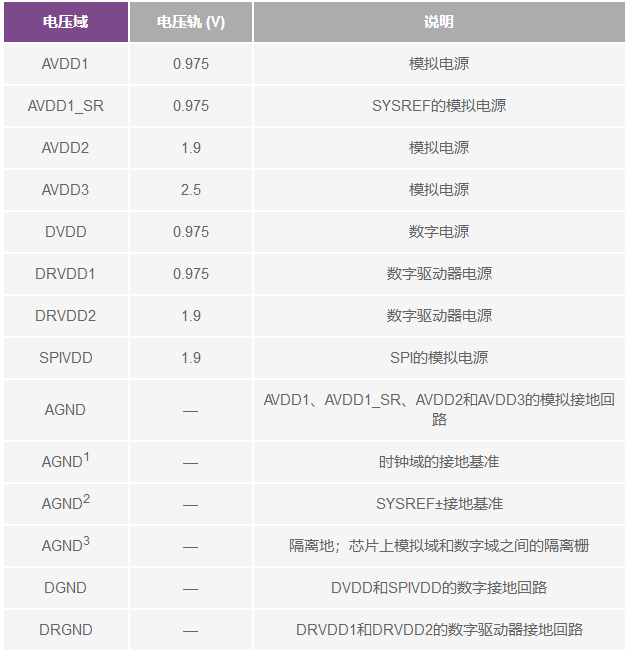

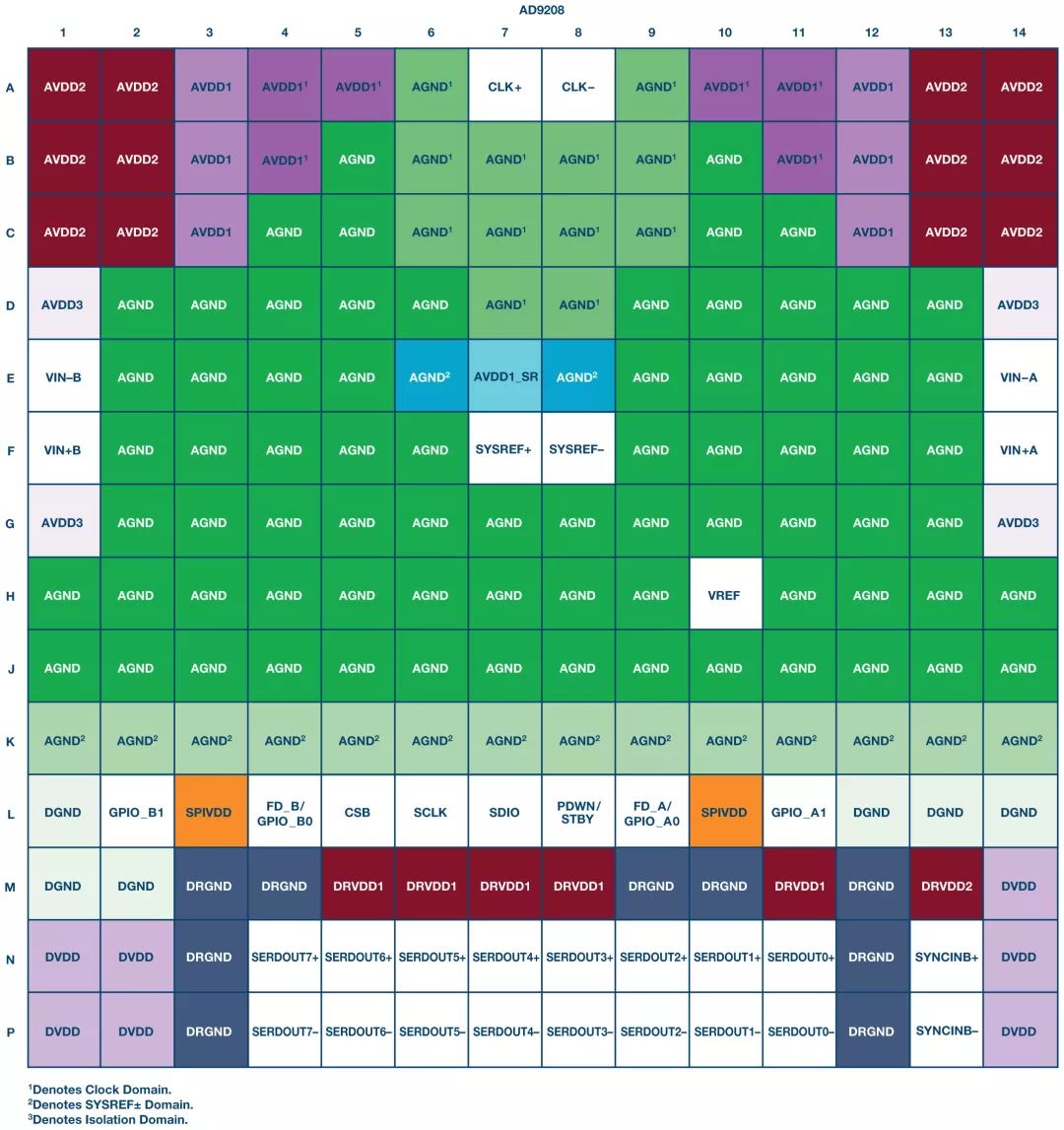

表2:AD9208电源域和接地域

👇点击探索ADI“芯”世界