摘要:将多个异构芯粒集成在一起进行封装是一种具有广阔前景且成本效益高的策略,它能够构建出既灵活又可扩展的系统,并且能有效加速多样化的工作负载。在此基础上,我们提出了Arvon,它使用嵌入式多芯片互连桥(EMIBs)将一个14nm FPGA芯粒和两个紧密排列的高性能22nm DSP芯粒集成在了一起。芯粒间通过一个1.536-Tb/s的高级接口总线(AIB)1.0接口和一个7.68-Tb/s的AIB 2.0接口进行互连。Arvon是可编程的,支持从神经网络(NN)到通信信号处理的各种工作负载。每个DSP芯粒在半精度浮点运算中提供了4.14 TFLOPS的峰值性能,同时保持了1.8 TFLOPS/W的能效。我们还开发了一个能够为FPGA和DSP分配工作负载的编译程序,以此来优化系统的性能和资源利用率。我们使用36-µm-pitch微凸块实现的AIB 2.0接口达到了4 Gb/s/pin的数据传输速率,包括适配器在内的能效为0.10–0.46 pJ/b。其Shoreline带宽密度达到 1.024 Tb/s/mm,areal带宽密度达到1.705 Tb/s/mm²。

I. 介绍

随着机器学习、机器人技术和5G/6G通信等领域的快速发展[1], [2], [3], [4],用于这些领域的DSP工作负载正变得越来越动态和多样化。一个灵活且计算效率高的硬件系统能够很好地满足这些需求。这样的系统可以集成多个组件,包括CPU、FPGA以及DSP加速器等,其中CPU或FPGA提供了系统所需的灵活性,DSP加速器提供了高效的内核加速。

实现这类系统的一种方法是设计并制造一个单片系统级芯片(SoC)。然而,构建一个大型SoC有着高昂的时间成本和经济成本。对此,作为一种成本效益高且可行的替代方案,采用2.5D或3D芯粒集成的异构系统级封装(SiP)为构建大规模系统提供了一条有希望的途径,以实现与单片集成相媲美的性能,同时避免了与单片集成相关的高成本、高风险和高工作量。SiP由称为芯粒(chiplet)的互连组件组成。每个芯粒都包含一个功能模块,可以在最适合的技术节点上制造,以获得最佳性能和效率。由于每个芯粒在尺寸上更小、功能上更专一,因此其设计复杂性会降低,而产量则会提高。通过选择已知良片(KGD)来组装SiP,可以提高系统产量。在未来设想的芯片生态中,我们可以从不同的供应商那里采购经过验证的芯片,并在构建多样化的系统时重复利用它们,这样就能有效地克服在快速开发新系统过程中遇到的挑战和障碍。

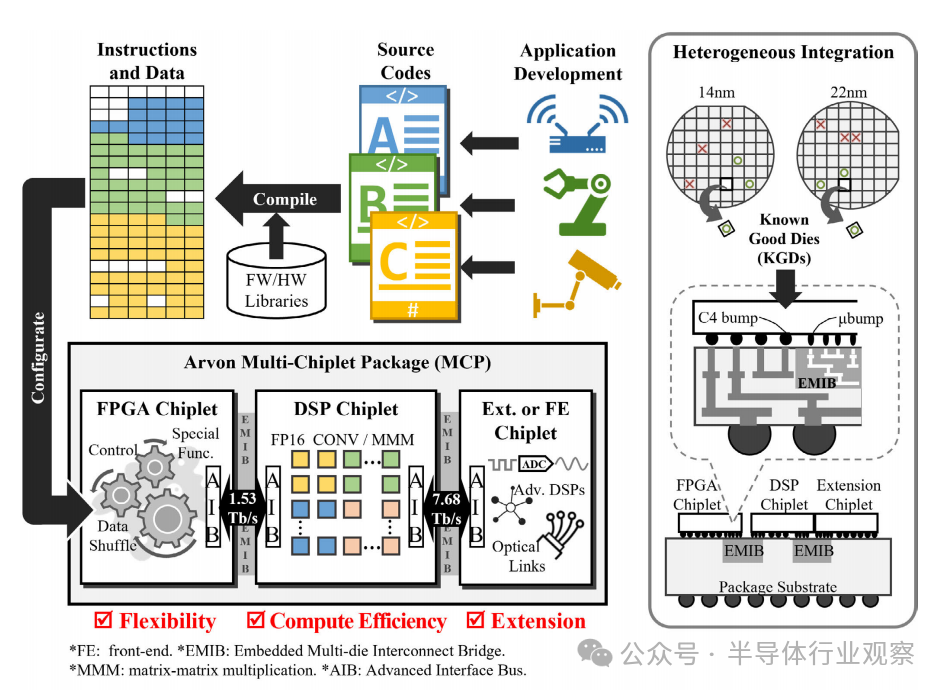

图1展示了一种多功能加速器的SiP解决方案,它整合了一个FPGA芯粒、一个DSP加速器芯粒,以及可能包括的扩展芯粒,比如模数转换器(ADC)或光学收发器。这种异构SiP设计能够灵活地将各种动态DSP工作负载——从机器学习到通信信号处理,映射到其上。FPGA芯粒提供必要的自适应性,DSP芯粒贡献高效的计算能力,而扩展芯粒则提供了与前端(FE)组件如传感器、无线或光接口的连接。在SiP内部,芯粒之间的芯片间接口对于数据传输至关重要,它必须提供足够高的带宽,以确保与单片SoC相匹敌的性能,同时维持较低的每比特能耗,确保整个解决方案保持竞争力。

图1 Arvon SiP通过异构集成FPGA、DSP和FE芯粒,实现灵活的工作负载映射

近期的研究展示了在具有高带宽和高效的die-to-die接口的SiP中集成芯粒的成果[5], [6], [7], [8], [9], [10], [11]。在文献[5]中,两个双Arm核心芯粒集成在chip-on-wafer-on-substrate(CoWoS)上,具有8-Gb/s/pin的低电压封装内互连(LIPINCON)接口。在文献[6]中,36个深度神经网络(DNN)加速器芯粒使用25-Gb/s/pin的地参考信号(GRS)接口[7]集成在有机基板上。在文献[8]和[9]中,四个运行时可重配置的通用数字信号处理器(UDSP)集成在具有 1.1 Gb/s/pin SNR-10 接口的硅片互连结构 (Si-IF) 中介层上。IntAct[10]则在活性硅中介层上集成了六个16核芯粒,使用了1.2-Gb/s/pin的3-D-Plug接口。这些成果代表了同构集成的典型应用,通过将模块化芯粒的多个实例拼接在一起,有效地扩展了计算系统的规模。

在Arvon中,我们展示了不同类型芯粒的异构集成,以构建一个用于DSP工作负载的多功能加速器。Arvon由一个14nm FPGA芯粒和两个通过嵌入式多芯片互连桥(EMIB)技术[12], [13]集成的22nm DSP芯粒组成。我们原型化了第一代和第二代开放式高级接口总线(AIB)芯片间接口,分别称为AIB 1.0和AIB 2.0,用于连接这些芯粒。结果在一个SiP中得到展示,该SiP能够有效地加速各种机器学习和通信DSP工作负载,同时保持较高的硬件利用率。这项工作还展示了AIB 2.0接口,该接口在能效为 0.1 pJ/b的情况下实现了1 Tb/s/mm 的海岸线带宽密度和 1.7 Tb/s/mm²的面积带宽密度。

本文的其余部分安排如下:第二部分概述了Arvon SiP。第三部分详细阐述了AIB接口的设计,包括物理层(PHY)I/O、时钟分布和总线适配。第四部分深入探讨了DSP芯粒及其矢量引擎设计的细节。第五部分讨论了各种工作负载的映射。第六部分介绍了硅片测量和系统评估。最后,第七部分对本文进行了总结。

II. ARVON 系统概述

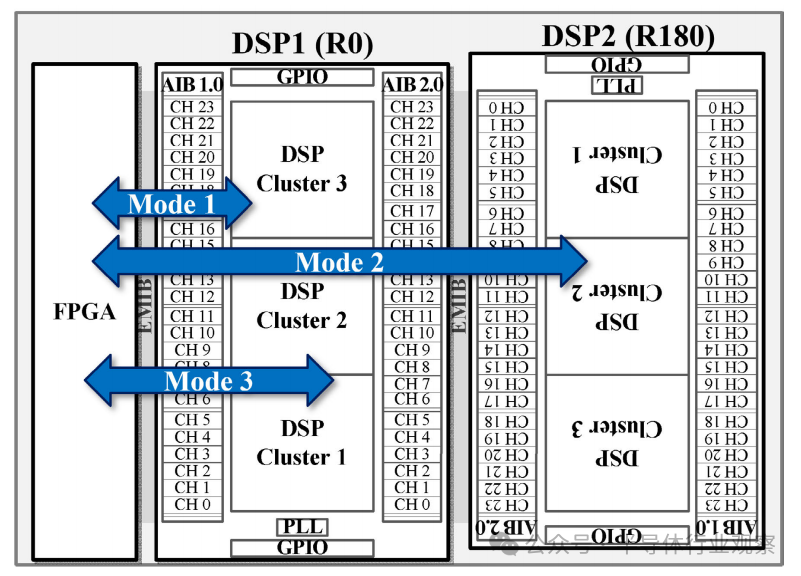

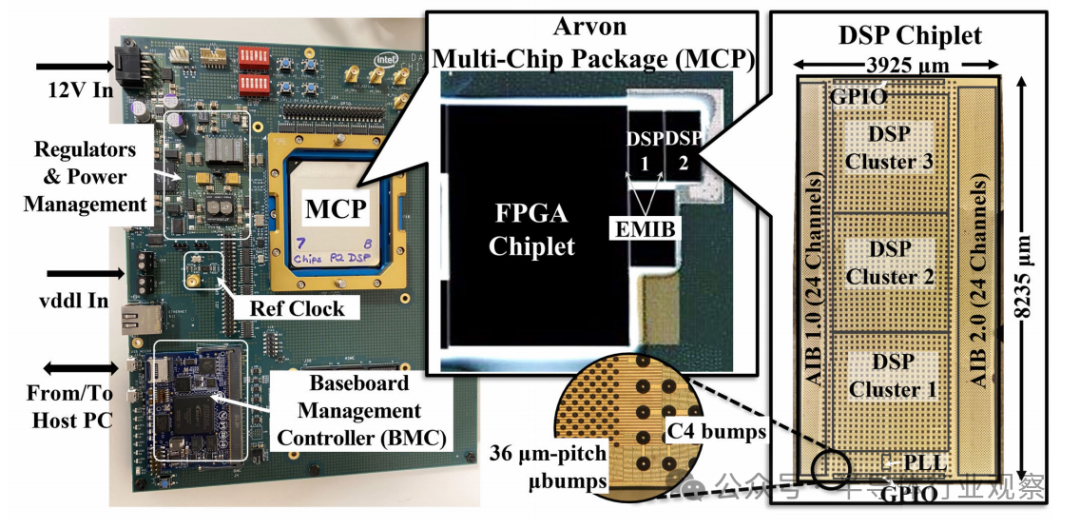

Arvon系统概览如图2所示。该系统包括一个FPGA芯粒和两个DSP芯粒实例,分别命名为DSP1和DSP2。DSP2是DSP1的物理旋转版本。FPGA使用EMIB技术通过AIB 1.0接口连接到DSP1,而DSP1使用EMIB技术通过AIB 2.0接口连接到DSP2。Arvon提供了三种操作模式,如图2所示。在模式1和模式2中,FPGA分别连接到DSP1和DSP2,并将通用计算核心卸载到DSP上面。这些通用核心包括在神经网络(NN)和通信工作负载中至关重要的矩阵乘法(MMM)和二维卷积(conv)。在模式3中,DSP1和DSP2被组合起来以增强计算能力。DSP2也可以被FE芯粒(例如光学tile或 ADC tile)取代,以实现完整的通信或传感系统。

图2 Arvon SiP支持的数据流模式: 在模式1和模式2中,FPGA连接到其中一个DSP; 在模式3中,FPGA同时连接到两个DSP

A

DSP芯粒

DSP 芯粒可为计算密集型工作负载提供卸载和加速功能。DSP芯粒的设计如图2所示。芯粒的两侧都放置了芯片间接口。在西侧,有24个AIB 1.0接口通道,为与FPGA的通信提供1.536 Tb/s的带宽。在东侧,有24个AIB 2.0接口通道,为与另一个DSP的通信提供7.68 Tb/s的带宽。芯粒包含三个DSP集群,每个集群提供1024个16位半精度浮点处理元素(PE)。每个集群最多使用8个AIB 1.0接口通道和8个AIB 2.0接口通道进行输入输出。使用低抖动环形锁相环(PLL)为DSP集群以及AIB 1.0和AIB 2.0接口生成时钟。沿着芯粒顶部和底部有两排通用输入/输出(GPIO)端口,便于进行全局配置和调试。

B

FPGA主机芯粒

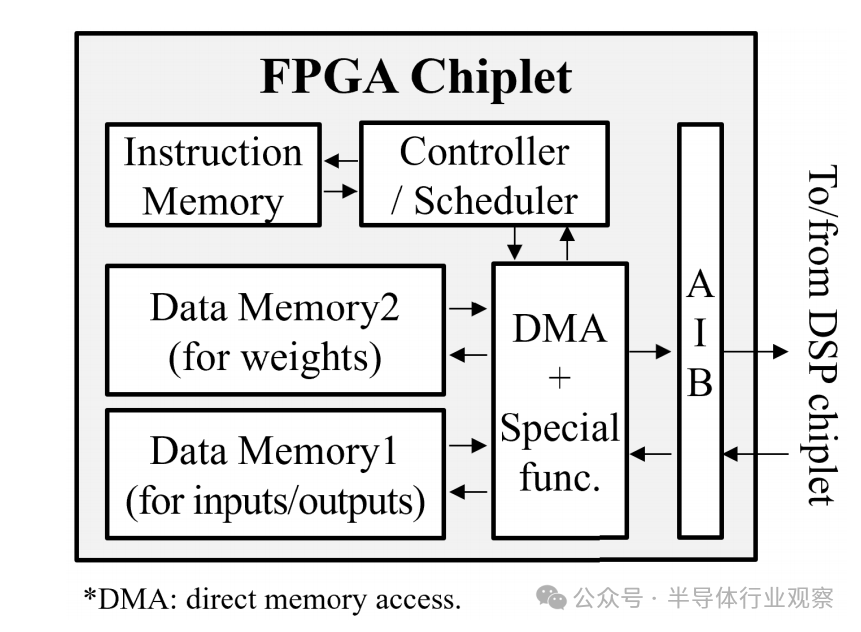

FPGA在实现Arvon的灵活性方面发挥着关键作用。FPGA的可编程逻辑被用来支持各种任务,例如为DSP执行转置和洗牌等数据处理操作。此外,FPGA也可以用来提供DSP上没有的特殊功能,从而能够满足完整的处理需求。

在Arvon中,FPGA充当主机的角色,采用如图3所示的基于指令的处理器形式出现。一个简单的主机处理器配备了指令存储器、用于存储输入输出数据数据和权重数据的数据存储器,以及一个用于管理和协调与DSP芯粒进行数据传输的直接内存访问(DMA)单元。指令用于在运行时配置和重新配置DSP,引导数据存储器和DSP之间的数据流,以及执行DSP的前处理和后处理。

当FPGA内的主处理器触发并从指令存储器中读取首条指令时,工作负载的执行便正式启动。这些指令详细说明了所需的所有信息,包括数据内容、寄存器访问地址、存储器地址、总线地址、DMA进行读写操作的数据长度,以及执行的先后顺序。根据指令,主机处理器生成AXI总线事务以访问发送到DSP的DSP配置寄存器。同时,它也会发布DMA命令,用以从数据存储器读取或写入数据,以及向DSP进行数据的读取和写入。鉴于DSP中矢量引擎的处理时间较快,包括主机处理器在内的FPGA实现得到了高度利用,以最小化延迟并防止任何潜在的瓶颈。

图3 FPGA主机实现示例

III. AIB 芯片间接口

在 DSP 芯粒内,其西侧集成了24个 AIB 1.0 接口通道[14],东侧集成了24个 AIB 2.0 接口通道[14]。AIB 通道由两层组成:适配器层和物理层 I/O 层。适配器层负责协调 DSP 核与物理层 I/O 之间的数据传输。它负责这两个域之间的数据成帧和同步。状态机用于启动 AIB 链路并启用自动时钟相位调整。这种调整有助于确定数据的眼宽和中心。在 AIB 2.0 中,适配器还支持可选的数据总线反转 (DBI),从而减少了总线切换活动并提高了能效。

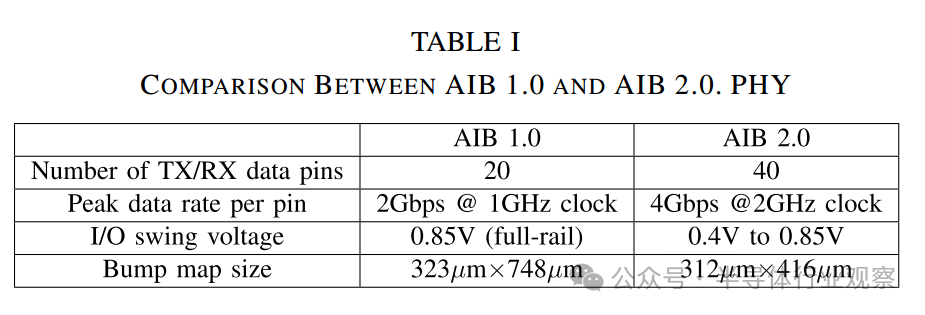

AIB 接口的物理层实现了源同步、短距离、低延迟和并行单端 I/O。在双数据速率(DDR)模式下,AIB 1.0的每个I/O端口通过全轨信号传输,提供从1 Mb/s到2 Gb/s的带宽范围。而AIB 2.0则进一步在DDR模式下,通过0.4 V至全轨信号的摆幅变化,实现了从1 Mb/s至4 Gb/s的带宽,从而显著提升了数据传输速率。单个 AIB 1.0 通道由 96 个引脚组成,其中包括2个 TX 时钟引脚、2个 RX 时钟引脚、20 个 TX 数据引脚、20 个 RX 数据引脚以及用于边带控制的和冗余的附加引脚。相比之下,单个 AIB 2.0 通道由 102 个引脚组成,其中包括两个 TX 时钟引脚、两个 RX 时钟引脚、40 个 TX 数据引脚、40 个 RX 数据引脚以及用于边带控制的和冗余的附加引脚。AIB 2.0 在 AIB 1.0 的基础上进行了改进,它将每个引脚的数据传输速率和每个通道的数据引脚数量增加了一倍,从而将数据传输带宽提高了四倍。此外,AIB 2.0 还通过使用低摆动信号提高了能效。AIB 1.0 和 AIB 2.0 的对比总结见表 I。值得注意的是,AIB 1.0 与 AIB 2.0 有着相似的设计结构。

表 I

A

AIB 2.0 适配器

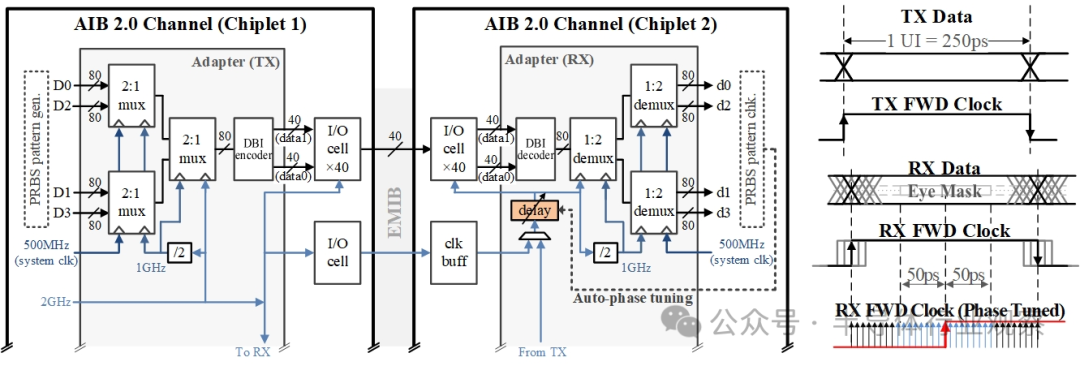

AIB 适配器管理 DSP 核与 PHY I/O 层之间的数据传输。数据路径包括 TX 端的串行器和 RX 端的并行器。图 4 展示了一个数据传输实例。在芯粒 1 中,一个 AIB 2.0 TX 通道每次从 DSP 核收集四条 80 位宽的数据流,DSP 核的时钟频率为 500 MHz。使用两级 2:1 多路复用器实现的串行器将并行数据流转换为单条 80 位宽的数据流进行传输。在可选用的 DBI 之后,80位数据被分为高低两个40位的段,这两个数据段分别发送至40个TX I/O单元的data0和data1引脚。在 DDR 模式下这些TX I/O单元以2 GHz的频率运行,每个单元每次传输2位数据,从而实现了4 Gb/s的有效数据传输速率。差分的2 GHz TX 时钟与数据一起被转发到芯粒2。在芯粒2 中,一个 AIB 2.0 RX 通道负责接收来自40个 RX I/O 单元的80位宽数据。在 DDR 模式下,数据以2 GHz的频率进行采样。随后,接收到的数据流通过并行器处理,其采用两级1:2的解复用器实现,将数据恢复成四路80位宽的数据流。接收到的TX端的时钟信号通过可调节的延时线进行微调,以适配RX端I/O单元的采样时钟需求。

1)自动时钟相位调整:在链路的初始化阶段,RX 时钟相位会进行调整,以便在最佳点对 RX 数据进行采样。适配器采用自动 RX 时钟相位调整机制。TX负责发送一个已知的伪随机二进制序列(PRBS),而后RX则利用可配置的延迟线扫描从TX接收到的时钟信号的延迟,从而监测潜在的错误。通过分析接收到的PRBS序列中的错误模式,RX端能够估算出眼图的边界。这样做的目的是将延迟以及采样点设置在估计的眼图中点。

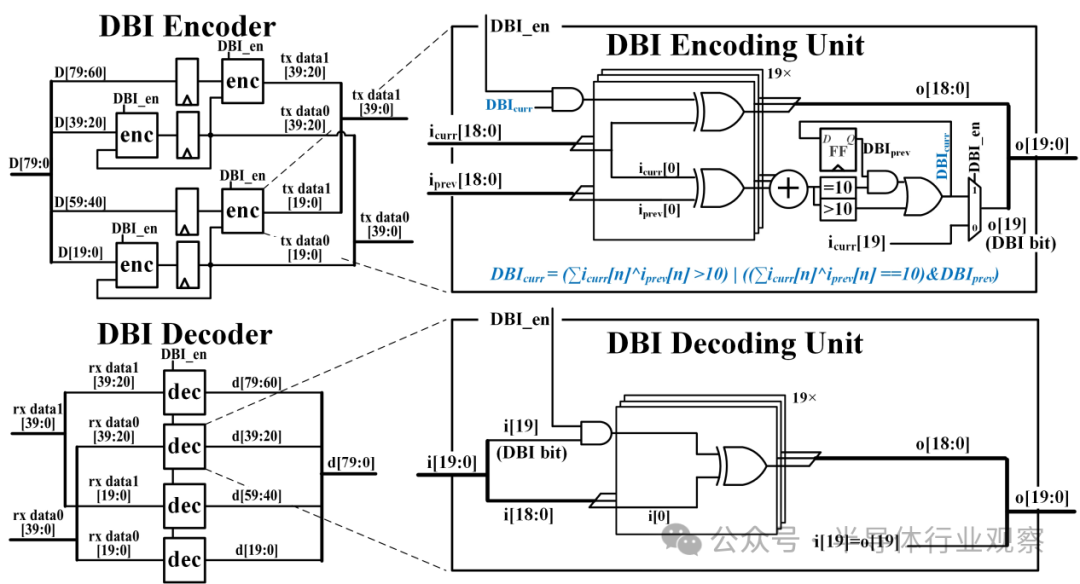

2)数据总线反转(DBI):AIB 2.0支持数据总线反转,这有效地减少了单端及源同步接口中的转换和同步开关输出(SSO)噪声。图5展示了一个1:19比例的DBI编码器和解码器。在TX端,80位数据由四个并行DBI编码单元进行编码。每个单元获取19位数据线的值(在图5中由icurr[18:0]表示),并计算先前编码的数据(iprev[18:0])中已发生转换的位数。如果计数超过10(20比特的一半),则DBI编码单元会反转这些位,并给DBI位分配一个高(HIGH)值。如果计数等于10,并且前一个DBI位已经是高(HIGH),则DBI位保持高(HIGH)。如果上述条件都不满足,数据保持不变,DBI位被设置为低(LOW)。然后,DBI位与编码后的19位数据结合,打包成20位的TX数据,并发送到20个I/O单元。在RX端,采用四个并行DBI解码单元。如果DBI位(接收到的20位数据块的最高位)为高(HIGH),则每个单元将反转接收到的19位数据位,如果DBI位为低(LOW),则数据保持不变。

图4 AIB 2.0 通道顶层图和自动时钟相位调整

图5 1:19比例DBI编码器(上)和解码器(下)

B

AIB 2.0 I/O

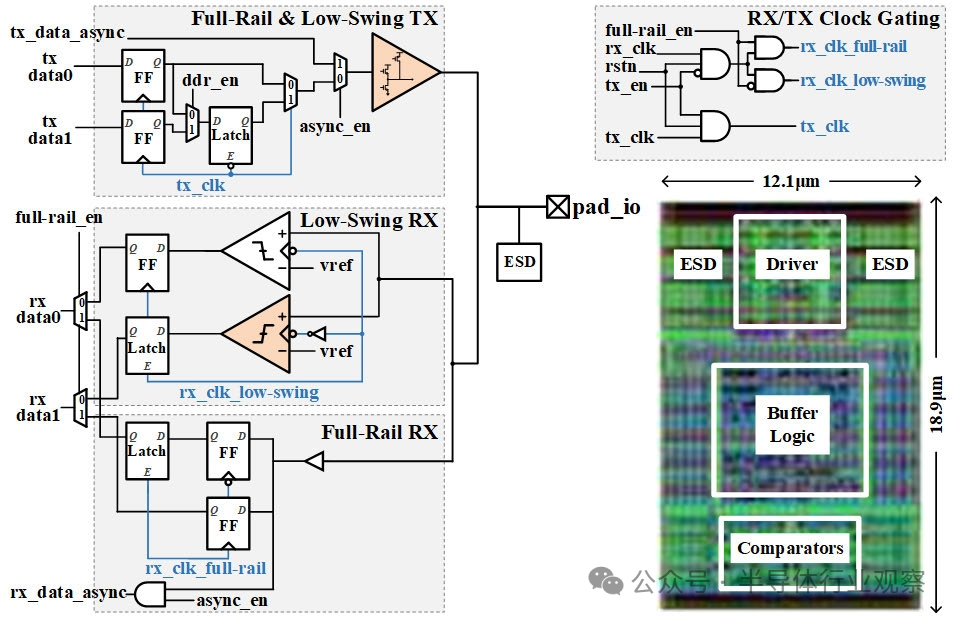

图6展示了一种紧凑型统一 AIB 2.0 I/O 单元设计的原理图和布局。为了实现36 µm微凸块间距的目标,该I/O 单元的布局经过了精心的优化,每个单元都在相应的微凸块下连接,以确保布局符合规定的凸块间距。统一I/O单元支持多种模式。首先,传输方向可以灵活设置为TX或RX模式,这不仅有助于进行冗余修复,也便于芯粒间的灵活连接。在TX模式下,为了降低功耗,RX组件的时钟被门控;反之,在RX模式下,TX组件的时钟被门控。其次,对于 AIB 1.0 和 AIB 2.0,I/O 信号摆幅可设置为全轨,而对于 AIB 2.0,摆幅还可以降低至 0.4 V。第三,传输模式可以设置为单数据速率(SDR)模式或双数据速率(DDR)模式。在DDR模式下,数据0和数据1被串行化后进行传输,其中数据1比数据0延迟半个时钟周期。这意味着,在TX时钟的正边沿,数据0被发送至驱动器,而在负边沿,数据1被发送。在RX端,这一过程则相反,数据通过并行化恢复。SDR模式仅使用数据0,它在TX时钟的正边沿发送到驱动器。最后,I/O 单元可设置为在时钟和其他边带信号的异步模式下运行。

图6 一个统一AIB I/O单元的原理图和布局

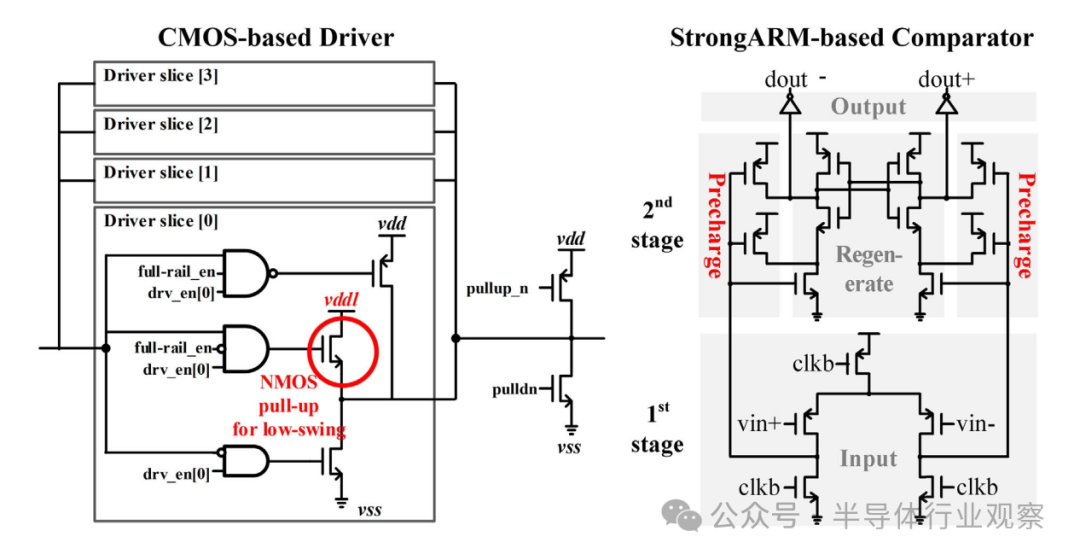

图7 基于 CMOS 的 TX 驱动器(左)和基于 strongARM 的 RX(右)示意图

1)TX驱动器:如图7(左)所示,TX驱动器的设计采用了分段技术,由四部分组成。该设计允许将最多四段驱动器连接起来,以实现可调节的驱动强度,这样就可以根据通道变化灵活调整,同时平衡传输速度和功耗之间的关系。每个驱动器段包括一个用于下拉的NMOS晶体管,以及一个可切换的PMOS或NMOS上拉驱动器,后者可以根据需要提供全轨或低摆幅的驱动力。在低摆幅模式下,NMOS上拉驱动会被适度增强,以确保与下拉驱动力的平衡。此外,系统还允许通过设置弱上拉和下拉来配置初始开机值。

2)RX缓冲器:RX缓冲器的设计区分了全轨输入和低摆输入。对于全轨输入信号,采用了标准单元缓冲器进行处理;而对于低摆输入信号,则使用了再生比较器,如图7(右)所示。该比较器是StrongARM锁存器的优化版本[15], [16],无需校准即可将平均偏移降低到 4.1 mV。此外,设计中还利用PMOS增强了对低波动输入的检测。该设计采用了一个简单的基准电压发生器。比较器可在 2 GHz DDR 频率下可靠地检测低至 0.38 V 的输入。

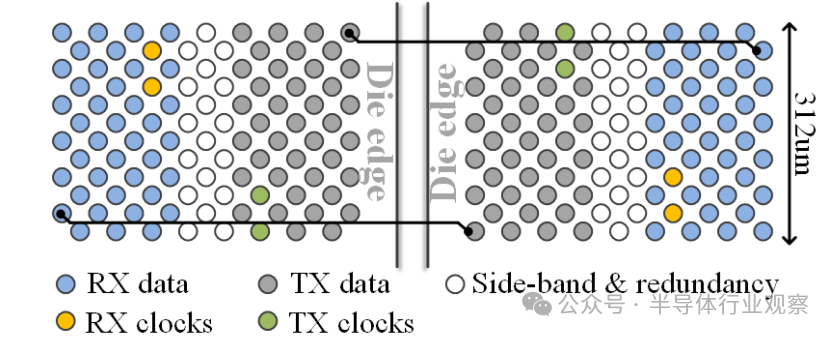

3)凸块图:图8展示了一个AIB 2.0通道的12×17凸块图。该通道由40个TX数据引脚、40个RX数据引脚、2个TX转发时钟引脚、2个RX转发时钟引脚以及18个边带和冗余引脚组成。TX和RX凸块的设计是对称的,使得在EMIB上每对TX-RX的布线长度对等。其总共拥有80个数据引脚,每个引脚的数据速率为4 Gb/s,一个AIB 2.0通道提供了总共320 Gb/s的带宽。该设计的微凸块间距为 36 µm,通道岸线宽度为 312.08 µm,带宽密度达到 1024 Gb/s/mm。

图8 一个AIB 2.0通道的凸块图

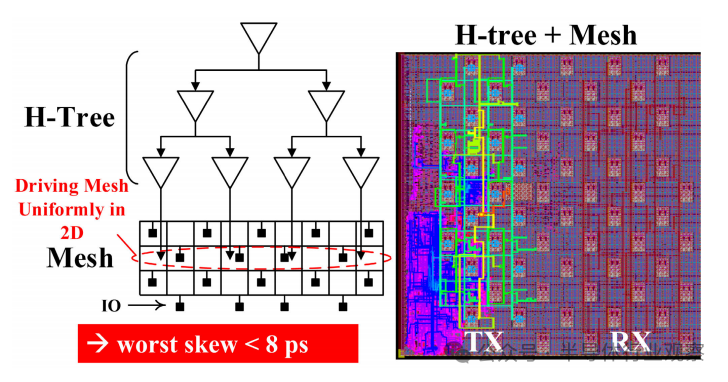

图9 两级时钟分布

C

时钟分布

对于像AIB这样的高速并行I/O接口来说,必须采用低偏斜时钟分布,以确保给定通道中的所有数据引脚相位正确地对齐。如图9所示,我们在每个AIB通道中采用两级时钟分布。上层是一个均衡的H型树状结构,它覆盖了整个通道;而下层则由一个局部时钟网格构成。这种双层设计有效限制了H树的深度,确保了各分支之间更好的平衡。此外,局部时钟网格还能提供更稳定的时钟汇(clock sinks),且不会显著增加功耗。因此,整个时钟网络能够将最坏的时钟偏斜控制在8ps以内。H树和网状时钟网络都是使用IC Compiler II的多源时钟树综合(MSCTS)流程创建和评估的。

IV. DSP集群

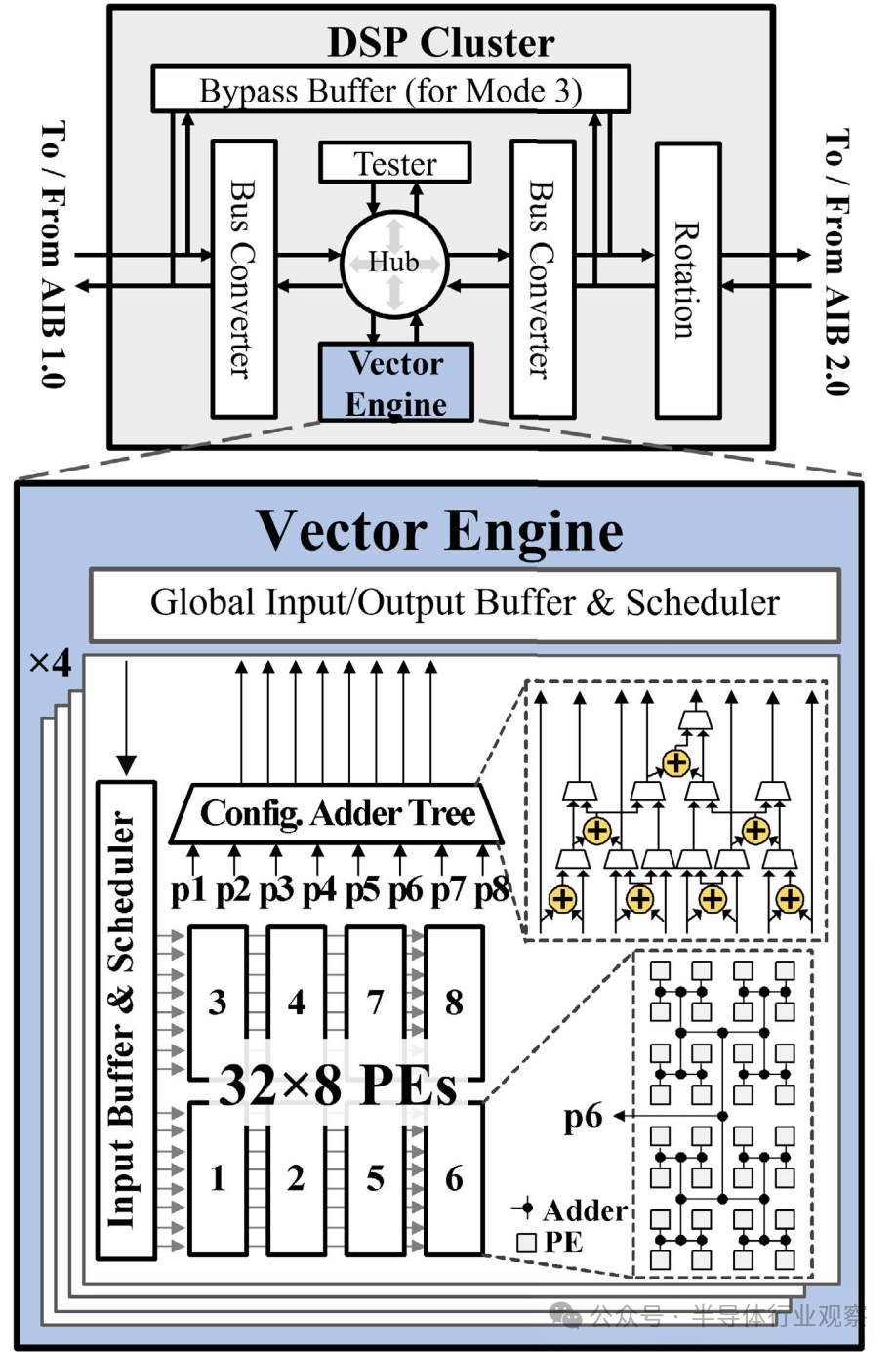

如图10所示,每个DSP集群包括一个灵活的矢量引擎、一个旁路缓冲器、一个用于数据成帧的旋转块、两个用于在多个 AIB 通道之间打包和解包数据的 兼容AXI 的总线转换器,以及一个与AXI兼容的系统总线。此外,还包括一个总线枢纽,用于在矢量引擎和测试器、AIB 1.0接口或AIB 2.0接口之间建立连接。旁路缓冲器支持Arvon的模式2操作,可绕过 DSP1 直接连接 FPGA 和 DSP2。通过这种连接,FPGA 的 AIB 1.0 事务可直接转发到 DSP2 的 AIB 2.0 事务。旋转块反转了AIB接口的通道索引顺序。例如,将 DSP1 连接到 DSP2(DSP1 的旋转版本)时,DSP1 的通道 1-8 连接到 DSP2 的通道 24-17,需要 DSP2 的旋转块来颠倒连接顺序。

图10 DSP集群(上)和矢量引擎(下)

A

矢量引擎

DSP集群的核心部件是矢量引擎,它由四个 2-D 对称阵列实例组成[17]。每个脉动阵列包含256个PE,每个 PE 以半精度浮点格式(FP16)执行乘法运算。这256个PE被分成八个单元,每个单元包含32个PE。每个32-PE单元的求和结果随后输入到一个可配置的加法器树中。可配置的加法器树可以通过选择将八个单元中的哪些单元求和在一起,从而灵活地支持各种工作负载映射。这种设计提供了更短的部分求和累积路径,并通过并发工作负载实现了更高的利用率,这与经典的脉动阵列有所区别。整个矢量引擎总共提供1024个PE,以支持矩阵-矩阵乘法(MMM)和卷积(conv)。最后,实现了一个全局I/O缓冲器和调度器,其使用多播或轮询仲裁技术将输入分配给PE阵列。

通过指令配置,矢量引擎便于输入流的连续计算。矢量引擎还具有高度的映射灵活性。首先,四个脉动阵列可以独立映射。此外,每个阵列内的256个PE可以32个PE为单位进行配置,可适应 1 到 8 个独立的工作负载。

B

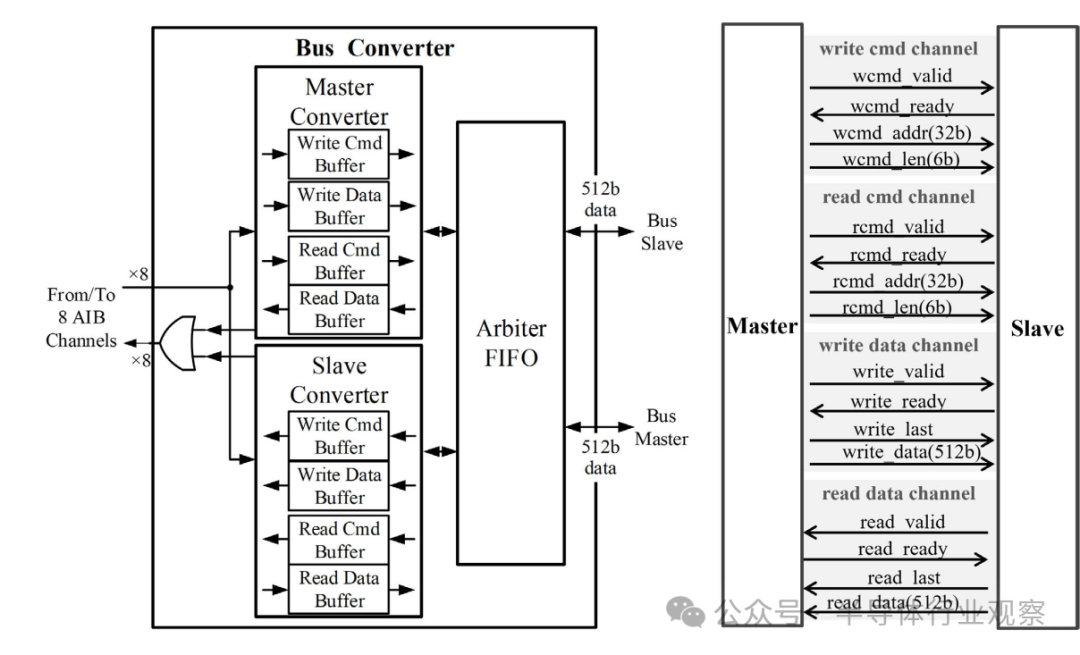

系统总线和总线转换器

AIB 连接由兼容 AXI 的点对点系统总线抽象出来。总线转换器处理跨多个AIB通道的数据打包和解包。它还支持突发模式,以最大限度地利用带宽进行流式传输。系统总线的通道和信号在图11中进行了说明。系统总线由四个通道组成:读命令通道、写命令通道、读数据通道和写数据通道。一个主设备能发出一个带有32位地址和6位突发长度的读写命令,以及512位写数据和写命令。在响应读命令时,从设备将512位读数据发送回主设备。系统总线和AIB通道之间的转换由总线转换器完成。我们在设计总线转换器时采用了基于报头的流方法,以实现高带宽和低延迟。一个矢量引擎最多可使用八个 AIB 通道,以确保最佳利用率。每个AIB通道可以灵活地配置为主设备或从设备,允许根据需要调整TX/RX带宽。

图11 兼容AXI的系统总线:总线转换器(左)以及总线接口通道和信号(右)

V. 工作负载映射

Arvon作为一个多功能的计算平台,它能够支持不同规模的计算任务,并且这些任务的复杂性可以在运行过程中根据需要动态调整。为确保高效的数据处理,必须建立一套系统方法,将工作负载映射到最佳硬件配置和数据布局上。

为了实现这一目标,我们开发了一套编译程序,如图 12 所示。工作负载首先被分割成几个部分,即使用 conv 核或 MMM 核的部分,或二者兼有的部分,这些部分可以通过适当的配置直接映射到Arvon DSP上。此外,一些计算核之间的中间步骤可由FPGA主机执行。具体来说,conv的配置是基于滤波器和输入的大小(R × S × C)制定的,而MMM的配置是基于矩阵的尺寸制定的。随后,工作负载中的conv和MMM核心将根据既定的指令和内存数据配置,被调度并分配给Arvon DSP的矢量引擎。这一分配过程综合考虑了多个关键因素,包括提高资源利用率、增强数据的可重用性,以及最小化端到端的延迟。

图12 工作负载映射的编译流程说明

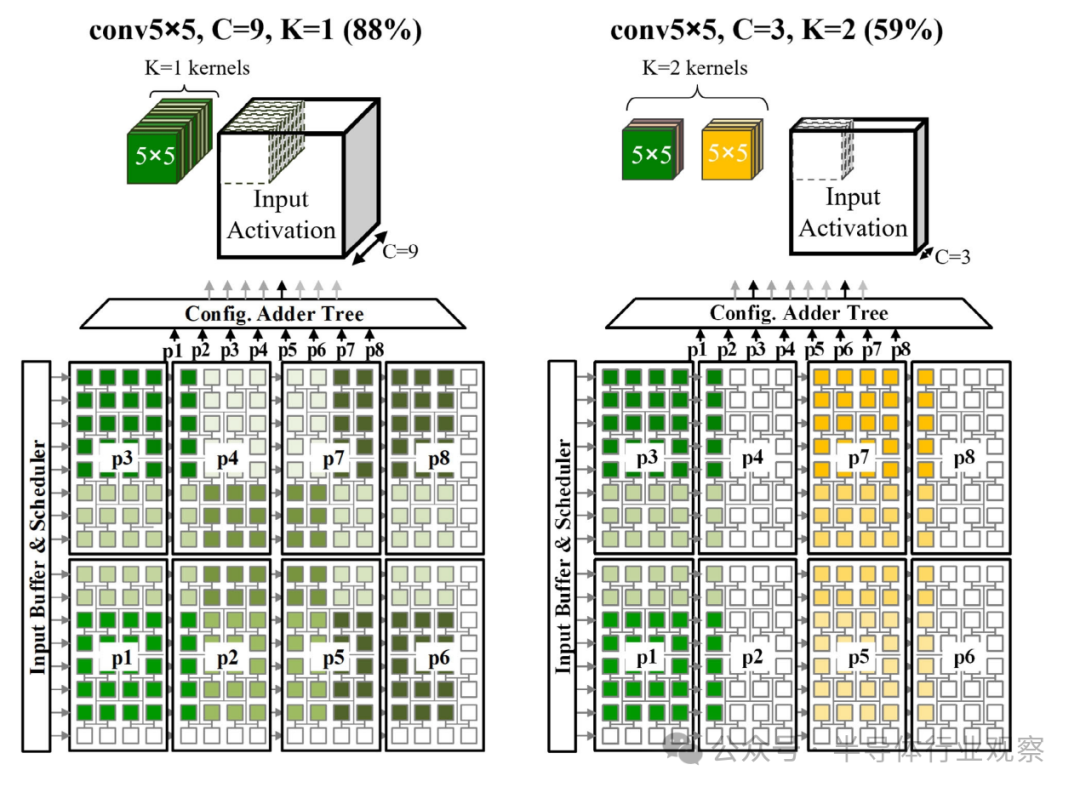

矢量引擎采用静态权重方案,其核心的权重分配给 PE。为了将MMM映射到矢量引擎[17],权重矩阵的每一行都被分配给PE,从而有效地将一维矢量分配到二维阵列中。具有相同权重矩阵的行可以分配给同一组PE。在涉及多个核的多租户场景中,不同权重矩阵的行可以分配给不同的分区,在图12和13中用p1–p8表示。分区输出被定向到可配置加法器树的相应输入端,确保计算出单独的和作为输出。

conv 的权重映射与多租户 MMM 的情况类似,因为其可能涉及多个卷积核。图13展示了两个卷积操作示例的映射。每个卷积核的大小为 R × S × C,并通过在二维中编织三维切片将其展开到二维 PE 阵列中。在滑动卷积窗口下的三维输入激活元素也相应地展开到二维PE数组上。输入激活在PE数组内部保留,以便通过相邻PE之间的脉动数据转发实现水平和/或垂直重用。对于单个卷积核的情况(如图 13 中的第一个示例),可以不考虑分区边界进行映射,从而实现高效利用。然而,当存在多个卷积核时,例如图13中的第二个示例,每个卷积核都需要与分区边界对齐,从而降低了利用率。

图13 不同内核大小的映射示例

VI. 芯片测量与比较

DSP 芯粒采用 22 nm FinFET 技术制造,面积为 32.3 mm²,如图 14 所示。为了构建 Arvon SiP,我们将一个 14 nm FPGA 芯粒和两个 DSP 芯粒通过两个十层 EMIB 相互封装和互连,同时使用 36 微米间距的微凸块。AIB 1.0 侧的平均导线长度为 1.5 毫米,而 AIB 2.0 侧的平均导线长度为 0.85 毫米。

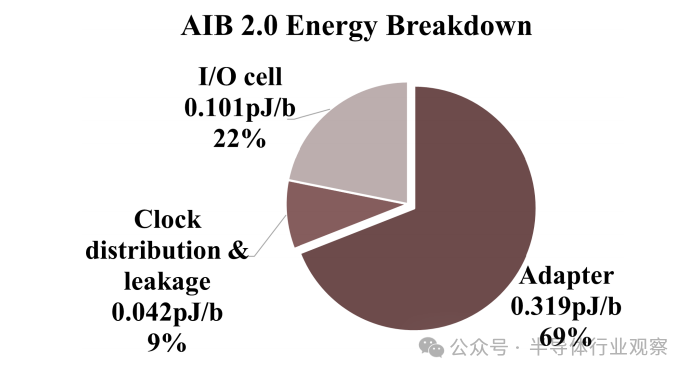

在室温和 0.85 V 的芯粒电压下,每个 DSP 集群的最高工作频率为 675 MHz,功耗为 0.76 W。在这种配置下,DSP 芯粒的峰值性能为 4.14 TFLOPS,功耗效率达到 1.8 TFLOPS/W。在 0.85 V I/O 电压和 800-MHz 时钟(受 FPGA 时钟频率限制)条件下,AIB 1.0 I/O 的功耗为 0.44 pJ/b,包括适配器在内为 0.85 pJ/b,传输延迟为 3.75 ns。在室温条件下,输入/输出电压为 0.4 V,时钟频率为 2 GHz,AIB 2.0 输入/输出每比特消耗 0.10 pJ,包括适配器在内为 0.46 pJ/b,传输延迟为 1.5 ns。AIB 2.0 接口的能耗分解如图 15 所示。适配器的能耗占绝大部分,为 0.32 pJ/b,约占总能耗的 69%。另一方面,I/O 单元仅消耗 0.10 pJ/b,约占总能耗的 22%。I/O 单元能耗较低的原因是利用了 0.4 V 的低信号摆幅。

图14 测试装置、Arvon多芯粒封装和DSP芯粒显微照片

图15 AIB 2.0 接口的能耗分解

图16 能效与区域带宽密度(左)和海岸线带宽密度(右)的关系

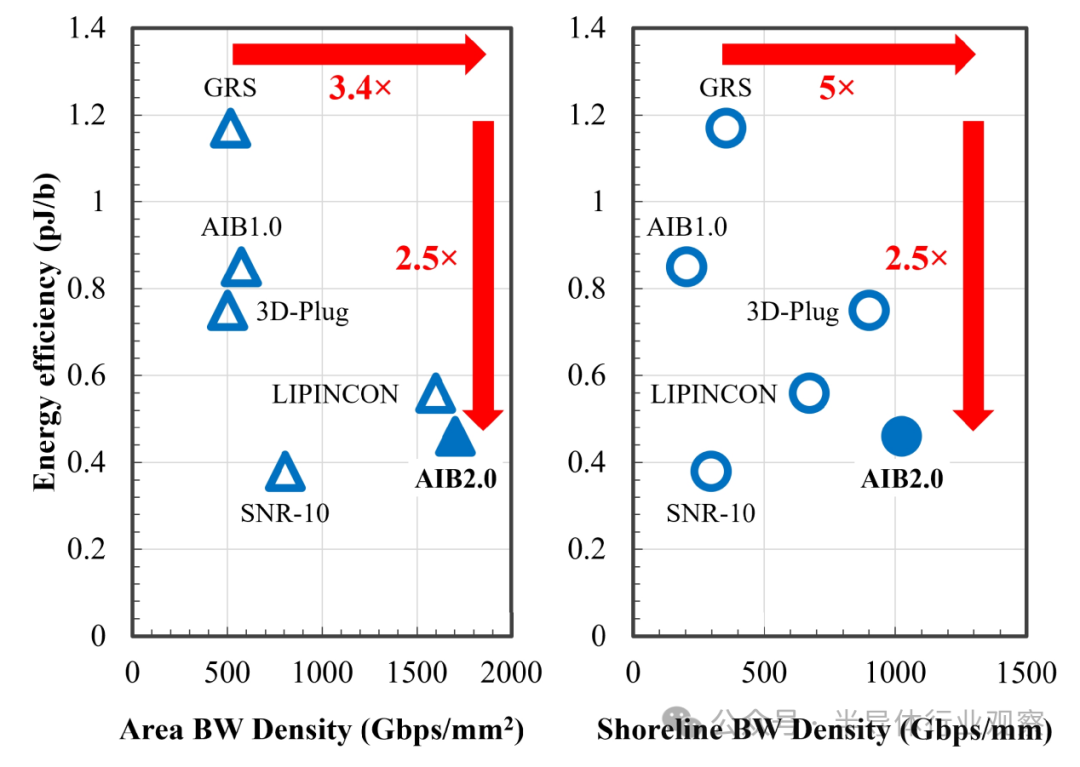

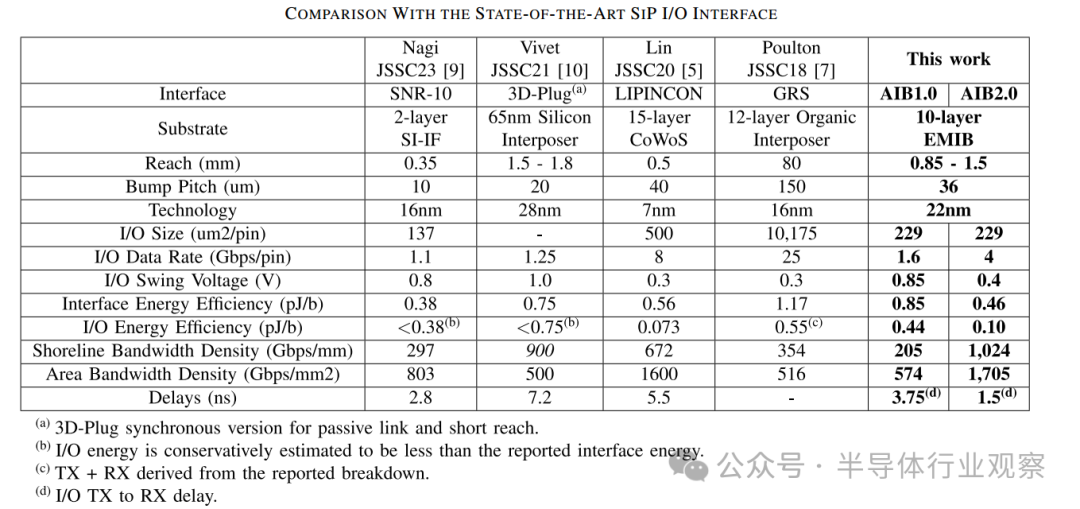

Arvon的AIB I/O 接口与最先进的 SiP I/O 接口的比较见表II。与 AIB 接口类似,SNR-10 [8]、3-D-Plug [10] 和 LIPINCON [5] 也是并行 I/O 接口。其中,LIPINCON 的数据传输率最高,达到 8 Gb/s/pin,I/O 能耗最低,在 0.3 V 信号摆幅下仅为 0.073 pJ/b;3-D-Plug 的带宽密度最高,达到 900 Gb/s/mm 的海岸线;SNR-10 的 I/O 尺寸最小,仅为 137 µm²。GRS [7] 是一种高速串行 I/O 接口,可提供 25 Gb/s/pin,能效为 1.17 pJ/b。我们的 AIB 2.0 原型提供了一个极具吸引力的解决方案,其 I/O 能耗仅为 0.10 pJ/b,如果包括适配器,则为 0.46 pJ/b。如表 II 所示,它还实现了 1.0-Tb/s/mm 的海岸线和 1.7-Tb/s/mm² 面积的最高带宽密度。图 16 比较了芯片间接口的能效、面积带宽密度和海岸线带宽密度。与 GRS 接口相比,AIB 2.0 接口的能效、面积带宽密度和海岸线带宽密度分别提高了 2.5 倍、3.4 倍和 5 倍,优于其他接口。

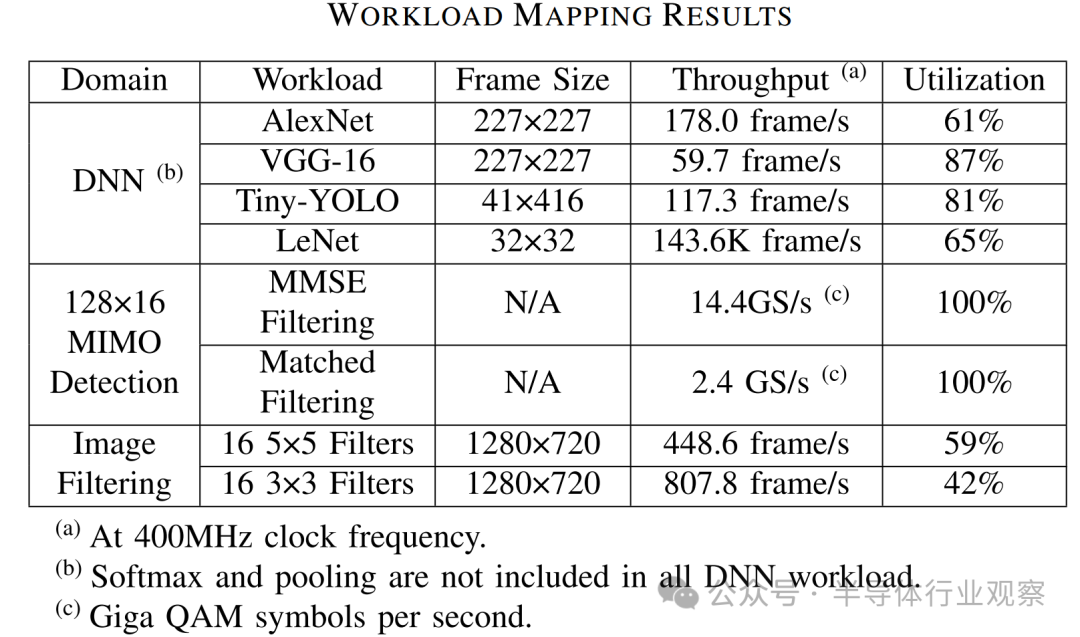

我们展示了可以利用Arvon的各种应用的工作负载映射,包括深度神经网络(DNN)、多输入多输出(MIMO)信号处理和图像滤波。工作负载大小、总体吞吐量和利用率在表III中进行了总结。除了常用的DNN模型外,128×16 MIMO检测工作负载利用128个接收天线来检测16个单天线用户。此任务涉及的处理包括最小均方误差(MMSE)滤波操作,该操作需要使用矩阵-矩阵乘法(MMM)计算滤波矩阵,然后使用MMM应用滤波矩阵。为了执行这些操作,需要使用尺寸为32×256、256×32、32×32和32×1的MMM核来完成此工作负载。这些计算核可以高效地映射到PE阵列,利用率达到100%。图像滤波工作负载涉及16个5×5的滤波器和16个3×3的滤波器,这些二维滤波器应用于1280×720的图像帧,这些操作均需要采用卷积核来进行。不过,由于滤波器尺寸较小,其利用率低于其他工作负载。这些示例工作负载的结果表明,Arvon的异构SiP架构为神经网络(NN)和通信处理提供了灵活性、性能和效率。

表II

表III

VII. 总结

Arvon是一个异构系统级封装(SiP),它使用嵌入式多芯片互连桥(EMIBs)集成了一个FPGA芯粒和两个DSP芯粒。这种集成方式使Arvon不但能够拥有FPGA作为主机的灵活性,还能拥有DSP的高计算性能和效率。

SiP 的主要特点是采用并行、短距离的 AIB 1.0 和 AIB 2.0 接口,用于无缝连接芯粒。输入/输出(I/O)单元设计紧凑,以数字为主,并且可综合。这些单元非常灵活,能够支持多种模式。此外,它们还采用了依赖模式的电源门控和两级时钟分布,从而提高了能效。我们使用 36 微米间距微凸块实现了低摆幅 4-Gb/s AIB 2.0 接口,能效为 0.10 pJ/b,若包括适配器在内则为 0.46 pJ/b,同时拥有1.024-Tb/s/mm 海岸线和 1.705-Tb/s/mm²的面积的带宽密度。该接口采用 与AXI 兼容的总线协议进行抽象,简化了主机和 DSP 的使用。

Arvon中的每个DSP芯粒都采用低延迟的脉动阵列架构,拥有3072个FP16 PE。这些PE按层次分为三个集群,每个集群包含八个32-PE单元。这种细粒度的组织结构允许同时并行执行多个工作负载。每个 DSP 芯粒可提供 4.14 TFLOPS 的峰值性能,功耗效率为 1.8 TFLOPS/W。我们开发了一套将工作负载映射到 Arvon 上的系统程序,并演示了 Arvon 可以加速的各种工作负载,以实现具有竞争力的性能和利用率。

致谢

所表达的观点、意见和/或发现皆属于作者本人,不应被解释为代表国防部或美国政府的官方观点或政策。

感谢电子科技大学集成电路科学与工程学院黄乐天老师与陈飞扬同学在翻译和校正中提供的帮助。

参考文献