本次设计包括基于FPGA的任意波形发生器设计实现和基于FPGA的低通滤波器设计实现。

波形发生器是一种常见的信号源,能够产生多种标准信号和用户定义信号,并保证较高精度和较高稳定性,广泛地应用于电子电路、自动控制系统和数字实验等,诸如电话、电视、收音机、高校通信系统实验等领域都需要用到波形发生器。本次设计基于Verilog HDL语言使用Artix-7系列芯片在EGO1开发板上实现一个简易的任意波形发生器。该波形发生器能够产生正弦波、方波、三角波与锯齿波四种波形,可输出频率有:1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、1Hz。波形类型选择控制字与频率设置控制字通过串口输入。

低通滤波可以简单的认为:设定一个频率点,当信号频率高于这个频率时不能通过,在数字信号中,这个频率点也就是截止频率,当频域高于这个截止频率时,则全部赋值为0。因为在这一处理过程中,让低频信号全部通过,所以称为低通滤波。低通过滤的概念存在于各种不同的领域,诸如电子电路,数据平滑,声学阻挡,图像模糊等领域经常会用到。在数字图像处理领域,从频域看,低通滤波可以对图像进行平滑去噪处理。

本次设计将用两种方式实现低通滤波器。

方法一:利用Vivado自身具备的DDS和FIR的IP核实现;

方法二:通过Verilog编程实现FIR的功能。

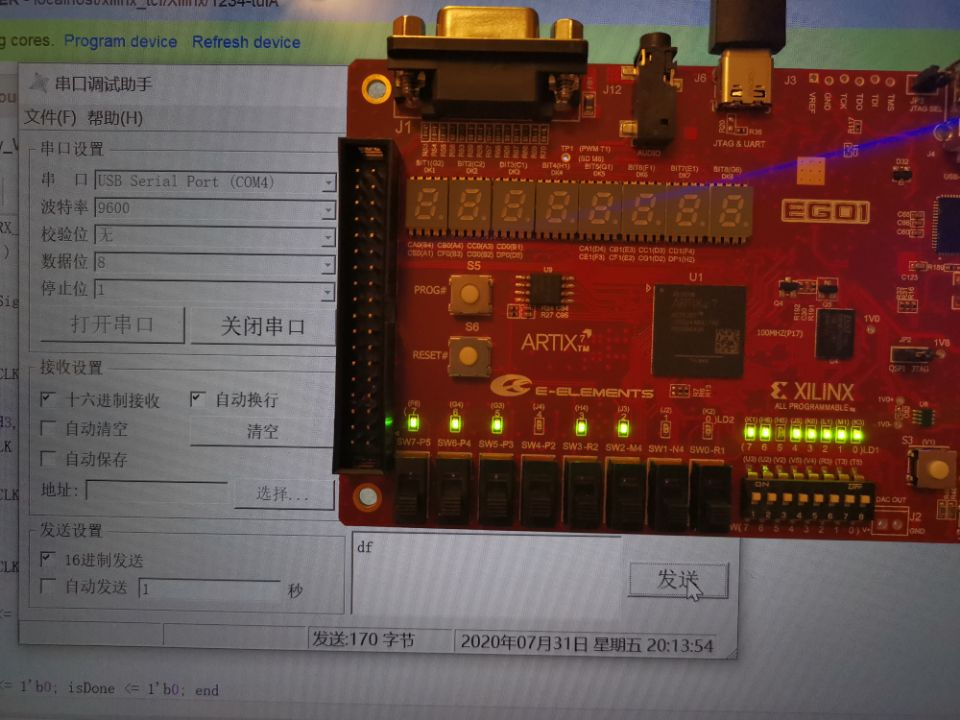

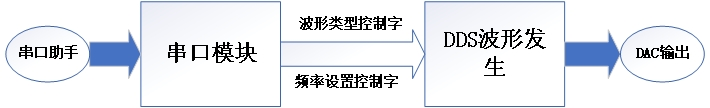

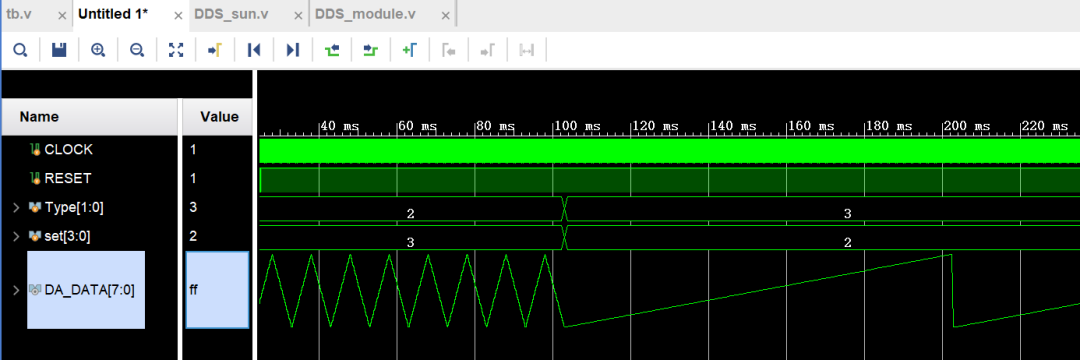

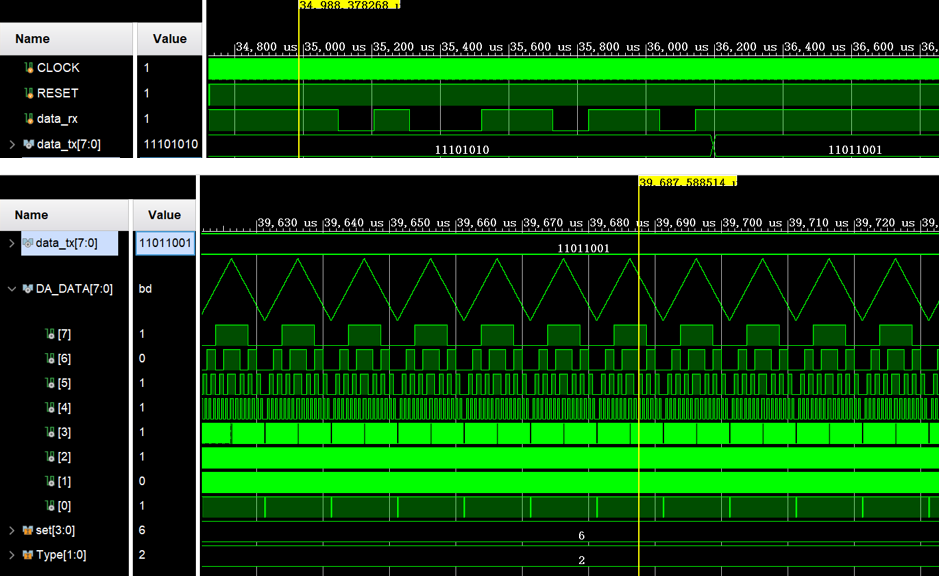

图1 UART串口实现

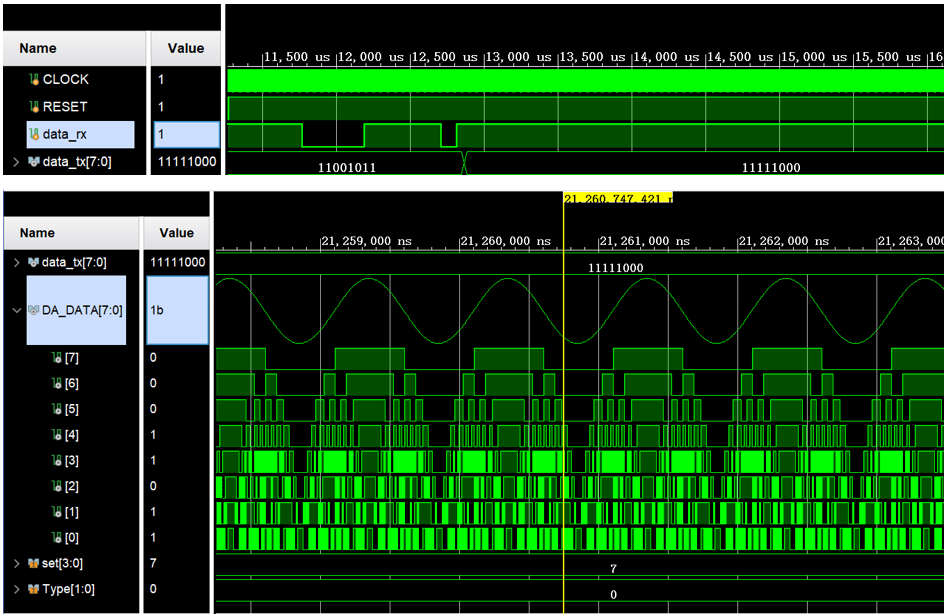

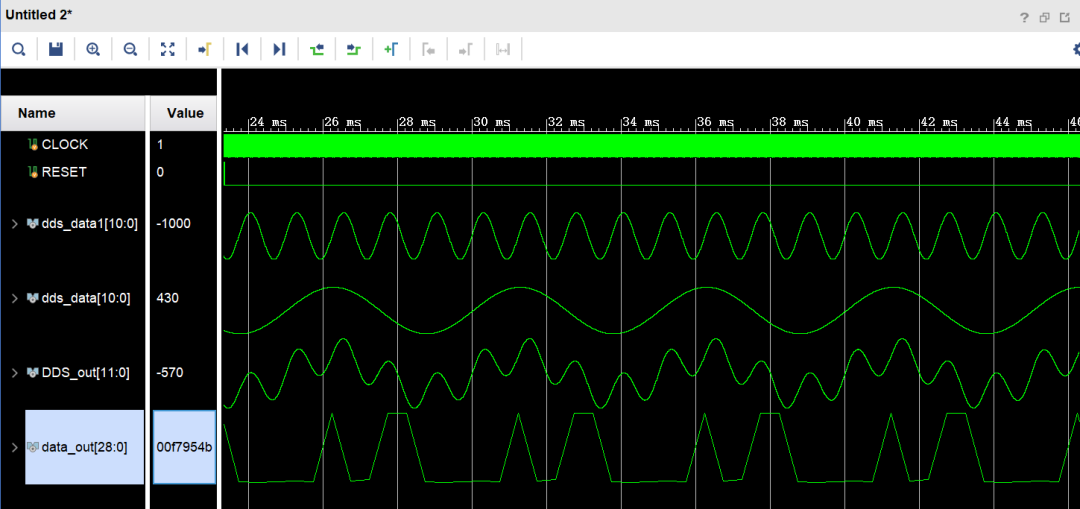

图2 波形发生器仿真

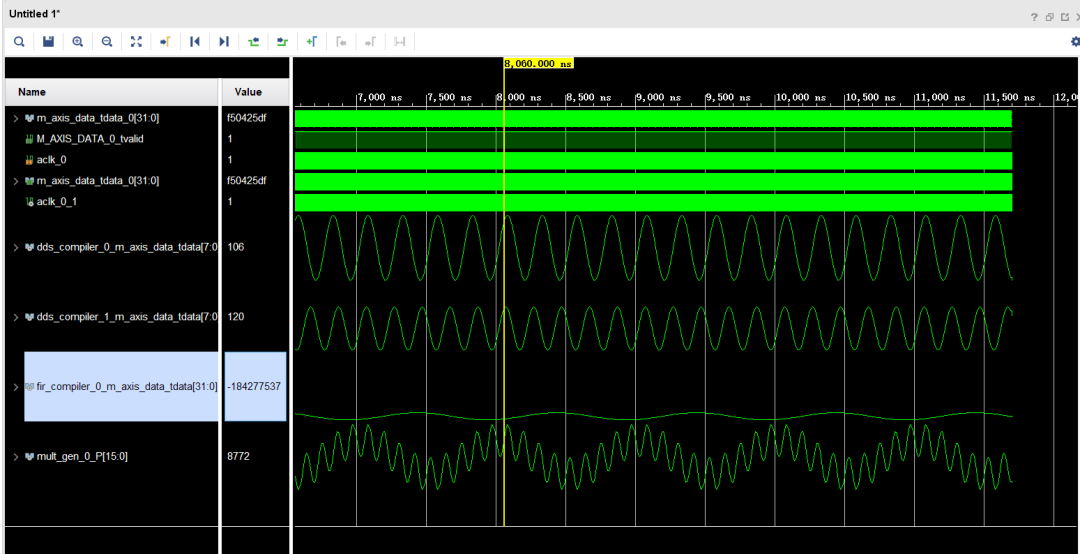

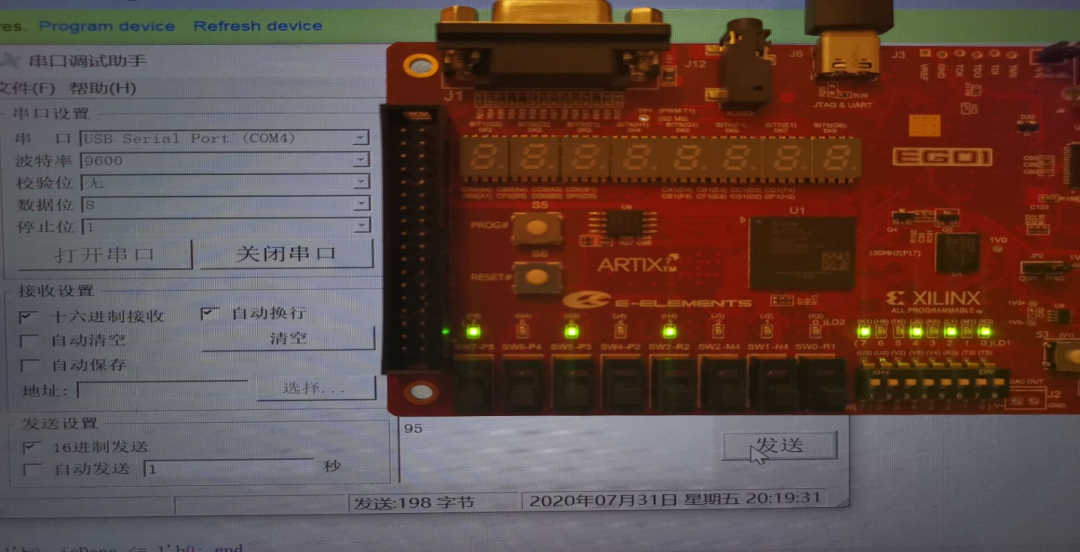

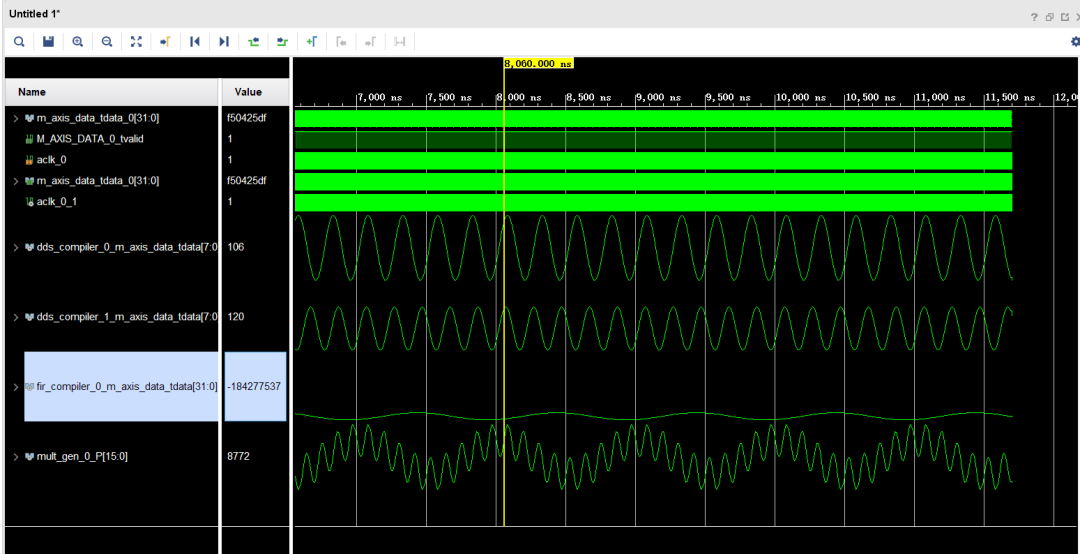

图3 低通滤波器仿真

任意波形发生器:计划产生正弦波、方波、三角波与锯齿波四种波形,可输出频率有:1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、1Hz,利用URAT串口与串口调试助手相连进行控制字数据传输。已经完成全部功能,由于没有示波器,实物调试部分不完整。

低通滤波器:本次设计将用两种方式实现低通滤波器。

方法一:利用Vivado自身具备的DDS和FIR的IP核实现;

方法二:通过Verilog编程实现FIR的功能。

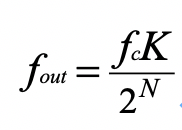

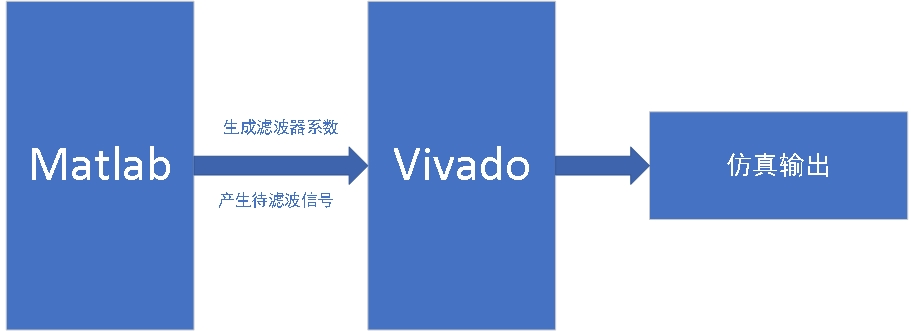

方法一使用Vivado的DDS IP核生成两个正弦信号,频率分别为4MHz和5MHz。同时调用乘法器IP将两个信号进行混频处理,乘法器将混频信号交给FIR IP核进行过滤处理。使用Matlab进行滤波器的参数设计,这里使用窗函数法设计FIR滤波器。窗函数法设计滤波器的基本思想是:选择一种合适的理想频率选择性滤波器,然后将它的冲激响应截短以获得一个具有线性相位和因果的FIR滤波器,因此这种方法的关键是选区某种较好的窗函数,在滤波器性能给定的情况下,尽量选择主瓣窄,旁瓣峰值小的窗函数。设置好以后将FIR滤波器系数导出,将生成好coe文件导入Vivado中FIR IP核中。撰写TestBench文件进行波形仿真。

方法二利用DDS 生成一个由三个正弦波叠加的待滤波信号,两个正弦波的频率分别是200Hz、800Hz。用MATLAB产生频率为500Hz的低通滤波器抽头系数,然后将待滤波信号送入Vivado,用Verilog编写的FIR滤波器进行仿真,观察滤波后的波形。

任意波形发生器:

图4 任意波形发生器系统框图

图5 串口模块设计框图

图6 DDS原理框图

低通滤波器:

图7 低通滤波器设计框图

图8 低通滤波器原理框图

(1)任意波形发生器

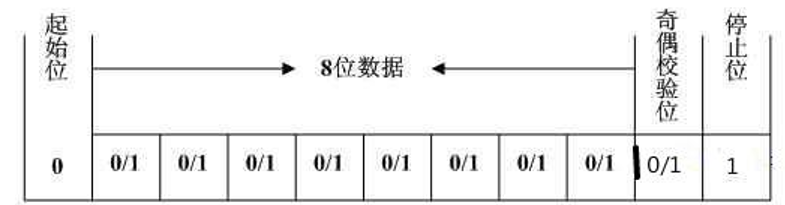

本次设计使用到的是UART串口通信,主要用来接收串口数据发送的数据,字节传输形式:1-0-x-x-x-x-x-x-x-x-0-1,检测到下降沿即-1-0-(起始标志)后开始进行接收字节,将接收到的一一存入寄存器中,8个bit后结束接收,就是简单的1个字节的接收。其协议发送原理:

图9 UART数据帧格式

根据URAT串口的数据帧格式,起始位为0,所以我们需要用一个下降沿检测模块,来判断起始位,然后开始准备接收串口数据。

然后使用一个计数器模块,在1Bit数据传输的时间找到最佳时间来输出读取串口数据。在串口通信中波特率表示每秒能传输的数据位,9600就是每秒能传输9600位,1word=2byte、1byte=8bit,这里的9600位指的是9600bit。每个开发板上都有它的系统时钟,本次设计用的是EGO1开发板,系统时钟是100MHZ,我们假定波特率是9600bit/s传输,那么传输1bit就需要100M/9600个时钟周期。那么在本次设计中传输1bit所需的计数值为10416,将采集数据的时刻放在波特率计数器每次循环技术的中间位置,即5208。

利用一个控制器模块,在下降沿检验通过后的信号与计数器模块输出的读数据时间信号控制下,依次将8位数据放入寄存器之中,然后利用case语句,经过停止位数据后停止数据接收。

最后在串口的总模块中对上述三个模块进行例化,将对应输入输出相连。

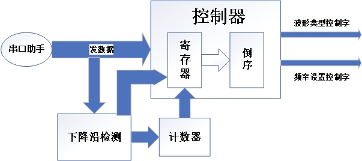

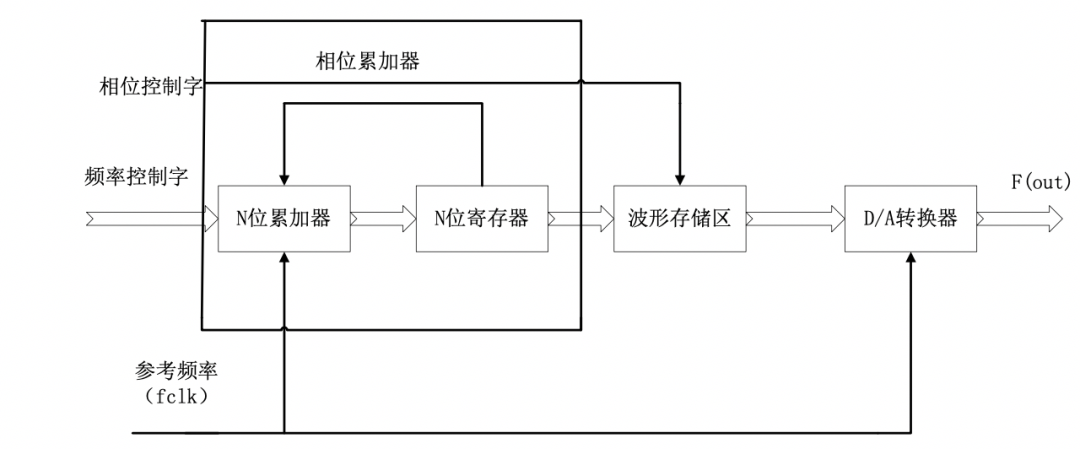

下面根据下图所示的DDS技术原理框图,当一个参考时钟过来 传输一个频率控制字进入累加器在累加器中加入上一个参考时钟的数据,相加后进去寄存器,然后寄存器的输出便是正弦查表的地址,通过这个数据在波形存储区查表,再通过D/A转换器和低通滤波器输出。结合项目功能要求实际分模块实现任意波形发生器。

波形类型控制字与频率设置控制字是分别拿串口助手输入的有效数据位的[7:6]与[5:2]位,我们注意到,串口传输过程是从低字节开始传输的,也就是说我们在串口助手中发送的有效数据为11010011,接收到的数据为11001011,所以需要将接收到的数据倒序然后给到两个控制字的寄存器。

图10 DDS直接数字频率合成技术原理

首先我们利用MATLAB新建脚本(.m文件),键入相应的程序,产生了存放有位宽为8,位深为256的四种波形数据的COE文件。然后在Vivado中利用IP catalog中的Block Memory Generator核。分别新建四个Block Memory Generator核,设置Basic栏中的Memory Type为Single Port ROM,Port A Options 栏中的位宽为8,位深为256,最后在Other Options中,选择加载本地文件选中MATLAB已经生成的正弦波、方波、锯齿波、三角波的COE数据文件,分别将它们放入了不同的Rom中,我们就可以通过Vivado进行编程,在时钟的驱动下,根据地址去读取Rom中的数据然后输出,即可产生波形数据。

我们拿到URAT串口接收的频率控制字后,利用case语句,根据不同的输入,输出不同的频率控制字,关于频率控制字的计算,首先系统的时钟为100MHz,相位累加器为32位,232等于4294967296,想要输出频率为1kHz的信号为例,通过以下的计算公式,得到K约等于42950。

然后在相位累加器中以频率控制字为步长进行周期的加法运算,再将相位累加器的每个值的高位作为地址去读Rom的数据。这里输出的为8位的DAC数据,所以用相位累加器的高八位作为Rom的地址输入。

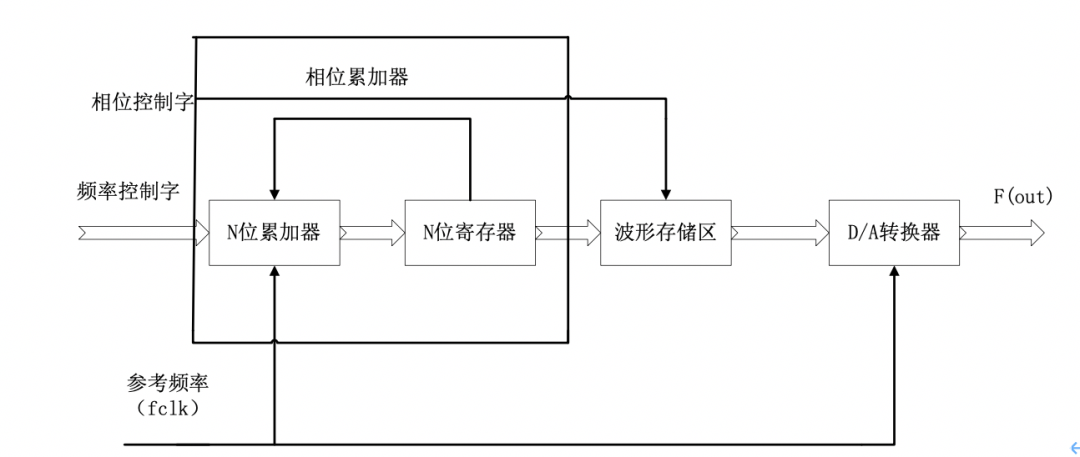

(2)低通滤波器

低通滤波器实现:

方法一:利用Vivado自身具备的DDS和FIR的IP核实现

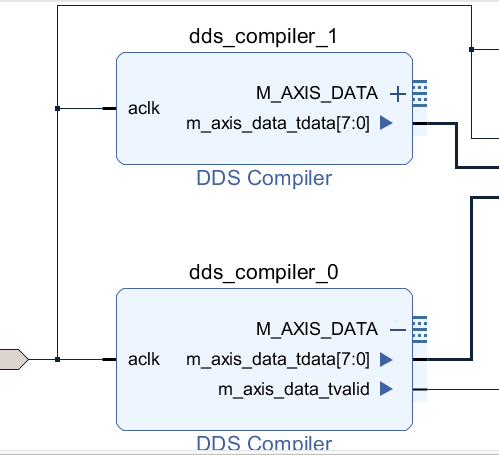

在Vivado中新建工程,创建Block Design,用DDS IP核生成两个正弦波信号,如图11所示。

图11 DDS IP核

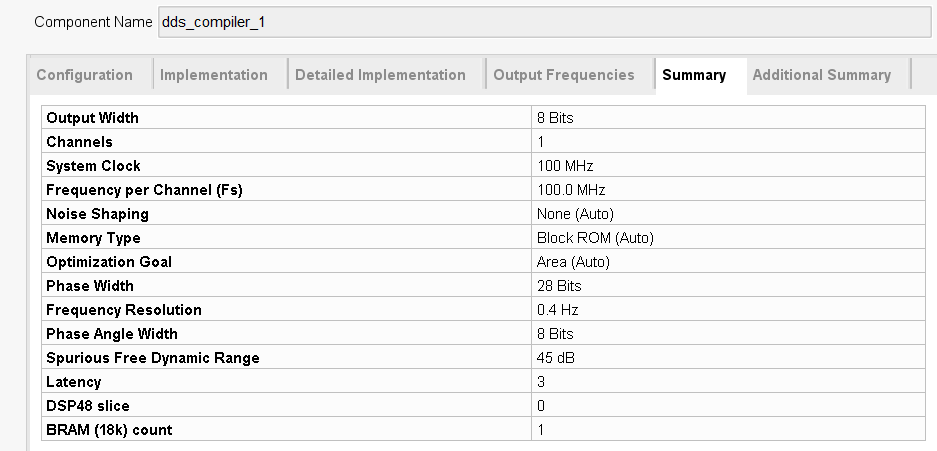

将DDS的参数设置为图12所示。

图12 DDS参数设置

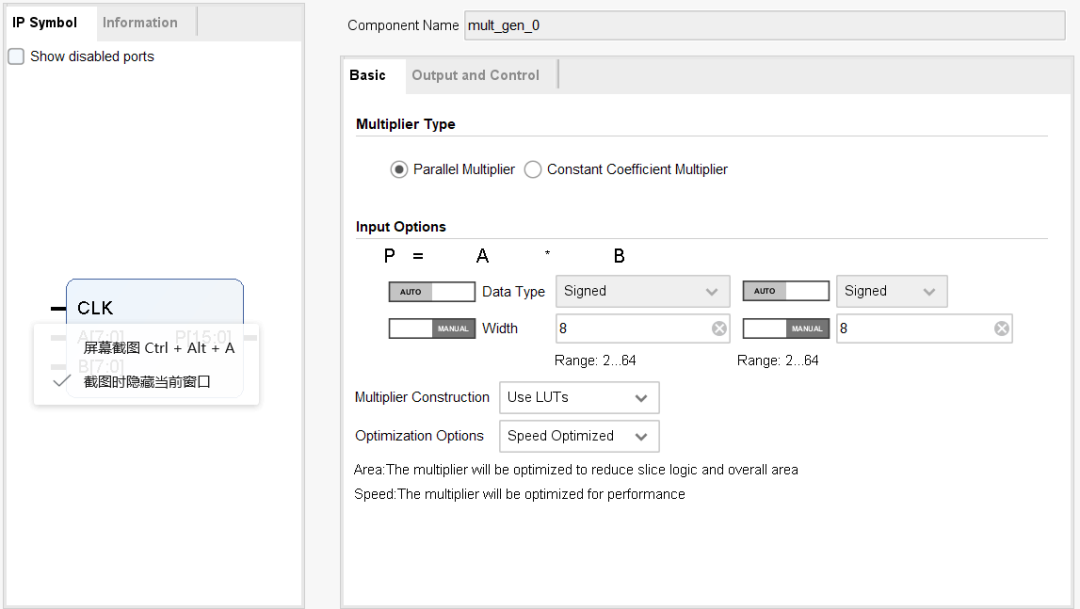

(2)调用乘法器,将两个正弦波信号进行混频处理,乘法器设置如下图13

图13 乘法器IP核参数设置

(3)调用FIR IP核,对其参数进行设置。利用Matlab对滤波器的参数进行设置。在matlab窗口输入fdatool,在弹出的窗口中,在Response Type(滤波器响应类型)一栏中选择Lowpass(低通),Desgned Method(实现方法)选择Window(窗函数实现),即基于窗函数法设计FIR滤波器,我们在Options中选择Hamming窗,Filter Order中选择Special Order,滤波器阶数选择128(阶数越高,滤波效果越好,占用的芯片资源会更多些)Frequency Specializations中单位Units选择MHz,采样频率Fs选择100MHz(根据奈奎斯特低通信号采样定理,采样频率至少高于信号的2倍,实际工程上一般得高于低通信号频率的5-10倍,如果信号频率过高的话,实际的AD采样频率核精度无法达到,所以工程上一般把低通信号经调制后搬到频率很高的载波上,再下变频到中频上用带通采样定理进行AD采样),之前提到采样频率高于信号频率的5-10倍就可以,因为我们这里FIR滤波器时钟是和板卡时钟连接在一起的,没有编写时钟分频模块,所以这里采样频率直接设置为100MHz(一个周期点数为100MHz/2MHz=50,板卡资源会浪费一些,但是不影响),截止频率Fc设为2MHz(1MHz的正弦波通过,9MHz的被滤除),点击View和Design Filter按钮,设计的滤波器时域和频域波形(Time Domain and Frequency domain)以及幅相响应(Magnitude and Phase Response),最后生成coe文件,加载到FIR IP核中。具体设置如下图。

图14 滤波器参数设置

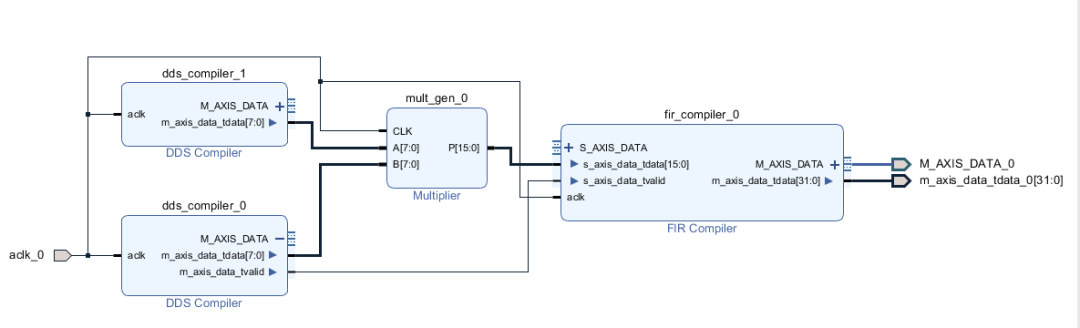

(4)将各IP核之间进行连线,生成顶层模块。如图15。

图15 各IP核连线图

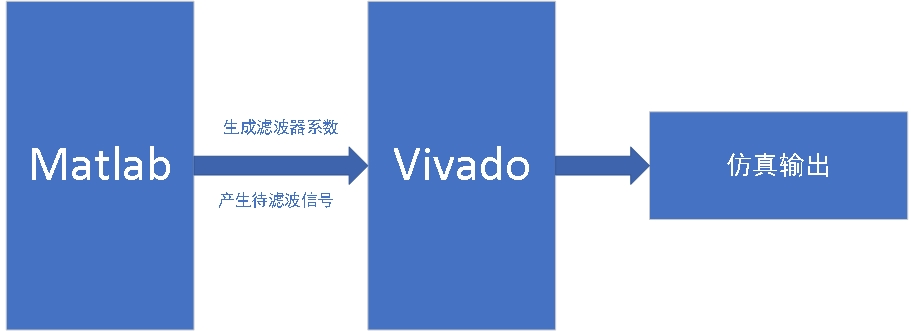

方法二:通过Verilog编程实现FIR的功能。具体设计流程如图16。

图16 设计流程图

(1)利用DDS 生成一个由三个正弦波叠加的待滤波信号,两个正弦波的频率分别是200Hz、800Hz。

(2)用MATLAB产生频率为500Hz的低通滤波器抽头系数,

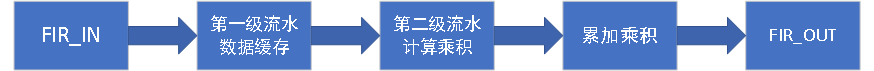

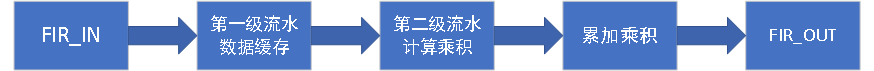

(3)Vivado进行FIR的verilog设计。FIR的代码实现流程如下图7所示。

图17 FIR verilog设计框图

第一级流水线的功能是将输入信号进行延时,每到来一个时钟信号,便将输入信号保存到delay_pipelin1中,然后将剩下的依次移动一位。

第二级流水线的功能是将输入经过延时的信号和滤波器系数相乘,每到来一个时钟便将一个新的乘积结果更新到multi_data中。

累加积乘的主要功能是将乘积累加,累加的结果就是滤波后的信号。

(4)仿真测试,创建TestBench文件进行仿真测试。

已实现功能:产生正弦波、方波、三角波与锯齿波四种波形,可输出频率有:1MHz、100KHz、10KHz、1KHz、100Hz、10Hz、1Hz;利用URAT串口与串口调试助手相连进行控制字数据传输。由于没有示波器,实物调试部分不完整。

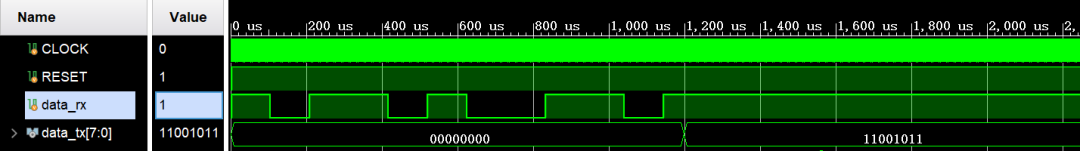

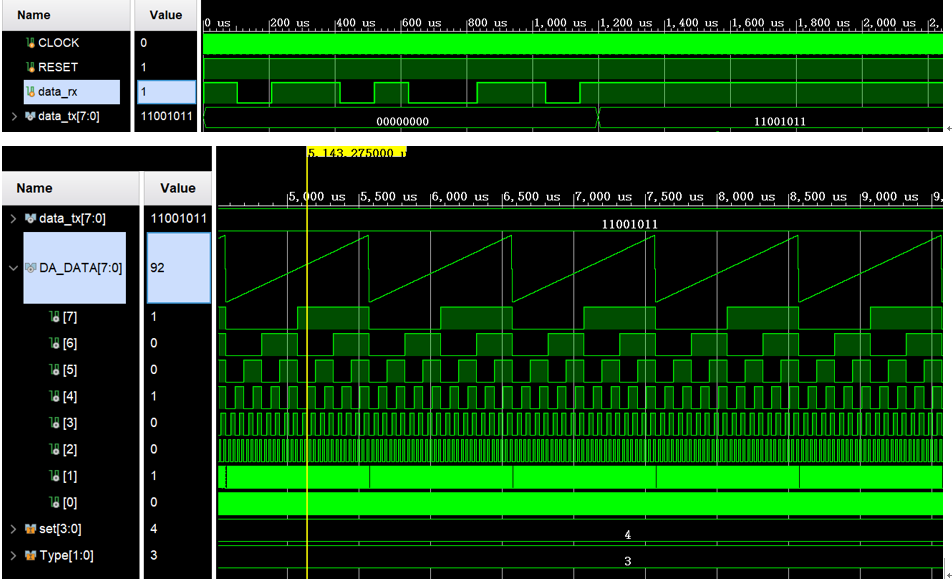

a.串口模块仿真分析:在Testbench中依次给串口数据(data_rx)为10 11010011 011。

图18 URAT串口仿真波形

如上图所示,FPGA接收到的数据为11001011,根据仿真结果,URAT串口测试成功。

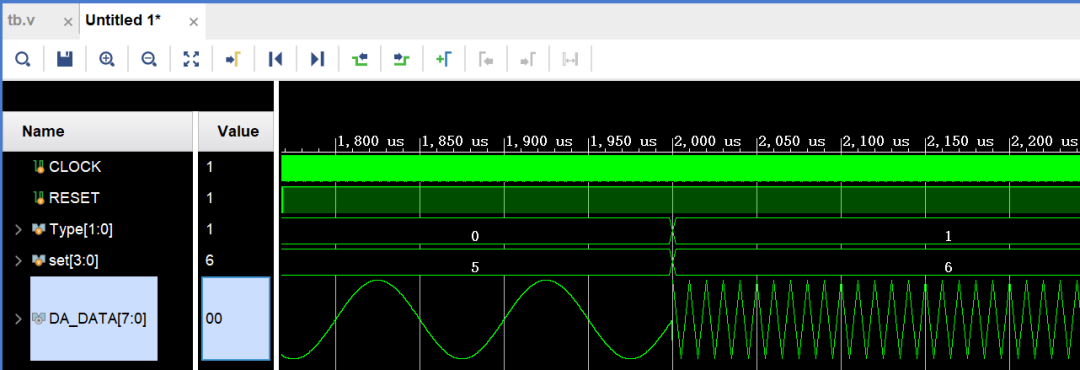

b.任意波形发生模块仿真分析:

图19 波形发生模块仿真1

图20 波形发生模块仿真2

如上图所示,在仿真中分别给波形类型控制字为0、1、2、3,对应频率设置控制字为5、6、3、2。分别产生了频率为10kHz的正弦波、100kHz的三角波、100Hz的三角波、10Hz的锯齿波。其中100kHz的三角波为方波,询问老师后确定是系统显示问题,其波形数据图 所示。根据分析知波形发生器仿真测试成功。

c.系统仿真测试与分析

最后通过顶层模块,例化DDS模块与UART模块,将相应输入输出连接起来,编写仿真激励文件,给串口助手发送值,验证波形输出。

图21 系统仿真测试1

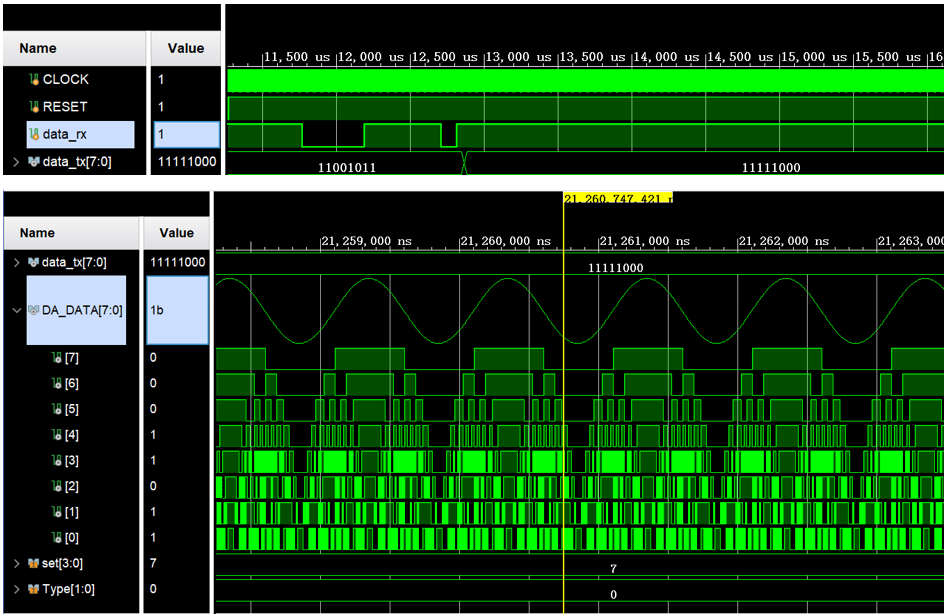

图22 系统仿真测试2

图23 系统仿真测试3

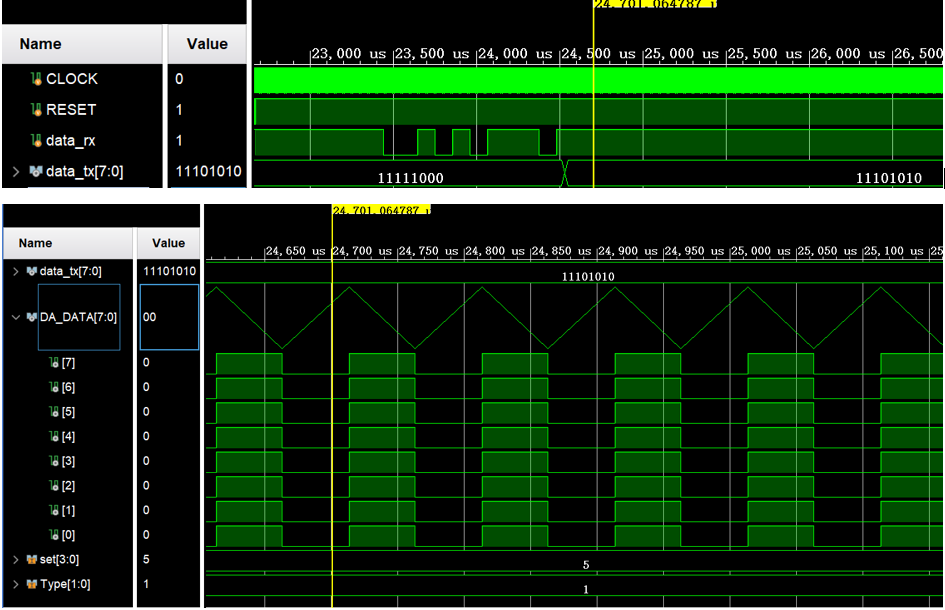

图24 系统仿真测试4

如上所示,根据仿真波形可知,当仿真输入1011010011011,FPGA收到11001011,类型控制字11(3),频率设置控制字0100 (4),输出周期为 1ms(即频率为1KHz)的 锯齿波;

当仿真输入1000011111011,FPGA收到11111000,类型控制字00(0), 频率设置控制字0111(7),输出周期为1000ns频率 (即频率为1MHz )的正弦波;

当仿真输入1001010111011,FPGA收到11101010,类型控制字01(1),频率设置控制字0101(5),输出周期为100us( 即频率为10KHz)的方波 ;

当仿真输入1010011011011,FPGA收到11011001,类型控制字10(2),频率设置控制字0110(6),输出周期为10us(即频率为100KHz)的三角波。

根据分析可知,系统仿真成功,接下来Run Synthesis→Run Implementation,然后在Windows的下拉选项中点击I/O Port,根据EGO1硬件手册上的引脚说明绑定引脚,选择逻辑电平为LVCMOS33,然后保存即可生成引脚约束文件。最后Generate Bitstream→Open Hardware Manager→Open Target→Auto Connect→选中生成的bit文件→Program即可进行实物测试。

图25 系统实物调试

图26 系统实物调试

将BIT文件下入EGO1开发板后,打开串口助手,发送“de”,即二进制的“11011110”,可以观察到代表FPGA串口接收数据的LED1中的八个灯的数据(亮为“1”,灭为“0”)为11011110;发送“95”,即二进制的“10010101”时,LED1灯群展示数据为10010101。由于没有示波器,不能看到波形,仅能通过LED2中的LED7—LED2显示可以看出DDS波形发生器的波形类型控制字与频率设置控制字数据都是对的。至此,正确实现任意波形发生器功能。

低通滤波器通过IP核设计得以实现,仿真波形如下图8所示。

图27 FIR—IP核实现仿真波形

通过上面仿真波形可以看出4MHz和5MHz的正弦混频信号经过FIR低通滤波器后将9MHz的高频正弦信号滤除掉了,输出为我们需要的1MHz低频信号。

图27 FIR-Verilog代码实现仿真波形

如上图所示,DDS产生频率为200Hz与800Hz输入,DDS_out为叠加信号,低通滤波器输出波形不符合功能要求,未能定位到具体原因,仿真错误、系统功能未正确实现。

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+公司/学校+岗位/专业进群

FPGA技术江湖QQ交流群

备注姓名+公司/学校+岗位/专业进群