欢迎再次来到我们的技术专栏——模拟芯视界。在上一期中,我们讨论了使用理想二极管控制器进行 ORing 和电源多路复用的概念和优势、不同类型和架构,以及在汽车系统中使用理想二极管控制器实现 ORing 和电源多路复用的挑战和解决方案。

本次为大家带来的是《适用于隔离式 ADC 信号链解决方案的低 EMI 设计》。该文章将解释 EMI(特别是辐射发射)的来源,并介绍了一些尽可能减少模拟信号链的 EMI 的技术,包括详细的布局示例和测量结果。

引言

如今人们使用的电子设备数量庞大,而这些设备的体积却在不断缩小,这使得电磁干扰 (EMI) 成为电路设计人员面临的一大难题。用于通信、计算和自动化的电路需要近距离工作。产品还必须符合政府的电磁兼容性 (EMC) 规定。几乎每个国家/地区都对在其境内销售的电子产品的 EMC 做出了规定。在美国,联邦通信委员会 (FCC) 监管所有商业(非军事)电磁辐射源,并在美国国家标准协会 (ANSI) 的标准 C63.4 等标准中定义了辐射和传导 EMI 测试程序。欧盟 (EU) 国家对电子设备的电磁辐射和抗扰度都有规定;电磁兼容性指令基本上规定,设备必须符合统一的 EMC 标准,并进行相应的测试和标记。

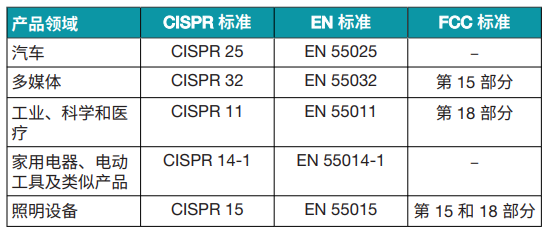

与各类设备相关的 EMC 标准有很多。例如,国际电工委员会 (IEC) 61000 标准涵盖大多数商用产品的抗扰度要求,而国际无线电干扰特别委员会 (CISPR) 32 标准则规定传导和辐射发射的限制。 表 1 列出了相关产品领域的 CISPR、欧洲规范和 FCC 标准。美国和欧盟以外的许多其他国家/地区要么规定要符合 FCC 或欧盟的 EMC 要求,要么有它们自己的要求。美国和欧洲以外国家/地区的法规通常与 FCC 或欧盟的要求类似。

表1: 辐射和传导发射的主要产品标准摘要

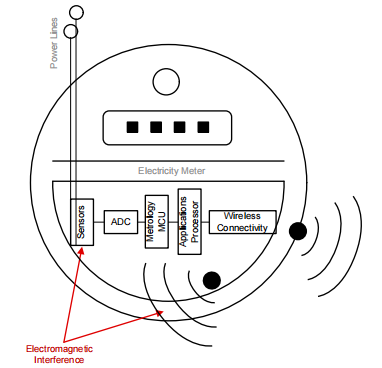

在考虑特定类型的设备(例如智能电表)时,对低 EMI 的需求变得更加明显。智能电表是未来能源分配的重要组成部分。它们向电力公司和终端用户提供实时用电数据,帮助人们监测能源使用情况,并且无需上门抄表。大多数智能电表通过无线通信 连接,如无线 M-Bus 或 ZigBee,或者连接到蜂窝电话网络(GSM、LTE cat NB1 - NB2、2G/3G/5G)。如图 1 所示,智能电表包含一个射频 (RF) 发射器电路,通常与电能计量电路板位于同一外壳内。必须尽可能减少计量电路的辐射发射,以免干扰射频通信,射频通信的工作频率为 800MHz、900MHz、1,800MHz、 2,100MHz 或 2,700MHz 等。计量电路还需要具有抗电磁易感性(能够承受无线通信产生电磁能量),以避免因射频噪声注入灵敏的能量计量前端而产生的计费误差。

本文解释了 EMI(特别是辐射发射)的来源,并介绍了一些尽可能减少模拟信号链的 EMI 的技术,包括详细的布局示例和测量结果。

图1:支持射频的智能电表

EMI 和辐射发射来源

EMC 是指在存在 EMI 的情况下,电气系统在其预定环境中正常运行的能力,以及不成为超出相关标准规定限制的电磁环境干扰源的能力。

EMI 可以是辐射干扰,也可以是传导干扰。辐射干扰以无线电波的形式传播,也称为射频干扰。传导干扰来自传输信号和电力的电缆中电流产生的磁场。

本文重点关注如何尽可能减少辐射干扰。在印刷电路板 (PCB) 上或安装在 PCB 上的集成电路 (IC) 内部,辐射发射的一些主要来源包括:

开关信号,如时钟信号,在数字信号转换过程中电压电平会快速发生变化。这是因为信号中含有高频成分。开关和时钟信号对于 IC 内部和 IC 之间各种元件的同步运行至关重要。

开关稳压器和其他元件,它们会导致电源线上的电流消耗快速变化。

输入/输出缓冲器,尤其是与 USB、HDMI 或以太网等高速接口相关的缓冲器,因为它们需要处理高速信号转换。

在频率高于基波信号时,IC 内部电路中的非线性行为产生的谐波。

IC 互连和结构中的寄生电容、电感和电阻。

触发 ESD 保护电路的静电放电 (ESD) 事件。

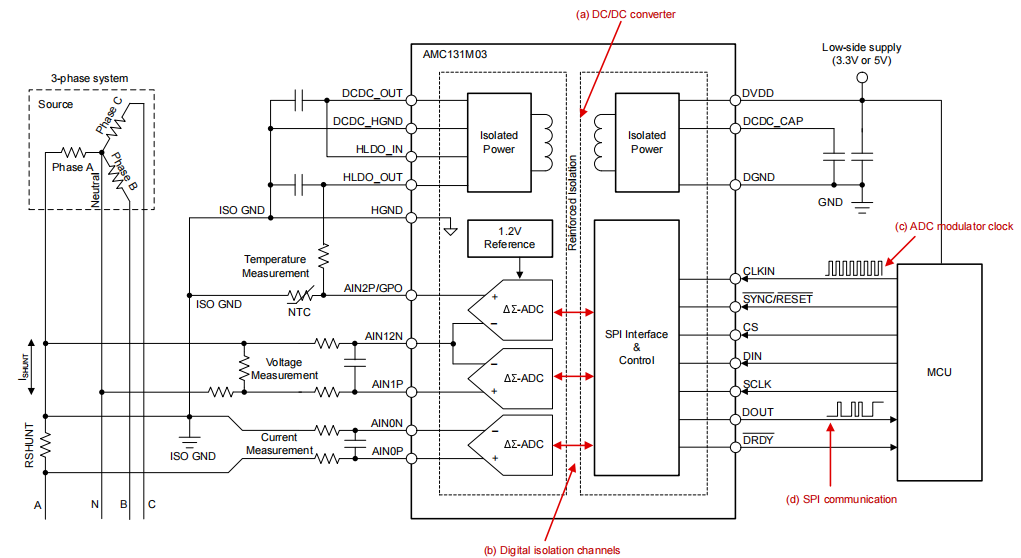

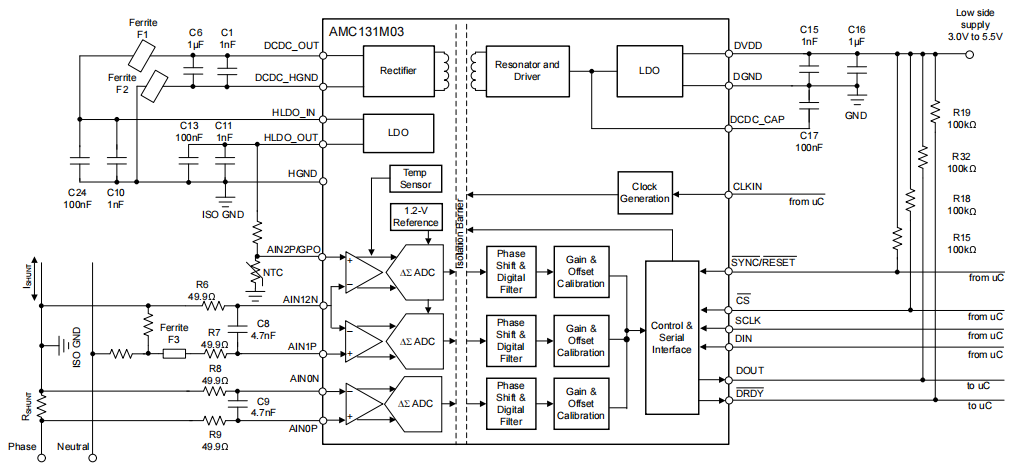

图 2 展示了德州仪器的 AMC131M03 电隔离模数转换器 (ADC) 及其内部架构和印刷电路板上的连接所产生的主要辐射源。ADC 用于三相电能计量应用,图 2 显示了单相(相 A)的电路。信号链的设计目的是提取电压和电流测量值,用于能源监测。ADC 通道 0 通过分流电阻器测量相电流,通道 1 通过电阻分压器测量相电压 。对辐射影响最大的是内部开关直流/直流转换器(图 1 中的 a),它在高压侧产生隔离电源。第二大辐射发射源是数字隔离(图 2 中的 b),因为它是通过堆叠电容屏障使用高频开/关键控传输实现的。此外,时钟信号也会在很宽的频率范围内产生辐射,例如 ADC 调制器时钟 CLKIN(图 2 中的 c),以及 ADC 和微控制器之间的数字通信接口(图 2 中的 d)。

图 2: 带有隔离式 ADC 的模拟信号链和辐射发射源

更大限度减少 EMI 的技术

有几种常见的 PCB 设计技术可以更大限度地减少 EMI :

正确接地:这是减少辐射发射的有效方法之一。小心地接地可避免可能充当天线的接地环路。使用接地平面还有助于减少环路面积,并为信号提供返回路径,从而降低产生 EMI 的可能性。但在其他情况下,接地平面会在敏感节点上形成天线,并增加辐射发射(参阅图 5 中的具体示例)。

元件放置:放置元件时应尽可能减少信号线的长度,尤其是高速信号。将数字和模拟元件分开,以避免干扰。

直而短的布线:以直线方式进行高速布线并尽可能缩短布线,可以更大限度地减少潜在 EMI。此外,还要注意避免在布线中形成直角,因为直角会导致反射和信号损失。

使用去耦电容器:去耦电容器可为高频噪声提供一条短的接地返回路径。将去耦电容器放置在尽可能靠近 IC 电源引脚的位置。

受控阻抗:控制信号布线的阻抗将与信号源和负载的阻抗相匹配,有助于防止可能导致辐射发射的信号反射。

屏蔽:有时,在 PCB 的某些区域使用金属屏蔽层或屏蔽材料可以防止辐射发射。

使用滤波器:滤波器可以阻挡引起辐射发射的某些频率,在电源电路中特别有用。

层堆叠:在多层 PCB 中,应注意各层的排列方式,以尽可能减少 EMI。通常来说,交替使用电源层和接地层是一种很好的做法,因为这有助于减少环路面积,并为信号提供返回路径。顶层和底层接地层可作为内部信号层(如产生辐射发射的时钟)的屏蔽场。

避免时钟谐波:时钟信号会产生谐波,从而干扰电路的其他部分。展频技术有助于分散这些谐波,减少其影响。

EMI 仿真:辐射发射仿真工具有助于在 PCB 设计阶段预测和更大限度地减少 EMI。

图 3 是图 2 中介绍的模拟信号链的详细示意图。

图 3: 图 2 中模拟信号链的详细示意图

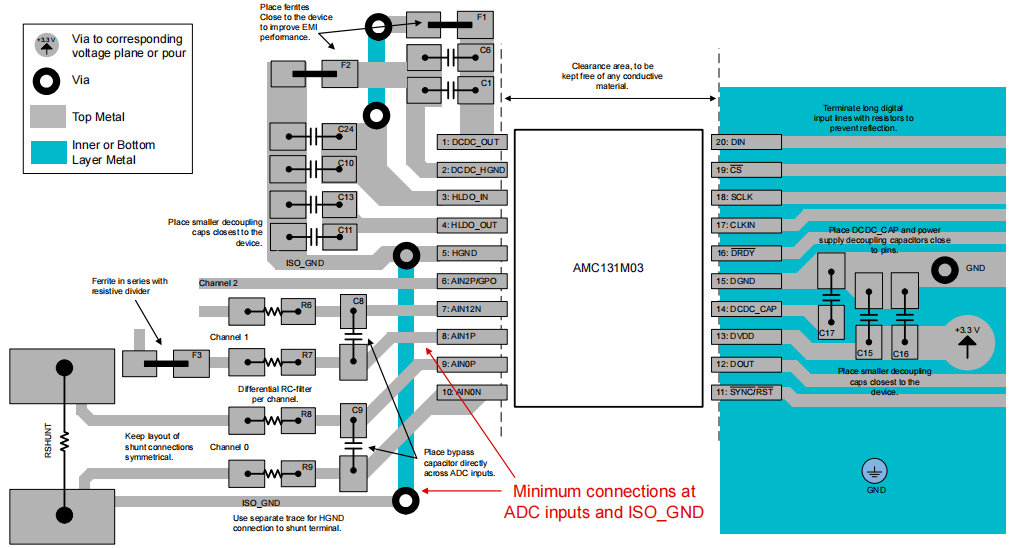

图 4 和图 5 展示了减少辐射发射的技术在 AMC131M03 的相应 PCB 布局中的应用。图 4 显示了一种“良好”布局,高压域(AMC131M03 位置左侧的 PCB 区域)的 ADC 输入和电源线路的布线较短,将旁路电容器 C1、C6、C8、C9、C11、C13、C14 和 C24 放置在靠近 IC 的位置。

减轻 EMI 的一个重要方面是隔离式接地节点 ISO_GND 的接地方案。尽可能缩短布线长度,并且不在高压域放置接地平面,可更大限度地减少该节点上的天线,从而更大限度地减少辐射发射。铁氧体磁珠 F1 和 F2 插入电源连接 DCDC_OUT 和 DCDC_HGND,以阻隔高频噪声。您还可以在具有过高辐射发射的频率处(取决于 PCB 设计)额外放置一个高阻抗铁氧体磁珠 (F3),与电阻分压器串联,用于测量电压。

图 4:良好的PCB布局(低 EMI )

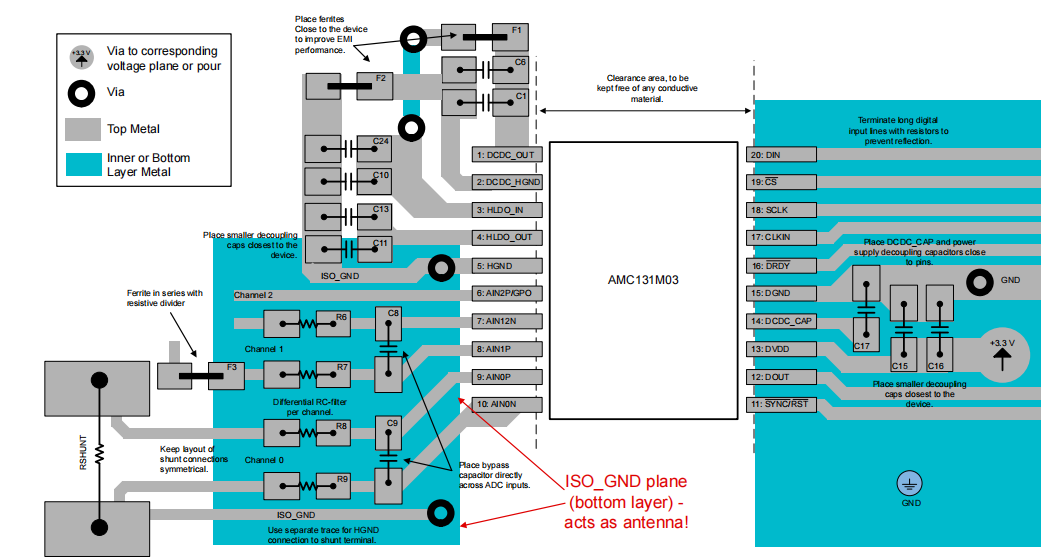

图 5 展示了一种“不良”布局,其中显示接地平面连接到 ISO_GND 节点,这起到天线的作用,会显著增加辐射发射。

图 5:不良 PCB 布局(高 EMI )

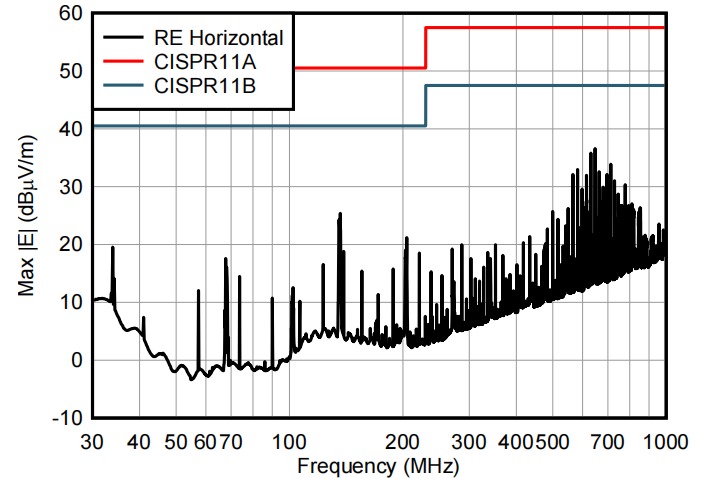

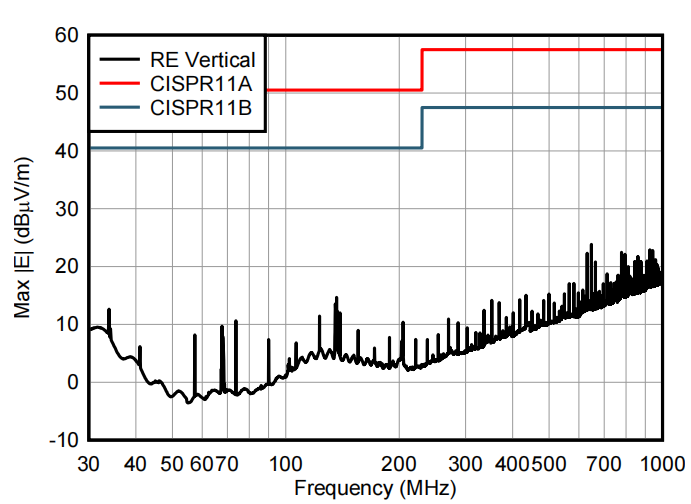

图 6 和图 7 显示了使用图 4 中所示布局实现方案的 AMC131M03 PCB 的辐射发射测量。测量是按照 CISPR 11 的要求进行的,即在半电波暗室中使用为水平和垂直极化配置的宽带天线,距离为 3m。ADC 通过 CLKIN 引脚接收连续时钟,并生成转换结果。不过,在对发射曲线进行表征期间没有串行外设接口通信。该设计符合 CISPR 11 A 级和 B 级标准,裕度为 13dB,为市场上具有数据和电源增强型隔离功能的 ADC 提供超低辐射发射性能。

图 6:水平辐射发射 CISPR

图 7:垂直辐射发射 CISPR 11 测量

结语

为确保电子电路按设计运行,必须防止电磁干扰。同时,电路本身不得产生可能威胁或降低其他设备性能的辐射。要符合 EMC 标准,必须在四个层面上提供 EMI 保护:元件层面、电路板层面、系统层面和整个系统层面 。

本文介绍的技术可更大限度地减少 PCB 设计层面的 EMI,并可轻松应用于一个实际例子,即用于电能计量的具有增强隔离功能的一流精密 ADC 信号链 。凭借使用建议的 EMI 降低技术进行精心设计,该设计可实现相关 EMC 标准要求的足够裕量 。

持续关注我们的专栏,或通过“阅读原文”浏览德州仪器《模拟设计期刊》 电子版,一同探索模拟设计的更多可能!

点击“阅读原文”,浏览《模拟设计期刊》电子版,更多相关知识等待解锁!