本文的目的是介绍高速ADC相关的理论和知识,详细介绍了采样理论、数据手册指标、ADC选型准则和评估方法、时钟抖动和其它一些通用的系统级考虑。另外,一些用户希望通过交织、平均或抖动(dithering)技术进一步提升ADC的性能。

1. 引言

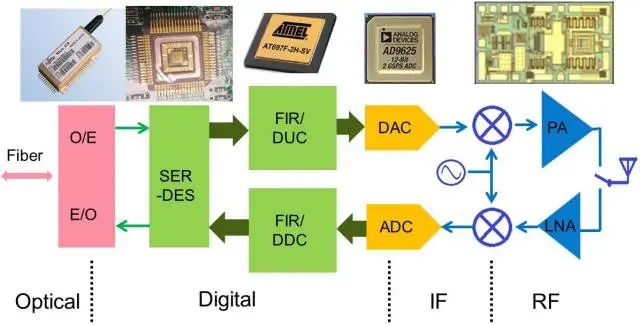

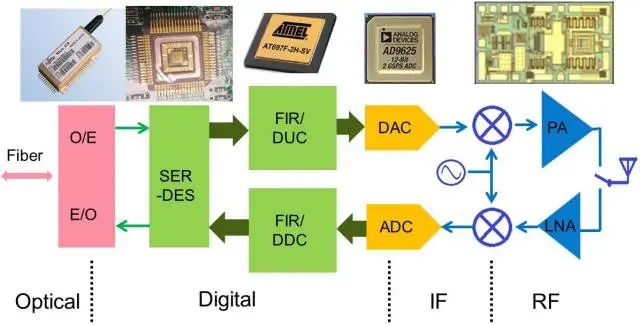

高速 ADC/DAC 在现代全数字雷达中的应用

主要静态指标:

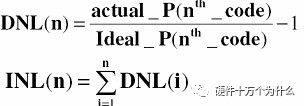

Differential Non-Linearity (DNL)

Integral Non-Linearity (INL)

Offset Error

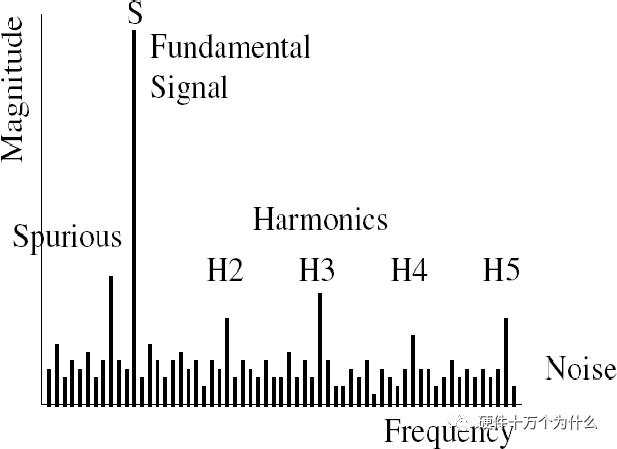

主要动态指标:

Total harmonic distortion (THD)

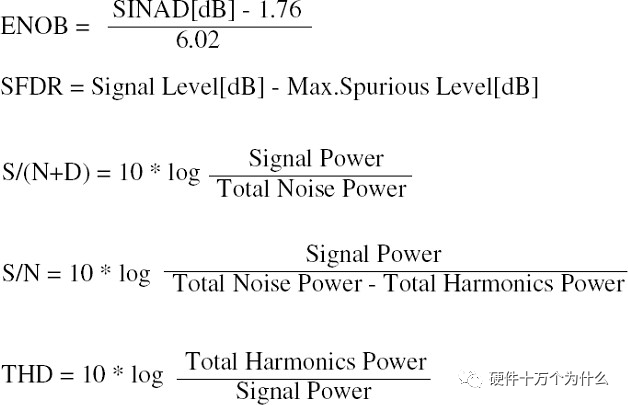

Signal-to-noise plus distortion (SINAD)

Effective Number of Bits (ENOB)

Signal-to-noise ratio (SNR)

Spurious free dynamic range (SFDR)

通过 FFT 频谱分析测试动态参数

2. 频谱性能术语

3. 奈奎斯特、混叠、欠采样、过采样和带宽

4.ADC管脚接口

一般来说,ADC包括以下6种接口:

模拟输入

参考/共模模式

时钟输入

数字输出

电源

GND

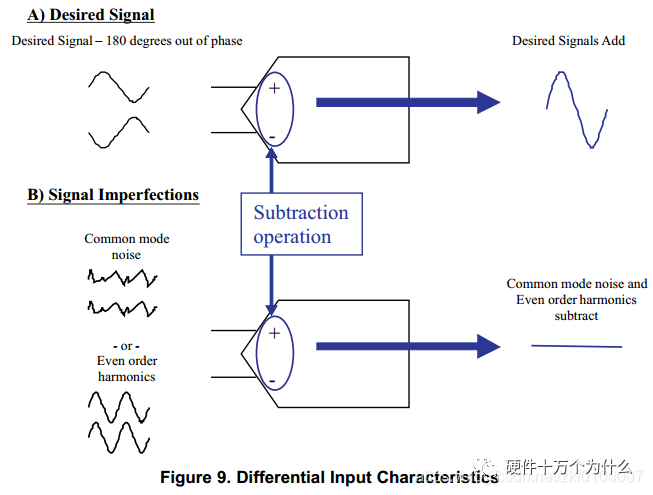

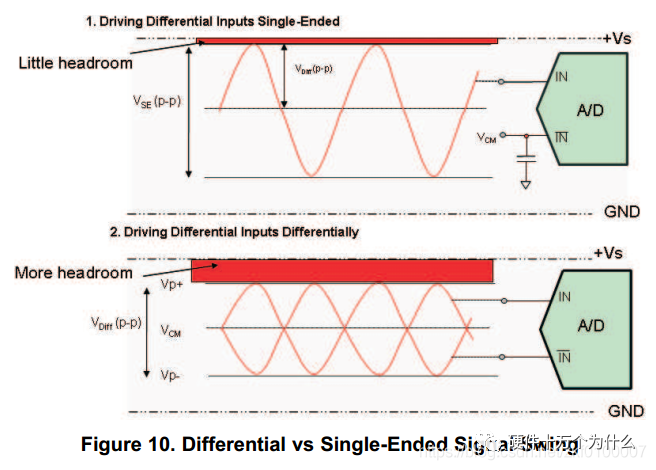

4.1模拟输入高速ADC通常采用差分输入,输入信号是180度反相的,使得信号是叠加的。与单端输入相比,由于消除了共模噪声,差分信号改善了ADC的噪声特性。此外,差分信号还降低了偶次谐波,这是由于信号被偏移了180度,对于偶次谐波,导致2x180,4X180,6X180度的相移,如下图所示

与单端信号相比,差分信号的幅度仅于等效单端信号的一半,从而差分信号具有更优的谐波性能。小信号使得ADC具有更宽的裕量。一般而言,更多的裕量可以使ADC工作在线性区域,减少产生谐波的非线性影响。如下图所示:

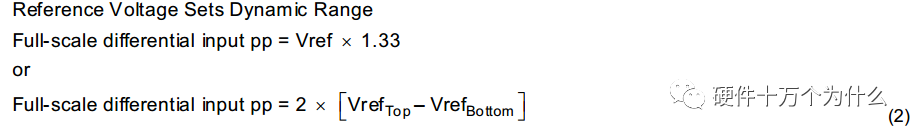

参考电压可以由ADC内部生成,或者外部提供。为了获得数据手册标注的性能,需要提供正确的参考电压。对于外部参考,应尽量降低外部参考电压的直流噪声。参考电压上的噪声会直接影响ADC的SNR。

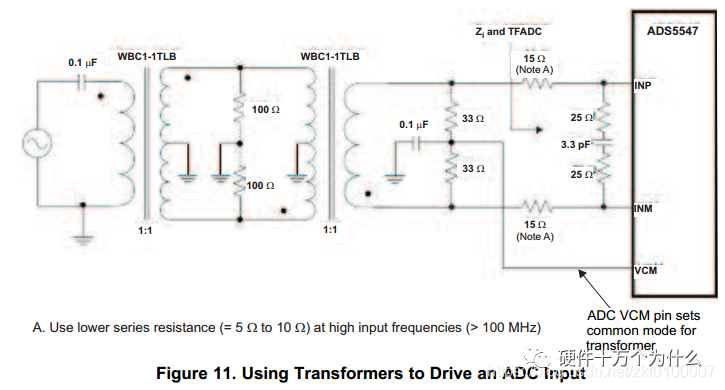

图11中,共模电压VCM是指输入到差分模拟输入信号的直流电平。VCM用于将将差分输入信号偏置在电源和GND的中间。

VCM有以下几种应用方式:

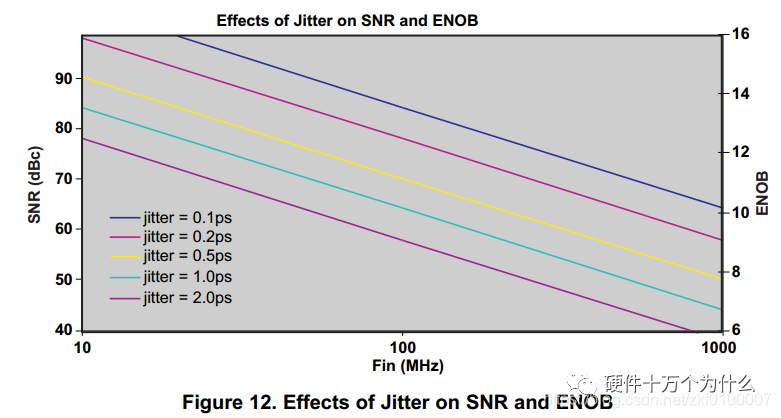

高速ADC通常采用差分时钟输入。时钟抖动及斜率是影响ADC的SNR的重要因素。时钟抖动对SNR的影响如下所示:

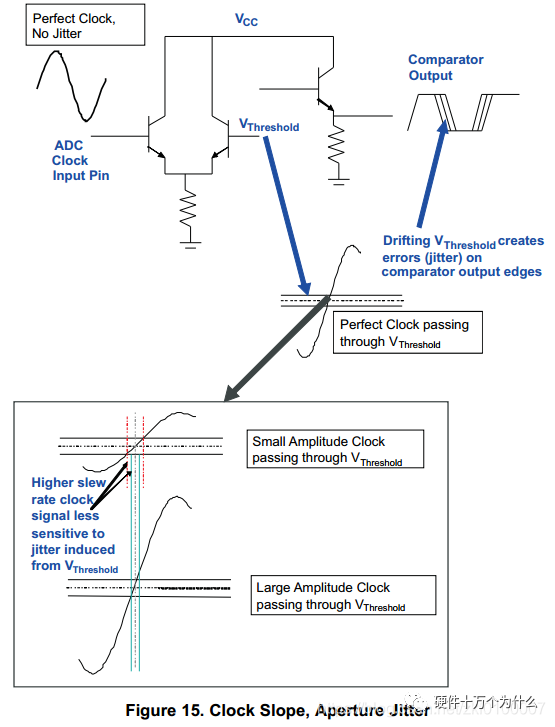

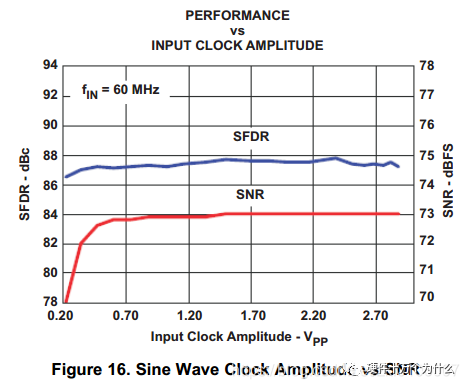

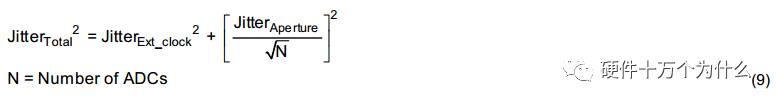

由上可知,对于理想ADC,时钟频率并不会影响SNR。若不考虑时钟抖动,时钟频率达到ADC设计极限(诸如建立、保持或模拟建立时间),从而最终导致SNR下降。抖动不变时,SNR随输入信号频率增加而降低。由上图所示,指定时钟抖动时,SNR随信号频率增加而降低。高频模拟输入信号对于时钟抖动有较大的误差。如果时钟信号上有随机噪声,会表现在频谱图上。如果时钟信号上有确定的误差信号,这个信号会与ADC的输入信号混合在一起,在频谱图上表现为杂散。设计师必须考虑时钟抖动的两个重要因素。其一是ADC的孔径延迟,其二是外部输入时钟的抖动。这两个因素共同产生的抖动影响ADC的采样误差。设计实例:设计需求如下:SNR=75dBFIN=75MHz客户选定的ADC其孔径抖动=80fs为了满足客户的SNR需求,客户应用所能容忍的最大抖动是多少?A:用公式3求解抖动B:用公式4求解外部时钟抖动因此,外部输入时钟抖动必须小于397fs。下图展示了慢时钟沿导致较大的孔径抖动的情形。对于正弦时钟,增大时钟幅度可以改善孔径抖动进而提高ADC的SNR。

那么问题来了,如果关注时钟上升斜坡,那为什么不直接给ADC提供方波时钟信号?答案是:方波时钟确实是一个可行的ADC时钟选择。但是,设计者必须在正弦和方波之间做出一系列的折衷。

其一是低抖动方波时钟与时钟频率范围间的折衷。对于大多数应用,通过窄带SAW或晶体滤波器以改进ADC时钟的close-in相位噪声(抖动)。滤波后,时钟变成低抖动正弦时钟,可以直接提供给ADC。这种方法的局限在于时钟频率范围受限于滤波器带宽。一些公司有时钟抖动清除及时钟分配芯片,这些芯片具有较好的相噪性能、方波输出和较宽的频率范围,其相噪特性足以满足系统需求,而不需要额外滤波器。

其二是方波时钟与正弦时钟在信号完整性方面的折衷。与正弦信号相比,方波信号具有丰富的谐波,具有高频分量。由于信号反射及对其它信号的干扰,高频分量会对电路设计带来较大困难。不管采用哪种时钟信号,必须对电路设计着重考虑,以满足ADC的抖动需求。

ADC的实验评估主要包括软件和硬件两个方面。

ADC实验评估的软件手段主要是FFT。由于其高速及准确性,FFT是时域到频域变换的卓越评估工具。

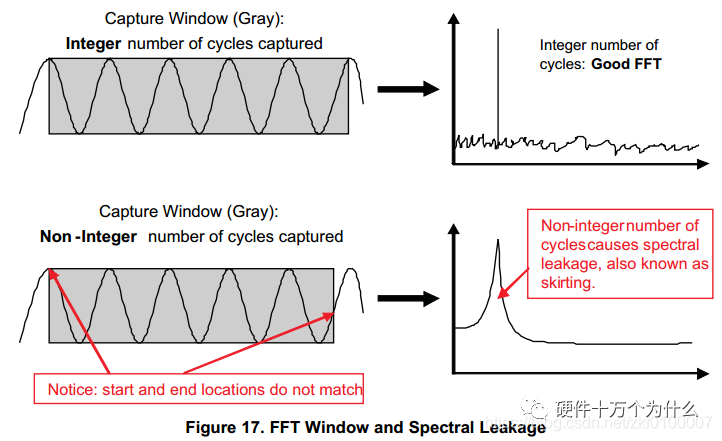

要实现FFT,必须理解一致性、加窗和频谱泄漏等概念。

下图显示了加窗和频谱泄漏。窗口选择不当会导致频谱泄漏。

某些设计者需要非整数个周期。在这些特殊情况下,由于频谱泄漏,不能使用FFT,可以使用布莱克曼窗或者傅利叶分析。这种方法允许采集非整数个周期信号,但是需要更多计算时间并且会对噪底计算和频率响应引入少量误差。

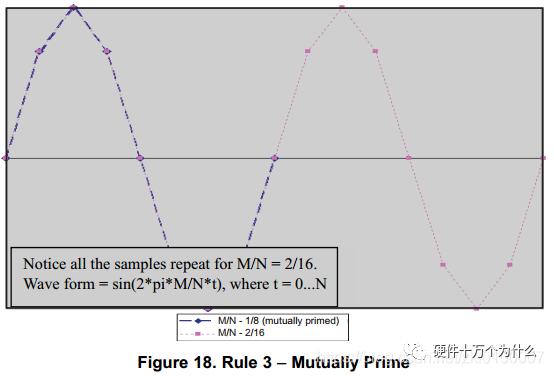

FFT一致性定义如下:

规则4:FIN与FS的分辨率须大于输入源的最小分辨率要求。例如,模拟输入和时钟源的最小分辨率为10Hz,则它们不能被设置为小于10Hz的分辨率。在做FFT时,如果频率分辨率小于输入源的分辨率,会采集到非整数个周期,进而引起频谱泄漏。

设计实例:

需求如下:

Fin=70MHz

Fs=125Msps

分辨率为1Hz

求解M,N,Fin,Fs。

1)取N=8192,M=NFin/Fs=4587.52,取M=4587.

2)根据N重新计算Fs(保证分辨率为1Hz)

X=Fs/N=125M/8192=15258.789

X取整为Xnew=15258.

新的Fs=XnewN=152588192=124.993536Msps

3)计算新的Fin

Fin=FsM/N=124.993536Msps*4587/8192=69.9988446MHz

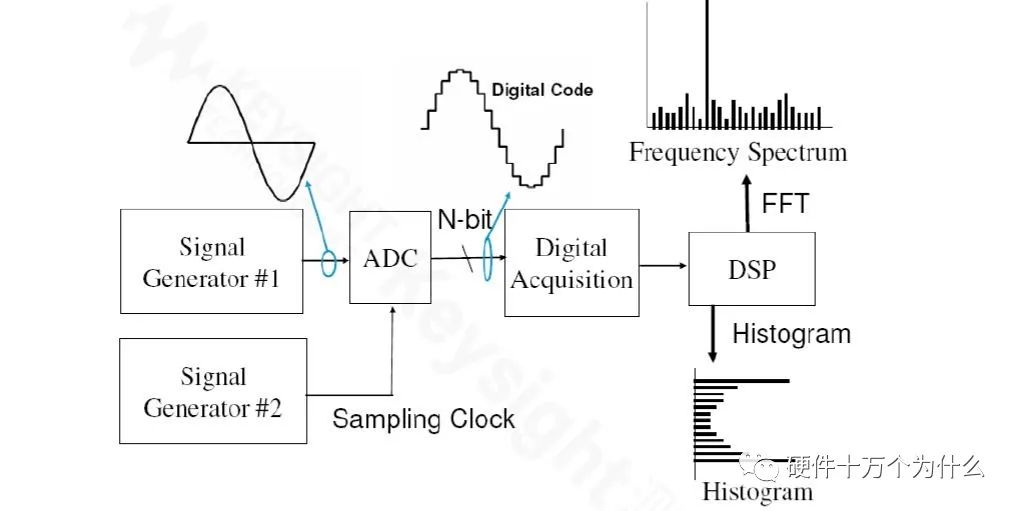

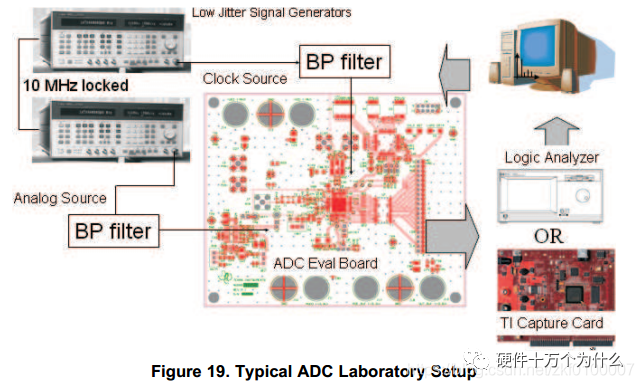

典型的ADC实验设置如下图所示:

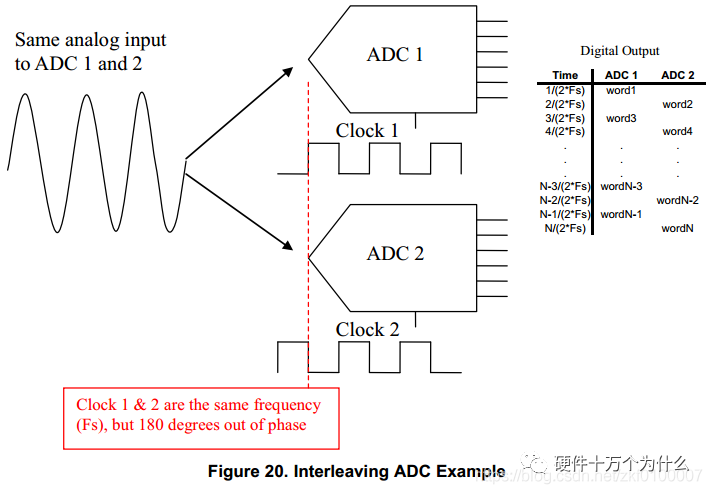

5.交织采样

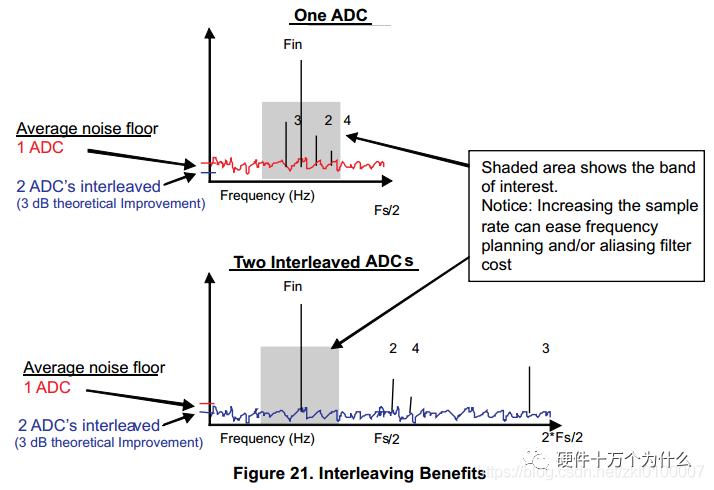

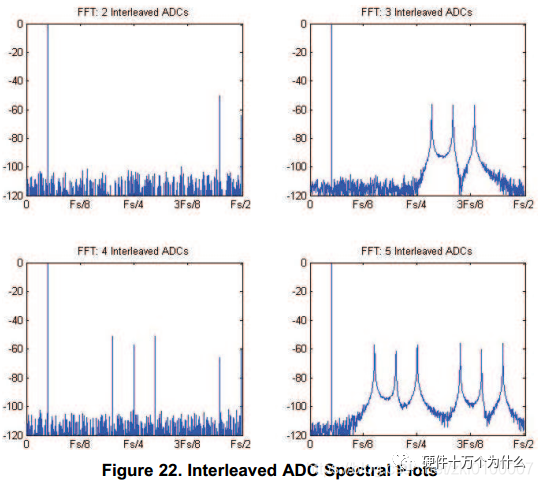

两个ADC的模拟输入并联连接,采样时钟相差180度,从而实现采样速度翻倍。采样速度翻倍有两个好处,其一是提高的采样信号带宽,其二是交织采样将噪底在更宽的带宽上进行扩展,可将噪底降低3dB,如下图所示:

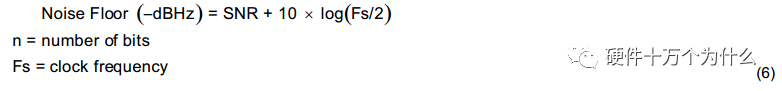

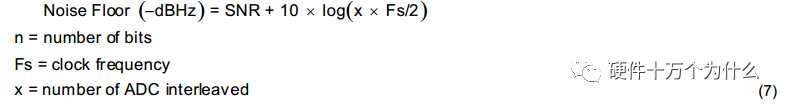

单片ADC噪底计算公式如下:

当多片ADC交织时,噪底计算公式如下:

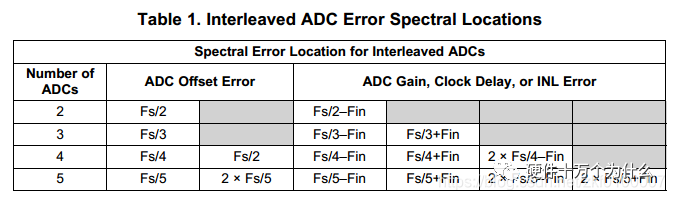

两片或多片ADC交织也带来了另外的设计挑战。ADC之间的DC偏移的差异会在特定位置产生频谱分量。ADC之间的增益差异、INL差异和时钟相位误差会在时钟和模拟输入混频的位置产生频谱分量。

由上图可知,尽管ADC的误差较小,但仍会造成较大的杂散响应。设计者需要设计相应的经温度补偿校正的模拟或数字滤波器,滤除这些杂散。

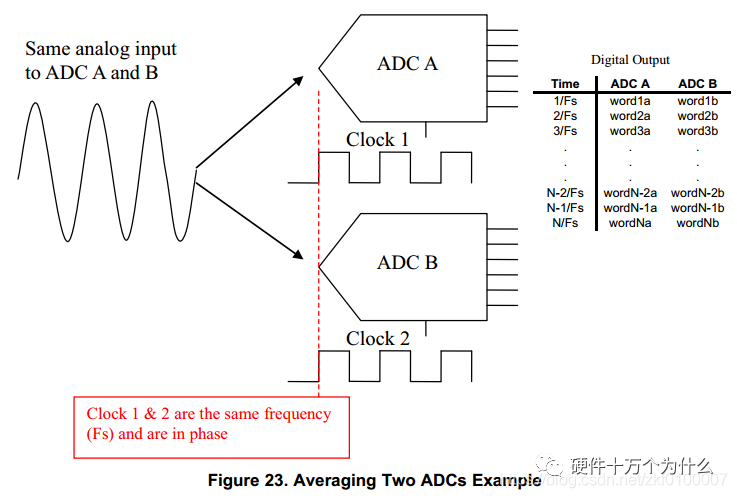

6.ADC取平均

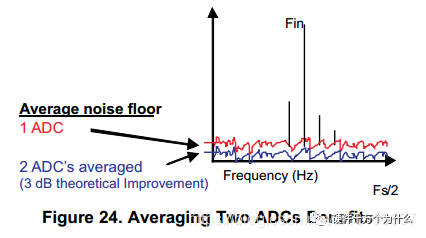

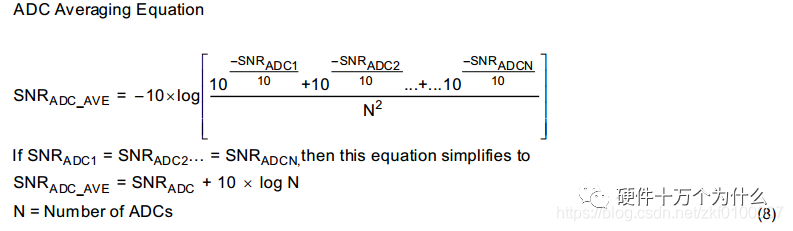

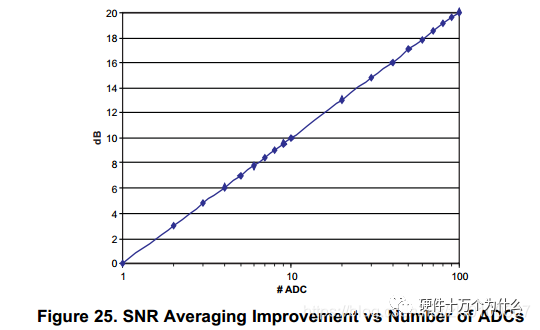

提高单片ADC SNR性能的另一方法是对两片或多片ADC取平均。对两片ADC取平均,可以将SNR提高3dB。

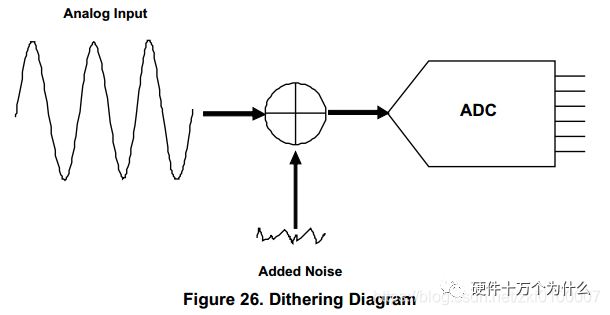

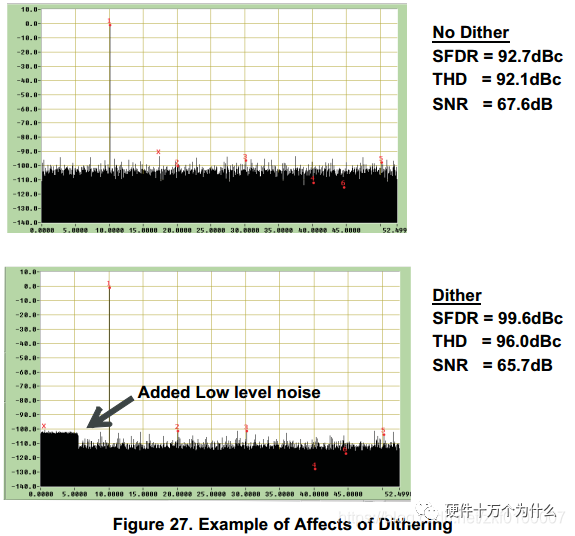

7.抖动(Dithering)

ADC具有确定性和系统性的错误,且具有重复性。理论上, 可以通过添加一个低量级的随机噪声来最大限度地减少这些错误。添加低量级随机噪声,以改善 ADC 失真的过程称为抖动(Dithering)。

7月16日-17日将在上海举办一期高级数模转换器(ADC)课程,本次课程首先深入探讨大规模时间交织 ADC 的交织器拓扑结构,探讨非理想情况、设计注意事项、建模技术和详细案例研究。随后,特别关注对高性能大规模 TI ADC 至关重要的外设块的设计挑战和解决方案,包括输入缓冲器和参考缓冲器。此外,还研究了极限采样器、残差放大器和时钟等关键 SAR ADC 块,通过全面的案例研究介绍了基本概念和先进技术。

今天小编带来了:ISSCC2024套餐,里面有文章、Short Course、PPT、Tutorial等,同学可以拿回去自己学习研究。

ISSCC2024完整资料领取方式如下

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台