在本系列第三篇文章中,我们介绍了传统封装和晶圆级(Wafer-Level)封装,本篇文章将继续介绍将多个封装和组件整合到单个产品中的封装技术。其中,我们将重点介绍封装堆叠技术和系统级封装(SiP)技术,这两项技术都有助减小封装体积,提高封装工艺效率。

01

堆叠封装 (Stacked Packages)

想象一下,在一个由多栋低层楼房组成的住宅综合体内,若要容纳数千名居民,则需要占据非常大的面积才能满足需求。然而,一栋摩天大楼就能容纳同样数量的居民。这个例子清楚地说明了堆叠封装具备的一大优势。相对于将多个封装水平分布在较大面积的产品,由堆叠封装(Stacked Package)组成的产品可以在减小体积的同时进一步提高性能。除了作为一种重要封装技术,堆叠封装还是产品开发过程中采用的一种基本方法。

过去,产品往往在一个封装体内只封装一个芯片,但现在可以开发涵盖多种不同功能的多芯片封装或将多个存储器芯片集成到容量更大的单个封装中。此外,系统级封装可将多个系统组件整合在单个封装体内。这些技术的问世使半导体公司能够在打造高附加值产品的同时,满足多样化的市场需求。

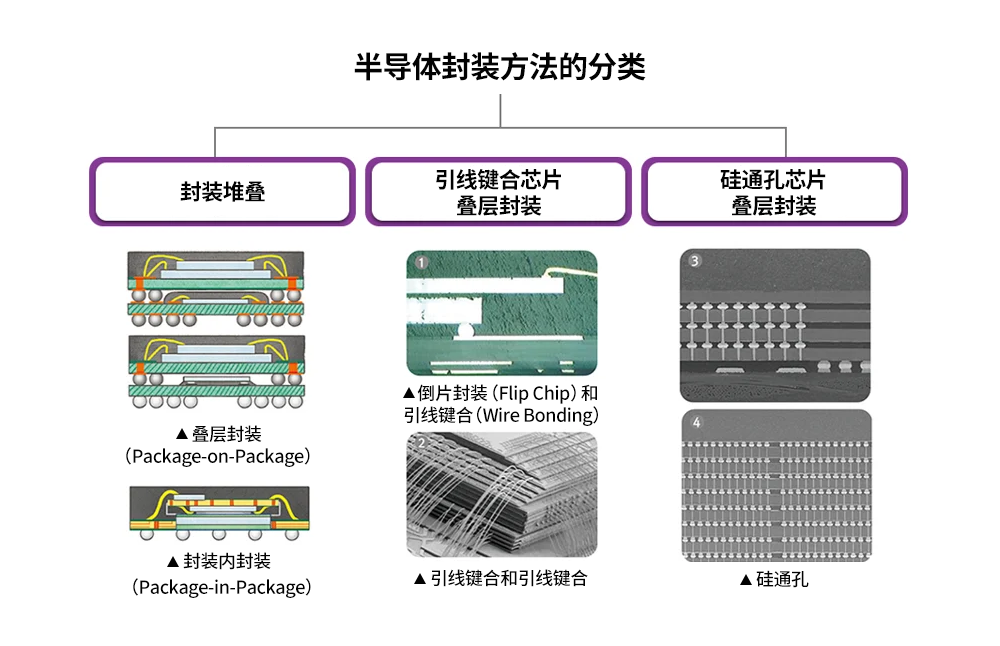

▲图1:堆叠封装方法的分类(ⓒ HANOL出版社)

如图1所示,基于不同的开发技术,堆叠封装可分为三大类:1)通过垂直堆叠封装体而形成的封装堆叠;2)使用引线键合技术将不同芯片堆叠在单个封装体内的芯片叠层封装;及3)使用硅通孔(TSV)1技术替代传统引线键合技术实现内部电气互连的芯片叠层封装技术。每种堆叠封装技术都具有不同的特点、优势和局限性,这将决定它们在未来的应用。

1 硅通孔(TSV,Through Silicon Via):一种可完全穿过硅裸片或晶圆实现硅片堆叠的垂直互连通道。

封装堆叠

(Package Stacks))

封装堆叠通过垂直堆叠封装体来实现。因此,其优缺点与芯片叠层封装正好相反。封装堆叠方法将完成测试的封装体相堆叠,在某个封装体测试不合格时,可轻松地将其替换为功能正常的封装体。因而,其测试良率相比芯片叠层封装更高。然而,封装堆叠尺寸较大且信号路径较长,这导致其电气特性可能要劣于芯片叠层封装。

最常见的一种封装堆叠技术便是叠层封装(PoP),它被广泛应用于移动设备中。对于针对移动设备的叠层封装,用于上下层封装的芯片类型和功能可能不同,同时可能来自不同芯片制造商。

通常,上层封装体主要包括由半导体存储器公司生产的存储器芯片,而下层封装体则包含带有移动处理器的芯片,这些芯片由无晶圆厂的设计公司设计,并由晶圆代工厂及外包半导体组装和测试(OSAT)设施生产。由于封装体由不同厂家生产,因此在堆叠前需进行质量检测。即使在堆叠后出现缺陷,只需将有缺陷的封装体替换成新的封装体即可。因此封装堆叠在商业层面具有更大益处。

芯片堆叠(Chip Stacks)-

引线键合芯片叠层封装

(Chip Stacks With Wire Bonding)

将多个芯片封装在同一个封装体内时,既可以将芯片垂直堆叠,也可以将芯片水平连接至电路板。考虑到水平布局可能导致封装尺寸过大,因而垂直堆叠成为了首选方法。相比封装堆叠,芯片堆叠封装尺寸更小,且电信号传输路径相对更短,因而电气特性更优。然而,若在测试中发现某个芯片存在缺陷,则整个封装体就会报废。鉴于此,芯片堆叠封装的测试良率较低。

在芯片堆叠封装中,要想提高存储器容量,就需要在单一封装中堆叠更多的芯片。因而,可将多个芯片集成在同一封装体内的技术应运而生。但与此同时,人们不希望封装厚度随着堆叠芯片数量的增加而变厚,因此致力于开发能够限制封装厚度的技术。要做到这一点,就需要减少芯片和基板(Substrate)等可能影响封装厚度的所有组件的厚度,同时缩小最上层芯片和封装上表面之间的间隙。这给封装工艺带来了诸多挑战,因为芯片越薄越易于损坏。因此,目前的封装工艺正致力于克服这些挑战。

硅通孔(TSV)-

硅通孔芯片叠层封装

(Chip Stacks With TSV)

硅通孔是一种通过在硅片上钻孔来容纳电极的芯片堆叠技术。相比采用传统引线方法实现芯片与芯片(Chip-to-Chip)互连或芯片与基板(Chip-to-Substrate)互连,硅通孔通过在芯片上钻孔并填充金属等导电材料来实现芯片垂直互连。尽管使用硅通孔进行堆叠时使用了芯片级工艺,但却采用晶圆级工艺在芯片正面和背面形成硅通孔和焊接凸点(Solder Bump)。由此,硅通孔被归类为晶圆级封装技术。

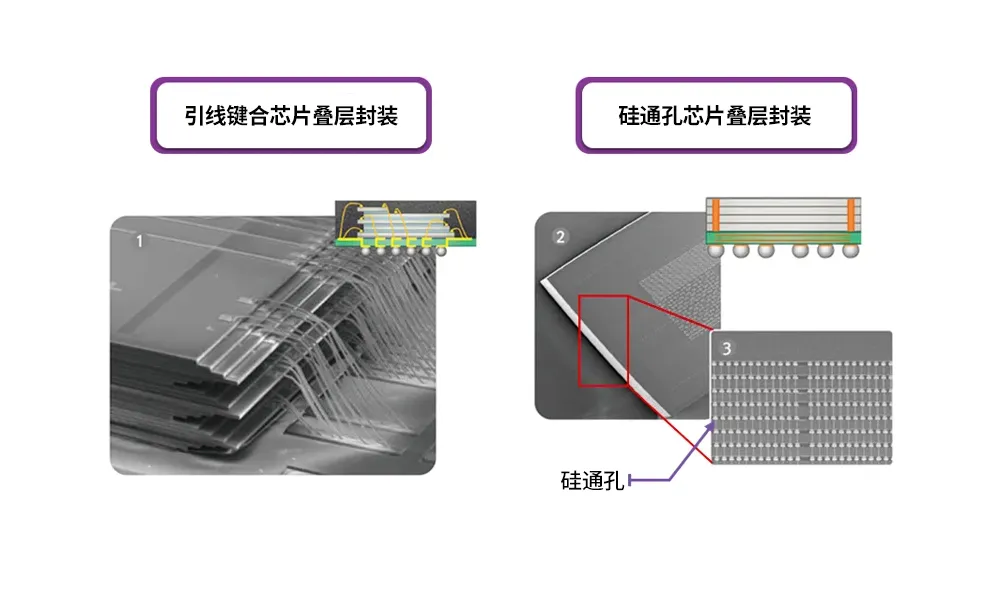

▲图2:使用硅通孔技术的芯片剖面图(ⓒ HANOL出版社)

硅通孔封装的主要优势在于性能优越且封装尺寸较小。如图2所示,使用引线键合的芯片堆叠封装利用引线连接至各个堆叠芯片的侧面。由于堆叠芯片以及连接引脚(Pin)的数量增加,引线变得更加复杂,而且也需要更多空间来容纳这些引线。相比之下,硅通孔芯片堆叠则不需要复杂的布线,因而封装尺寸更小。

正如上一篇文章所介绍,倒片封装(Flip Chip)具有良好的电气特性,原因有以下几点:其更易在理想位置形成输入/输出(I/O)引脚;引脚数量增加;电信号传输路径较短。基于同样的原因,硅通孔封装也具有良好的电气特性。当从一个芯片向其下方的芯片发送电信号时,硅通孔封装使得信号能够直接向下传输。相反,如果使用引线键合封装,则信号会先向下传输至基板,随后再向上传输至芯片,因而信号传输路径要长得多。如图2所示的引线芯片堆叠,芯片中心无法进行引线连接。相反,硅通孔封装可在芯片中心钻孔,形成电极,并与其他芯片连接。与引线连接不同,硅通孔封装可大幅增加引脚数量。

高宽带存储器(HBM)采用一种全新的DRAM架构,这种架构借助硅通孔技术来增加引脚数量。通常,在DRAM规范中,“X4”表示有四个引脚用于发送信息,或可以同时从DRAM发送4位(bit)信息。相应地,X8表示8位,X16表示16位,以此类推。增加引脚数量有利于同时发送更多信息。然而,由于自身局限性,引线芯片堆叠最多只能达到X32,而硅通孔堆叠则没有这方面的局限性,使HBM可达到x1024。

目前,将硅通孔封装用于DRAM的量产存储器产品,包括HBM和3D堆叠存储器(3DS)。前者用于图形、网络和高性能计算(HPC)应用,而后者则主要用作DRAM存储器模块。

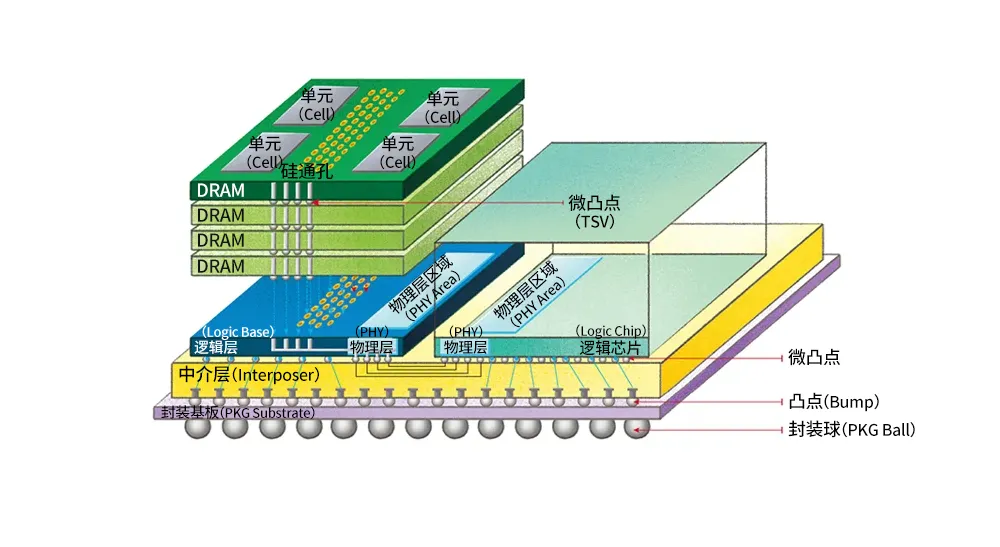

▲图3:使用HBM的2.5D封装(ⓒ HANOL出版社)

HBM并非一种全封装产品,而是一种半封装产品。当HBM产品被送到系统半导体制造商那里时,系统半导体制造商会使用中介层2构建一个2.5D封装3,将HBM与逻辑芯片并排排列,如图3所示。由于2.5D封装中的基板无法提供用于支持HBM和逻辑芯片的所有输入/输出引脚的焊盘(Pads),因此需要使用中介层来形成焊盘和金属布线,从而容纳HBM和逻辑芯片。然后,再将这些中介层与基板连接。这些2.5D封装被认为是一种系统级封装。

同样采用硅通孔封装的产品还有3DS DRAM,这是一种在PCB板上安装球栅阵列封装(BGA)4的内存模块。尽管服务器中的DRAM存储器模块需要高速传输和大容量存储,但使用引线键合的芯片堆叠封装因其速度局限性而无法满足这些要求。鉴于此,服务器等高端系统往往使用由硅通孔芯片堆叠封装构成的模块。

2 中介层(Interposer):用于2.5D配置中的裸片之间又宽又快的电信号管道。

3 2.5D封装(2.5D package):2.5D和3D封装在每个封装中包含多个集成电路。在2.5D结构中,两个或多个有源半导体芯片(Active Semiconductor Chips)并排排列在硅中介层上。在3D结构中,有源芯片通过裸片垂直堆叠的方式集成在一起。

4 球栅阵列封装(BGA):一种表面贴装芯片封装,使用锡球作为其连接器。

02

系统级封装(SiP)

由HBM和逻辑芯片构成的封装属于系统级封装。顾名思义,系统级封装是指在单个封装体中集成一个系统。然而,完整的系统还需包括传感器、模拟数字(A/D)转换器、逻辑芯片、存储芯片、电池和天线等组件,但就目前的技术发展水平而言,还无法将所有这些系统组件集成到单个封装体内。因此,研究人员正致力于不断开发针对这一领域的封装技术,而当前的系统级封装是指在单个封装体内集成部分系统组件。例如,使用HBM的封装将HBM和逻辑芯片集成到单个封装体内,形成一个系统级封装。

不同于系统级封装,系统级芯片(SoC)在芯片级实现系统功能。换言之,在同一个芯片上实现多个系统功能。例如,目前大多数处理器都在芯片内集成了静态RAM(SRAM)存储器,可同时在单个芯片上实现处理器的逻辑功能和SRAM的存储功能。因此,这些处理器被归类为系统级芯片。

系统级芯片需要将多种功能组合到单个芯片中,因此开发流程复杂而漫长。此外,如要对已开发出来的系统级芯片中单个元件的功能进行升级,则需从头开始对它们进行设计和开发。而系统级封装开发起来则更容易也更快,这是由于系统级封装是通过将已开发的多个芯片和器件整合在单个封装体内来实现。由于芯片本身是单独开发和制造,即使器件的结构完全不同,也很容易将它们集成到单个封装体内。同时,如果只需对功能的一个方面进行升级,则无需从头开发封装就可在芯片内集成新开发的器件。然而,如果产品将被长期大量使用,则相比系统级封装而言,将其开发为系统级芯片将更高效,因为系统级封装需要制造的材料更多,这会增加封装体积,只有这样才能将多个芯片整合到单个封装体内。

尽管系统级芯片和系统级封装之间存在各种差异,但两者并不是非此即彼的关系。事实上,可以将两者结合起来,以产生协同效应。完成系统级芯片开发后,可将其与其他功能芯片封装到单个封装体内,然后作为增强型系统级封装来实现。

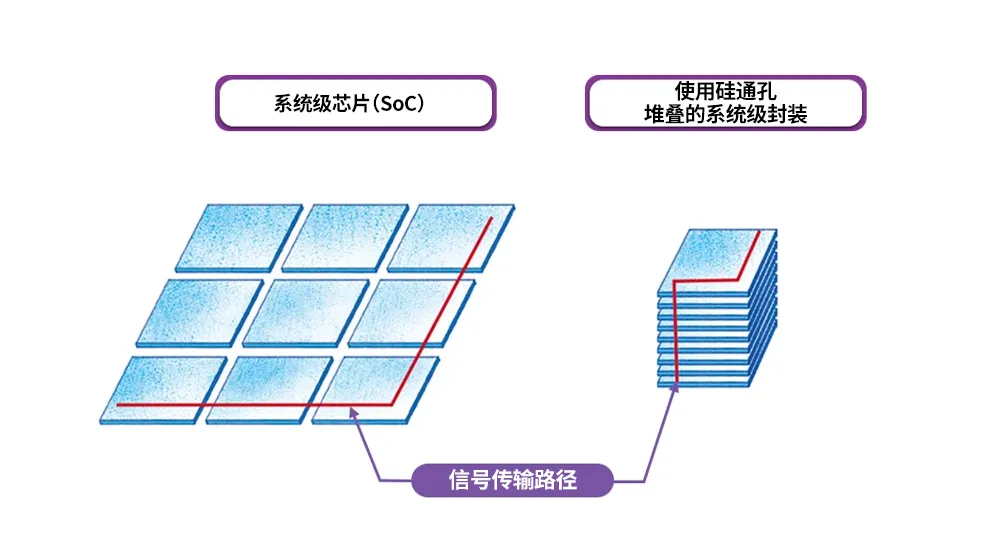

▲图4:使用硅通孔堆叠的系统级芯片和系统级封装的信号传输路径长度比较(ⓒ HANOL出版社)

在对系统级封装和系统级芯片的性能进行比较时,人们原本以为系统级芯片在单个芯片上实现,因而其电气特性会更优异。然而,随着芯片堆叠技术(如硅通孔技术)的发展,系统级封装的电气特性与系统级芯片旗鼓相当。图4对使用硅通孔堆叠的系统级芯片和系统级封装的信号传输路径进行了比较。当信号从系统级芯片的一端传输到对角的另一端时,将系统级芯片分为9个部分并使用硅通孔技术进行堆叠时,传输路径会短得多。

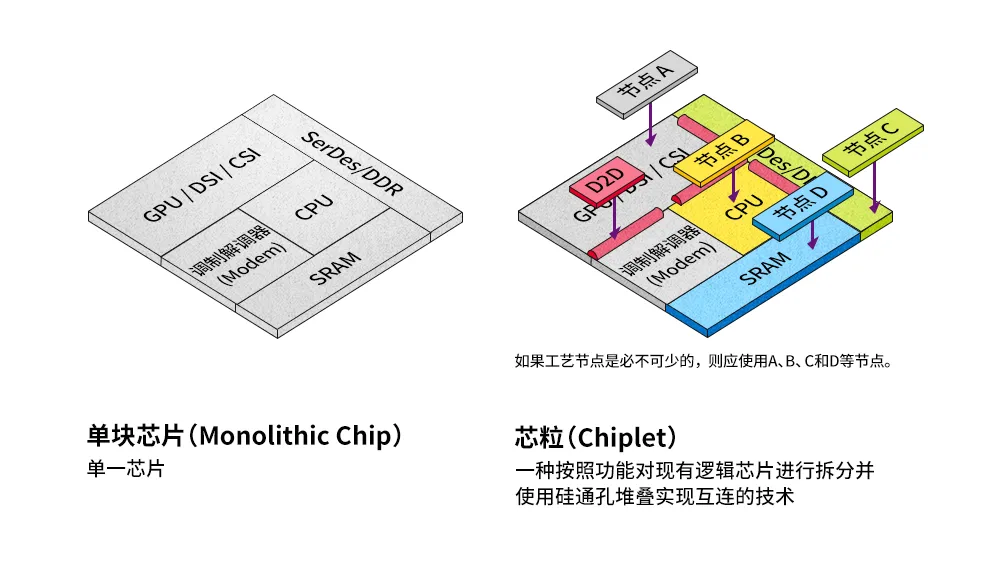

▲图5:芯粒概念图

除了使用硅通孔堆叠的系统级封装因具备各种优势而成为焦点之外,近年来一种称为芯粒(Chiplets)的技术也受到了广泛关注。如图5所示,这种技术按照功能对现有逻辑芯片进行拆分,并通过硅通孔技术对它们进行连接。与单块芯片相比,芯粒拥有三大优势。

首先,芯粒的良率较单块芯片有所提高。当晶圆(Wafer)上芯片的尺寸较大时,则晶圆良率就会受到限制,而缩小芯片尺寸可提高晶圆良率,从而降低制造成本。例如,将一个直径为300毫米的晶圆切割为100或1000个芯片(裸片)。如果在晶圆加工过程中,由于晶圆正面平均分布着五种杂质而导致五个芯片出现缺陷,则切割为100个芯片的产品良率为95%,而切割为1000个芯片的产品良率则为99.5%。因此,包含裸片数量越多或芯片尺寸越小的产品,其良率越高。鉴于此,按照功能对芯片进行拆分,并将其作为系统级封装而非系统级芯片中的单个芯片,有助于提高成本效益。

第二个优势是开发流程得到简化。对于单个芯片而言,如需升级芯片功能或采用最新技术,则需重新开发整个芯片。然而,如果对芯片进行分割,则只需对具有相关功能的芯片进行升级或使用最新技术对其进行开发即可,因而可缩短开发周期,提高工艺效率。例如,可以针对一些分割芯片采用现有的20纳米(nm)技术,同时针对其他芯片采用最新的10纳米以下技术,以此提高开发效率。

第三个优势是可促进技术开发集中化。由于芯片按照功能进行划分,因而无需针对每个功能来开发相应的芯片。只需开发用于核心技术的芯片,而其他芯片则可以通过购买或外包获取,这样企业就可以专注于开发自己的核心技术。

鉴于这些优点,主要半导体厂商正在引入基于芯粒技术的半导体产品或将其纳入自身的发展路线图。

在上一篇文章中,我们介绍了各种传统封装和晶圆级封装技术,而本篇文章则对更多封装技术及其不同特点进行了综述。目前,堆叠封装和系统级封装技术已取得长足发展,半导体研究人员将继续致力于提高这些高质量技术的能力,在提高其功能的同时,尽量缩小其占用的空间。通过生产兼具尺寸、功能和性能优势的封装产品,封装工艺的效率有望得到进一步提升。

推荐阅读

MTK、高通、紫光展锐手机SOC平台型号对比汇总(含详细参数,更新至2023年2月份)

2013-2023年全球智能手机出货量排名,明年智能手机市场将全面反弹

一文看懂NAND、eMMC、UFS、eMCP、uMCP、DDR、LPDDR及存储器和内存区别

SK hynix海力士DDR、LPDDR、UFS、eMMC、eMCP、uMCP规格型号参数对照表

什么是集成电路、工艺、CPU、GPU、NPU、ISP、DSP ?存储器和内存的区别是什么

科普;设计一颗芯片有多难,芯片是如何制造的,一片晶圆能切割多少片芯片?

三星内存eMCP、UMCP、eMMC、LPDDR、DDR型号参数对照表

WiFi发展史丨什么是WiFi6、WiFi6E和WiFi7以及参数对比

消费级、工业级、汽车级、军工级、航天级芯片区别对比

全球前五大存储厂商产品介绍Roadmap及代理商信息

KIOXIA 铠侠UFS、eMMC、NAND型号参数对照表

全球移动通信射频前端厂商汇总(含晶圆、封测)

手机平板常用存储型号容量对照表

全球80家无线通信模组企业汇总及介绍

三星、苹果手机处理器参数及代表机型

PCB板的价格是怎么算出来的(详解)

一文看懂智能手机常用传感器

MCU最强科普总结(收藏版)