作者:Pete Millett, Technical Marketing Engineer, Monolithic Power Systems,翻译:Toffee Jia,来源:MPS

电机驱动 IC 传递大量电流的同时也耗散了大量电能。通常,能量会耗散到印刷电路板(PCB)的铺铜区域。为保证PCB充分冷却,需要依靠特殊的PCB设计技术。在本文的上篇中,将为您提供一些电机驱动IC 的PCB 设计一般性建议。

使用大面积铺铜!

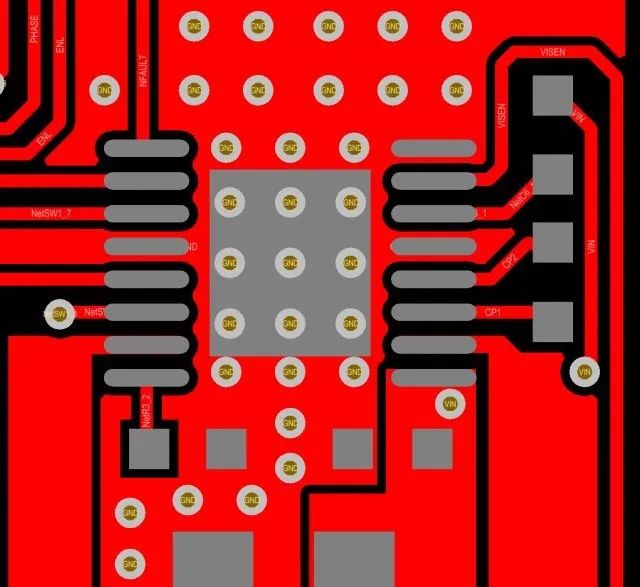

图 1:加宽PCB走线

由于较窄走线所产生的热量会传导至较宽的铺铜区域,所以窄走线的温升可以忽略不计。

嵌在PCB内层板中的走线散热效果不如外层走线,因为绝缘体的导热效果不佳。正因为如此,内层走线的宽度应为外层走线的两倍。

表1 大致给出了电机驱动应用中长走线(大于2cm)的推荐宽度。

电流 (RMS 或 DC) | 走线宽度为1盎司铺铜 | 走线宽度为2盎司铺铜 | ||

外层板 | 内层板 | 外层板 | 内层板 | |

≤1A | 0.6mm | 1.2mm | 0.3mm | 0.6mm |

2.5A | 1mm | 2mm | 0.5mm | 1mm |

5A | 2.5mm | 5mm | 1.2mm | 2.5mm |

10A | 7mm | 14mm | 3.5mm | 7mm |

表 1: PCB走线宽度

如果空间允许,越宽的走线或灌铜可以最大限度地降低温升并能减小电压落差。

热过孔-越多越好!

过孔是一种小的镀孔,通常用于将信号走线从一层传递到另一层。 顾名思义,热过孔是将热量从一层传递到另一层。适当地使用热过孔可以有效帮助PCB散热,但也需要考虑实际生产中的诸多问题。

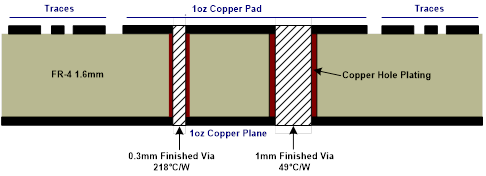

过孔具有热阻,这就意味着每当热量流经时,过孔两端会有一定温差,其测量单位为摄氏度/每瓦特。所以,为最大限度地降低热阻,提高过孔的散热效率,过孔应设计大一点,且孔内的覆铜面积越大越好(见图2)。

图 2:过孔横截面

虽然可以在PCB的开放区域使用大的过孔,但是,过孔常常被放在散热焊盘的内部,因为这样可以直接从IC封装散热。在这种情况下,不可能使用大过孔,因为电镀孔过大会导致“渗锡”,其中用于连接IC至PCB的焊料会往下流入通孔,导致焊点不良。

有几种方法可以减少“渗锡”。一种是使用非常小的过孔,以减少渗入孔内的焊料。然而,过孔越小热阻越高,因此想要达到相同的散热性能,需要更多的小过孔才行。

另一种技术是“覆盖”电路板背面的过孔。这需要去除背板上阻焊层的开口,使得阻焊材料覆盖过孔。阻焊层会盖住小的过孔使焊锡无法渗入PCB。

但这又会带来另一问题:助焊剂滞留。如果使用阻焊层盖住过孔,那么助焊剂会滞留在过孔内部。有些助焊剂配方具有腐蚀性,长时间不去除的话会影响芯片的可靠性。所幸大多数现代免清洗助焊剂工艺都是无腐蚀性的,不会引起问题。

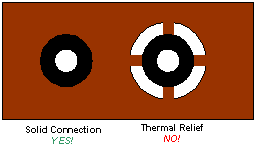

这里需注意,散热孔本身不具备散热功能,必须把它们直接连接至铺铜区域(见图3)。

图 3:热过孔

建议PCB设计师与PCB组装厂的SMT制程工程师协商出最佳的过孔尺寸和构造,尤其当过孔位于散热焊盘内部时。

焊接散热焊盘

TSSOP 和 QFN 封装中,芯片底部会焊有大片散热焊盘。这里的焊盘直接连到晶元的背面,为器件散热。必须将焊盘很好地焊接到PCB上才能耗散功率。

IC规格书不一定会指定焊盘焊膏的开口。通常,SMT制程工程师对放多少焊料,过孔模具使用什么样的形状都有自己的一套规则。

如果使用和焊盘大小一样的开口,则需要使用更多的焊料。当焊料熔化时,其张力会使器件表面鼓起。另外,还会引起焊料空洞(焊锡内部凹洞或间隙)。当焊料回流过程中助焊剂的挥发性物质蒸发或沸腾时,会发生焊料空洞。这会导致接合处的焊料析出。

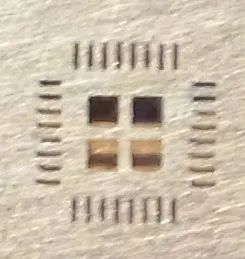

为了解决这些问题,对于面积大于约2mm2的焊盘,焊膏通常沉积在几个小的正方形或圆形区域中(见图4)。将焊料分布在多个较小的区域里可以使助焊剂的挥发性物质更容易挥发出来,以免造成焊料析出。

图 4:QFN 焊具

再次建议PCB设计师与SMT制程工程师共同协商出正确的散热焊盘模具开口。也可以参考网上的一些论文。

元件贴装

电机驱动IC的元件贴装指南与其他电源IC相同。旁路电容应尽可能靠近器件电源引脚放置,且旁边需放置大容量电容。许多电机驱动IC会使用自举电容或充电泵电容,这些也应放在IC附近。

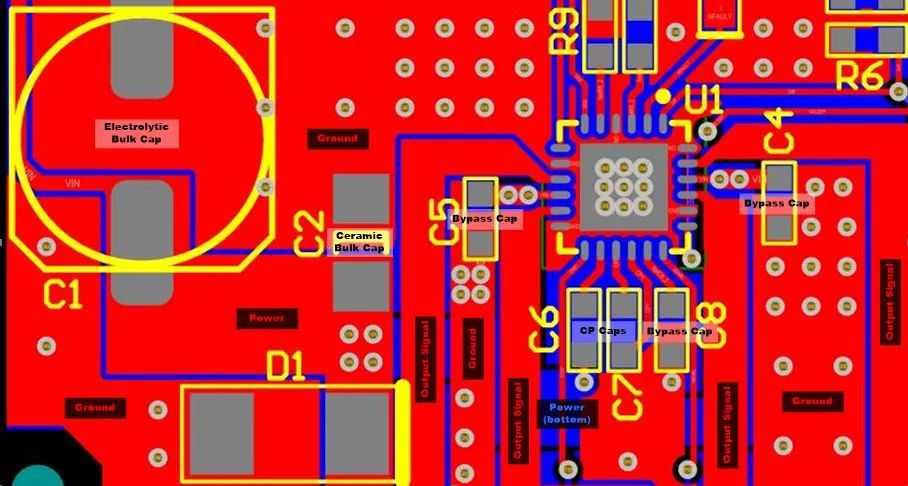

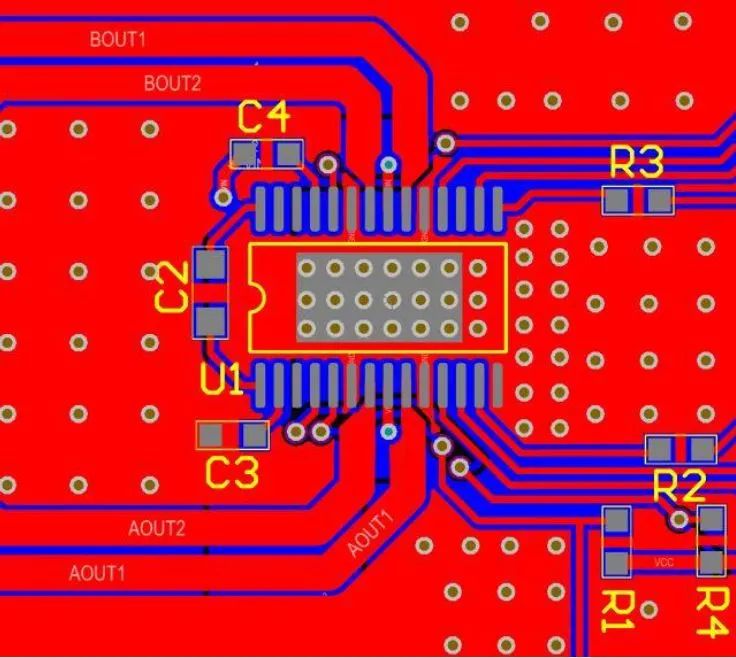

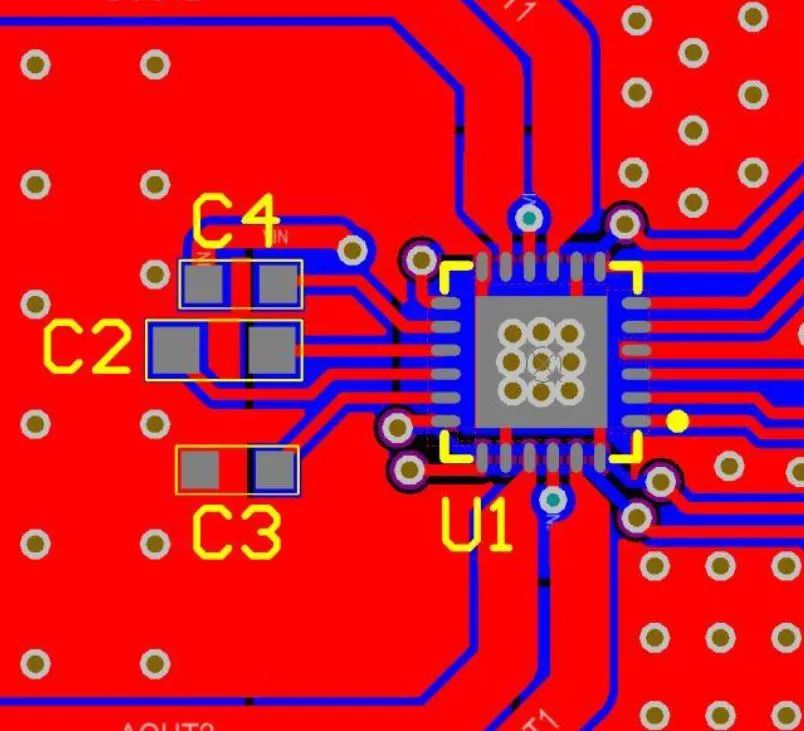

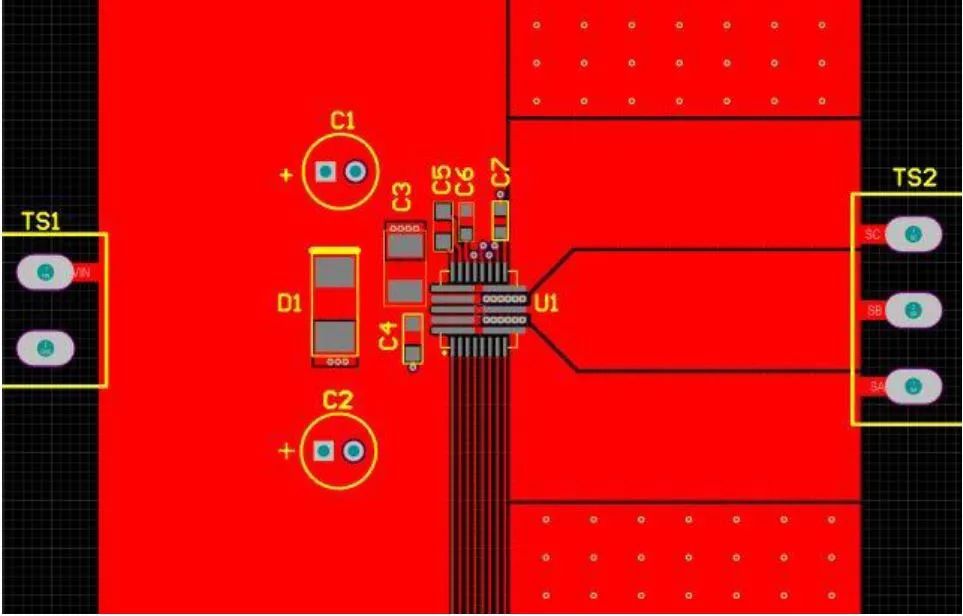

请参考图5中的元件贴装示例。图5显示了MP6600步进电机驱动的双层板PCB布局。大部分信号走线直接布置在顶层。电源走线从大容量电容绕到旁路,并在底层使用多个过孔,在更换层的位置使用多个过孔。

图5: MP6600 元件贴装

在本文的 下篇 中,我们将探讨详细的电机驱动IC封装方法和PCB布局。

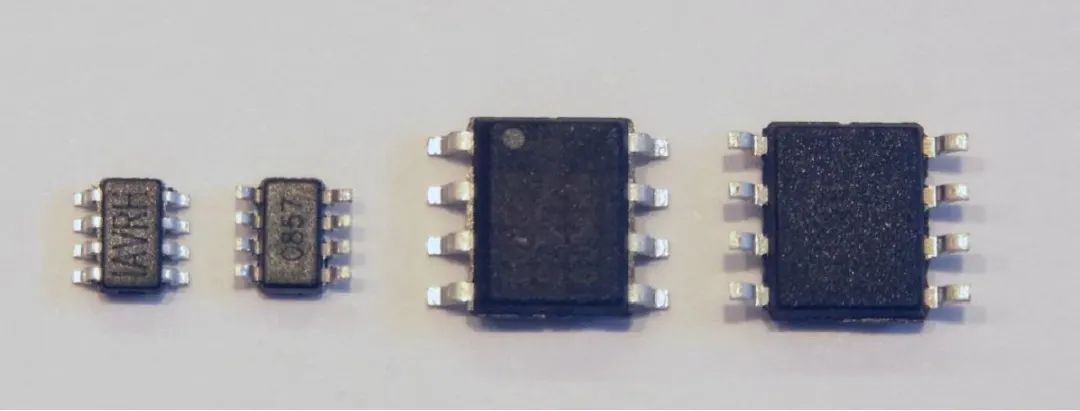

图 6: SOT 23 和 SOIC 封装

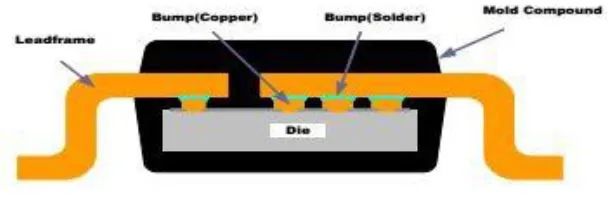

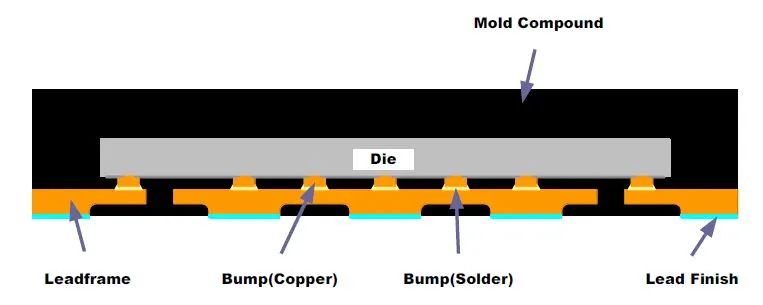

为了充分提高引线封装的功耗能力,MPS公司采用 “倒装芯片引线框架” 结构(图 7)。在不使用接合线的情况下,使用铜凸点和焊料将芯片粘接至金属引线,从而可通过引线将热量从芯片传导至 PCB。

图 7: 倒装芯片引线框架

通过将较大的铜区域连接至承载较大电流的引线,可优化热性能。在电机驱动器 IC 上,通常电源、接地和输出引脚均连接至铜区域。

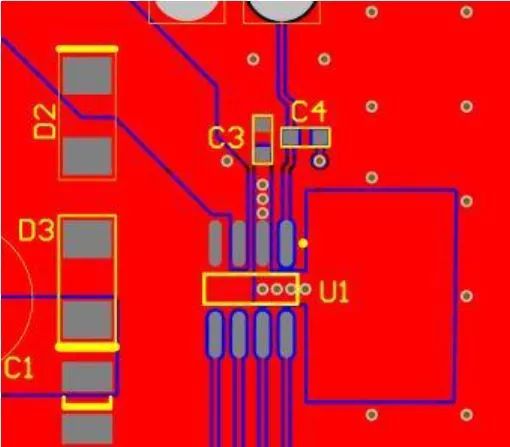

图 8: 倒装芯片 SOIC PCB 布局

图 8 所示为“倒装芯片引线框架”SOIC 封装的典型 PCB 布局。引脚 2 为器件电源引脚。请注意,铜区域置于顶层器件的附近,同时几个热通孔将该区域连接至 PCB 背面的铜层。引脚 4 为接地引脚,并连接至表层的接地覆铜区。引脚 3(器件输出)也被路由至较大的铜区域。

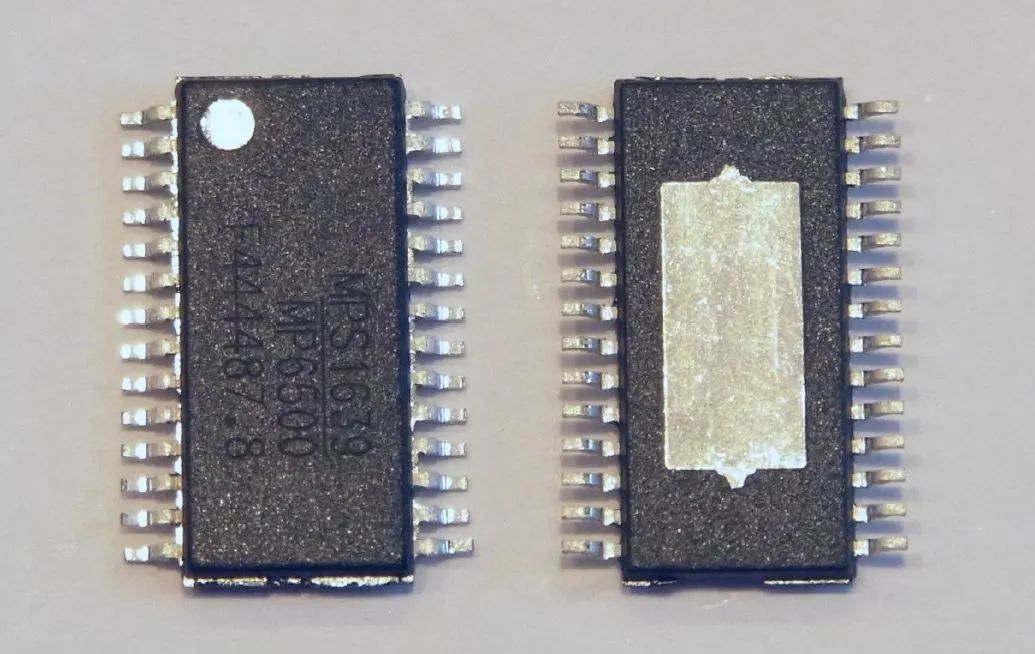

图 9: TSSOP 封装

QFN 封装为无引线封装,在器件外缘周围带有板,器件底部中央还带有一个更大的板(图 10)。这个更大的板用于吸收芯片中的热量。.

图 10: QFN 封装

为排除这些封装中的热量,外露板必须进行良好的焊接。外露板通常为接地电位,因此可以接入 PCB 接地层。在图 11 的 TSSOP 封装的示例中,采用了一个 18 通孔阵列,钻孔直径为 0.38 mm。该通孔阵列的计算热阻约为 7.7°C/W。

图 11: TSSOP PCB 布局

通常,这些热通孔使用 0.4 mm 及更小的钻孔直径,以防止出现渗锡。如果 SMT 工艺要求使用更小的孔径,则应增加孔数,以尽可能保持较低的整体热阻。

除了位于板区域的通孔,IC 主体外部区域也设有热通孔。在 TSSOP 封装中,铜区域可延伸至封装末端之外,这为器件中的热量穿过顶部的铜层提供了另一种途径。

QFN 器件封装边缘四周的板避免在顶部使用铜层吸收热量。必须使用热通孔将热量驱散至内层或 PCB 的底层。

图 12 中的 PCB 布局所示为一个小型的 QFN (4 × 4 mm) 器件。在外露板区域中,只容纳了九个热通孔。(见图 12) 因此,该 PCB 的热性能不及图 11 中所示的 TSSOP 封装。

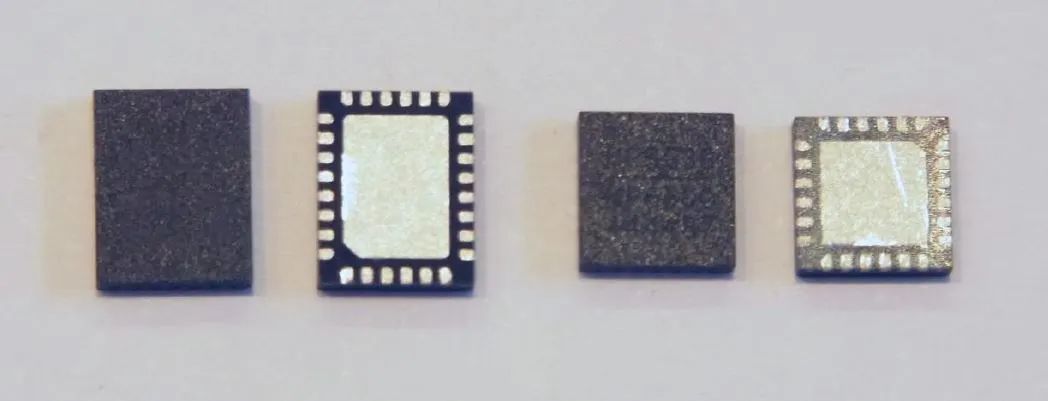

图 12: QFN (4mmx4mm) 布局

倒装芯片 QFN (FCQFN) 封装与常规的 QFN 封装类似,但其芯片采取倒装的方式直接连接至器件底部的板上,而不是使用接合线连接至封装板上。这些板可以置于芯片上的发热功率器件的反面,因此它们通常以长条状而不是小板状布置(见图13)。

图 13: FCQFN 封装

这些封装在芯片的表面采用了多排铜凸点粘接至引线框架(图 14)。

图 14: FCQFN 结构

小通孔可置于板区域内,类似于常规 QFN 封装。在带有电源和接地层的多层板上,通孔可直接将这些板连接至各层。在其他情况下,铜区域必须直接连接至板,以便将 IC 中的热量吸入较大的铜区域中。

图15: FCQFN PCB 布局

图15 显示了所示为 MPS 公司的功率级 IC MP6540 。该器件具有较长的电源和接地板,以及三个输出口。请注意,该封装只有 5mmx5mm。

器件左侧的铜区域为功率输入口。这个较大的铜区域直接连接至器件的两个电源板。

三个输出板连接至器件右侧的铜区域。注意铜区域在退出板之后尽可能地扩展。这样可以充分将热量从板传递到环境空气中。

同时,注意器件右侧两个板中的数排小通孔。这些板均进行了接地,且 PCB 背面放置了一个实心接地层。这些通孔的直径为 0.46 mm,钻孔直径为 0.25 mm。通孔足够小,适合置于板区域内。

综上所述,为了使用 电机驱动器 IC实施成功的 PCB 设计,必须对 PCB 进行精心的布局。因此,本文提供了一些实用性的建议,以期望可以帮助 PCB 设计人员实现PCB板良好的电气和热性能。

作者:Pete Millett, Technical Marketing Engineer, Monolithic Power Systems,来源:MPS

推荐阅读:

1、还在用CAM350吗?

2、我写的东西都在这里了

3、手撕Boost!Boost公式推导及实验验证

4、手撕Buck!Buck公式推导过程

5、开关电源环路学习笔记(一)-为啥要知道传递函数?

6、运放-1-理想运放与虚断虚短的来源

7、为何Layout时信号走线要先过ESD/TVS管?