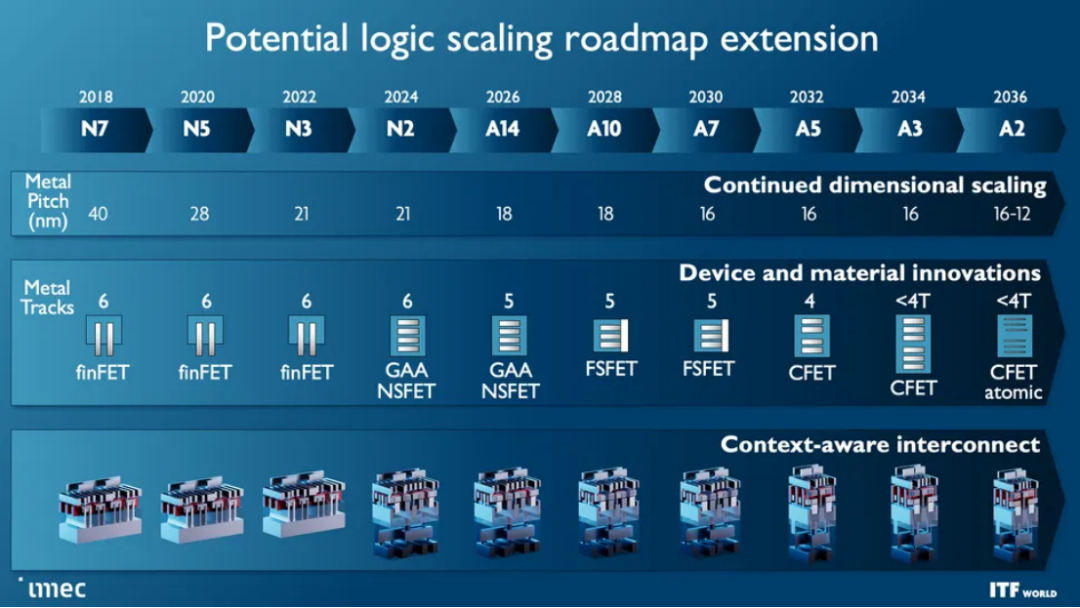

来源:IMEC

来源:IMEC

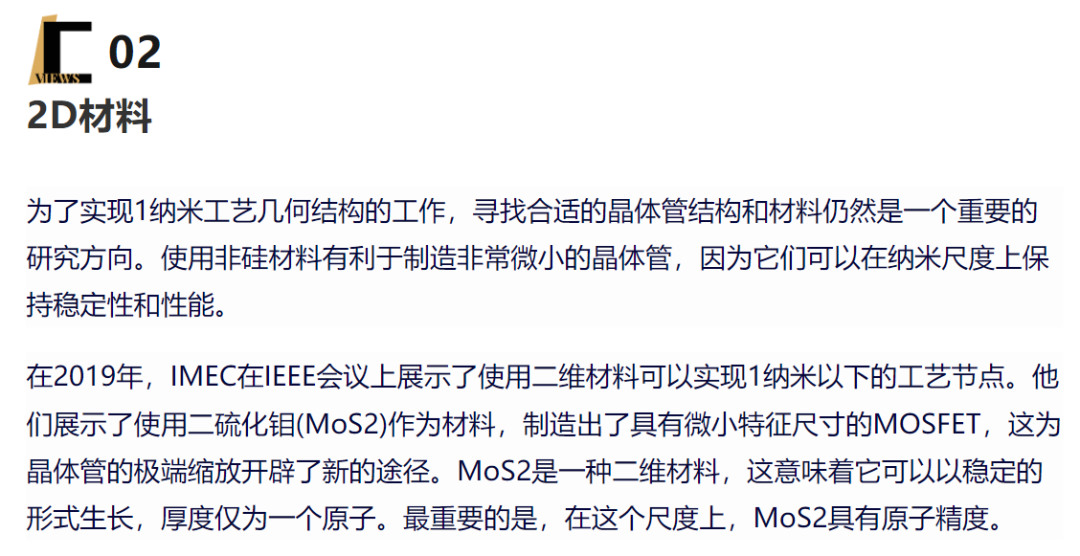

麻省理工学院、南洋理工大学和台积电的研究人员发现,二维材料与半金属铋 (Bi) 结合可实现极低的电阻,克服了实现 1 纳米芯片的挑战。

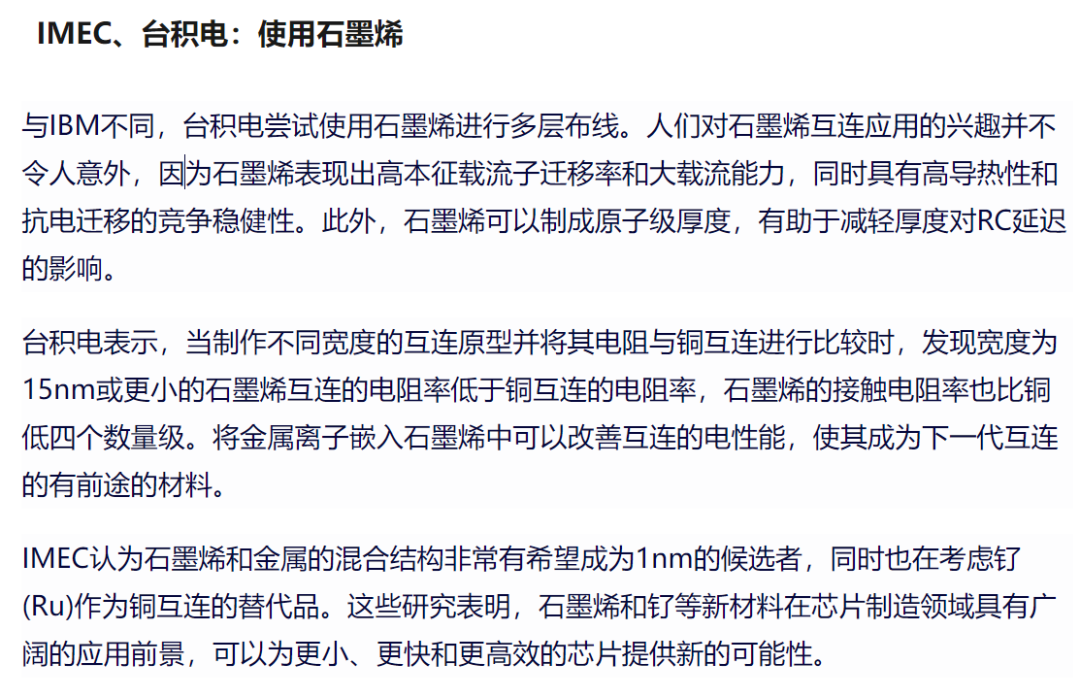

麻省理工学院、南洋理工大学和台积电的研究人员发现,二维材料与半金属铋 (Bi) 结合可实现极低的电阻,克服了实现 1 纳米芯片的挑战。台积电在2D材料方面也取得了突破,逼近1nm工艺节点。他们与麻省理工学院和南洋理工大学合作发表了一篇论文,描述了金属引起的导电间隙对制造挑战的影响,以及单层技术如何受到这些金属引起的间隙的影响。

在论文中,他们建议使用后过渡金属铋和一些半导体单层过渡金属二硫族化物来减小间隙的尺寸,从而生产出比以前小得多的2D晶体管。台积电在实验中尝试了各种低电阻的半导体材料,包括二硫化钼(MoS2)、二硫化钨(WS2)和二硒化钨(WSe2)。

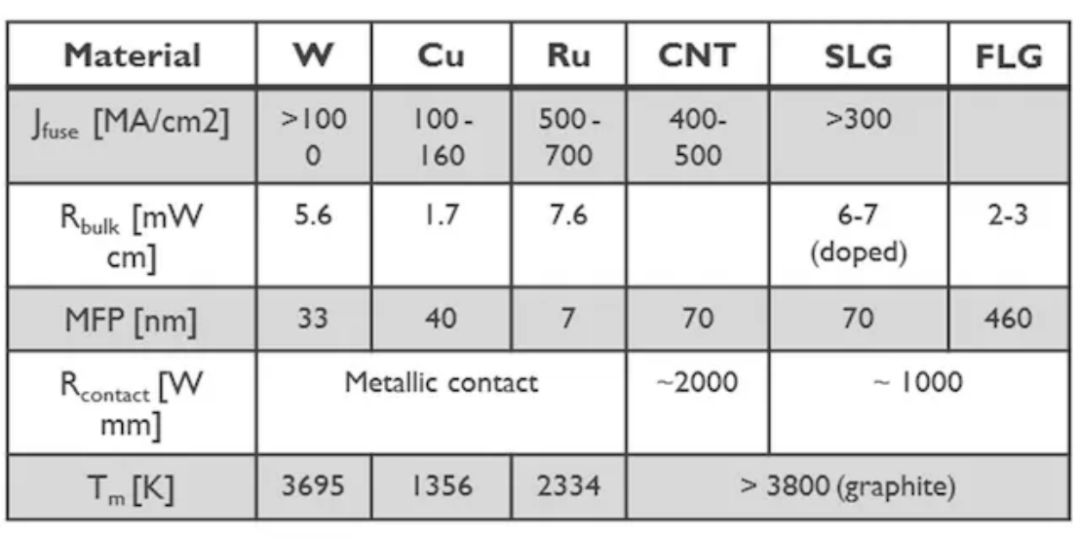

碳纳米管 (CNT)、单层石墨烯 (SLG) 和少层石墨烯 (FLG))与其他相关互连材料(钨 (W)、铜 (Cu) 和钌 (Ru))的性能比较 来源:IMEC

碳纳米管 (CNT)、单层石墨烯 (SLG) 和少层石墨烯 (FLG))与其他相关互连材料(钨 (W)、铜 (Cu) 和钌 (Ru))的性能比较 来源:IMECIBM正在寻找使用钌来解决铜互连遇到的瓶颈问题。钌可以扩展到1纳米及以上节点,并且仍然是一种有效的导体,因此不需要衬垫,这有助于节省空间。

通过减色图案化方法形成的钌也有可能用于一种新型互连集成方案,称为顶通孔集成。在这种情况下,互连通孔形成在导线的顶部,而不是导线的下方,从而允许为最关键的互连层形成连续的导线和自对准通孔。此外,通过这种顶通孔集成牢固地形成嵌入式气隙,从而减少互连寄生电容,也将有助于实现更快、更低功耗的芯片。

IBM的研究人员使用极紫外光刻(EUV)双图案现有的机器上创建测试结构,结果表明能够实现突破。这些研究结果表明,使用钌作为替代材料可以克服铜互连的限制,并为更小、更快和更高效的芯片提供新的可能性。

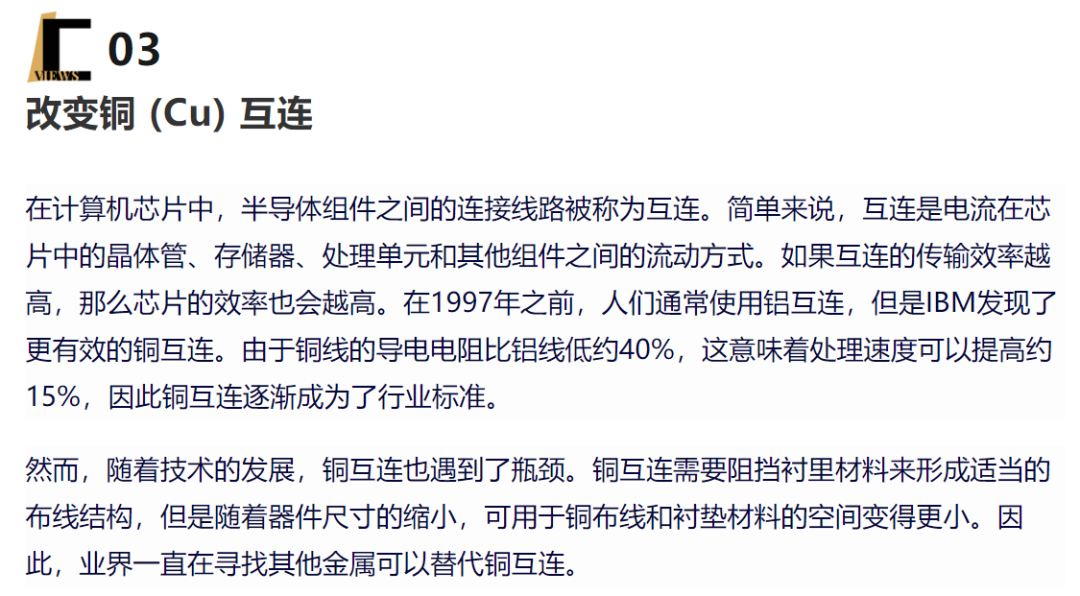

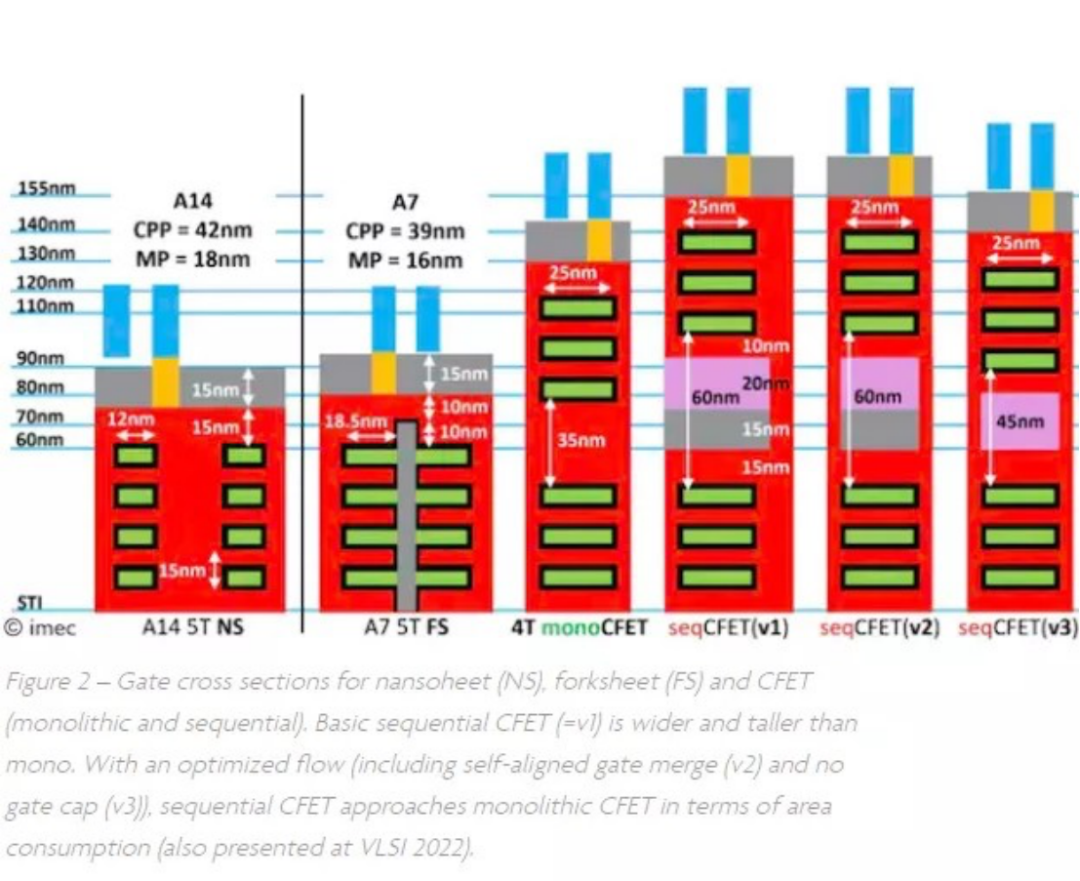

图侧四个结构,均为CFET的变种 来源:imec

图侧四个结构,均为CFET的变种 来源:imec 05

05

总结

在科技领域,1纳米无疑具有巨大的吸引力。然而,1纳米技术也带来了许多挑战。对于许多公司和科研机构来说,1纳米可能是技术上的一个重要目标,它不仅仅代表着物理极限,更是一个巨大的商业机会。例如,1纳米晶体管可以带来更快的处理器、更小的内存单元和更高效的能源储存等。

然而,从目前的技术发展来看,从3纳米到1纳米,摩尔定律的延续面临着巨大的挑战。产业界普遍认为,学术界取得的突破性进展并不一定能很快应用于商业化的芯片生产。例如,3纳米芯片的良率似乎仍是一个问题。因此,要克服1纳米技术所面临的巨大挑战,需要更多的深入研究和探索。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,侵权欢迎联系我们删除!

© 滤波器 微信公众号