近日,马斯克透露,他的人工智能初创公司xAI正计划建造一台超级计算机,并希望在 2025年秋季之前让拟议的超级计算机运行,为其下一版本的人工智能聊天机器人Grok提供算力。

其实,早在今年3月,xAI就发布了其最新版的Grok 1.5。不过,4月,马斯克宣布,由于没有足够多的先进芯片,故推迟了Grok 2模型的训练和发布。他表示,训练Grok2模型需要大约2万块英伟达H100,而Grok3模型及更高版本将需要10万块英伟达H100。完成后,其连接的芯片组将至少是当今最大GPU集群的4倍。

确实,生成式AI从云端走向终端,芯片已经成为推进大模型发展的关键。大模型企业也已经开始将目光聚焦到芯片公司,期待从底层展开合作,以解决算力成本在端侧的覆盖问题。基于算力需求,芯片厂商与大模型厂商走得更近了。

在泰克最新对清华大学教授高滨的采访中,他表示:“自2023年开始,大模型就非常火。国际上、以及几个大公司都在研究怎么去支持大模型。从新的器件到新的工艺,这几个公司的技术路线都不太一样。有的相对传统一些,有的尝试用新工艺新器件去做。在去年的IEDM大会中,还专门设置了一个探讨大模型的section。”

高滨老师特别强调说:“大模型不仅仅是算法和应用上,其实底层的算力支撑也是非常重要。”

大模型与存算一体技术

当前,各行各业都在数字化转型,数据处理和存储的需求与日俱增。传统的计算与存储的模式已经很难满足当下高性能、低能耗、强安全的需求。存算一体技术被认为是可以有效解决传统冯·诺依曼架构下的“存储墙”和“功耗墙”问题的有效途径。

存算一体的优势是打破存储墙,消除不必要的数据搬移延迟和功耗,并使用存储单元提升算力,成百上千倍的提高计算效率,降低成本。除了用于AI计算外,存算技术也可用于存算一体芯片和类脑芯片,代表了未来主流的大数据计算芯片架构。

高滨老师表示,大模型对功耗及成本的要求很高。如果忆阻器真的能应用到大模型里面的话,能效比预计将会有数量级的提升。现在大模型基本都是在云端,未来在端侧,功耗将会是一个非常大的挑战。忆阻器这种高能效的优势在端侧就会有很多的优势。

高滨老师分享了近两三年的研究重点,主要是希望把存算一体的技术往应用上去牵引,具体在开展的工作包括以下三大方面:

与企业合作。尝试在实际边缘智能的场景中做芯片设计,以及实际场景下的可靠性。高滨老师特别指出:“我们发现,在很多实际场景下,芯片电阻状态的保持其实是存在随机偏移的relaxation效应的,如何抑制随机偏移,以满足未来的应用需求,这是当前非常重要的课题。”

大模型的应用研究,主要是致力于提高密度。传统的小的卷积网络加速是不需要高密度的,但大模型需要。希望把密度尽可能的做高。以前做小的卷积网络的加速,其实不需要这么高的密度。但是大模型需要。这其实主要是工艺方面的研究。

类脑学习。这是更前沿更创新的领域,除了去年十月在Science上发表的新近研究成果之外,其实清华大学还在布局新型类脑计算,它更看重整体算法效果,而非器件个体,最后是落实到器件上去做优化,调节器件中的电子离子的输运。

后摩尔时代,从系统层面进行顶层规划,根据系统需求优化器件,并做好器件与系统的协同设计,这点这尤为重要。就此,高滨老师特别分享了后摩尔时代,系统和器件的全新范式的研究模式。

系统和器件的全新范式的研究模式

摩尔定律的黄金时代,主要是将晶体管、电阻、电容和电感等元器件集成在一起,并形成具有预期功能的电路。这个时期,不太需要在意系统和器件的协同,只要器件做的足够小,芯片的性能大体就能得到保证。

但是,后摩尔时代,应用场景的需求正向着高密度、小型化、强功能、低功耗、低成本、高可靠、易设计等方向发展,已经不仅仅是简单的电路设计,而是要做系统化的集成。很多时候,需要把系统和器件做一个协同的设计,根据系统的需求去优化器件,很典型的就是存算一体,最终目的是要做人工智能的加速。

高滨老师进一步分享说,人工智能对器件性能的要求很复杂,不是单纯把器件阻值调稳,就能达到系统要求。如加速一个深度神经网络,它的卷积层、全连接层等各种层,其实对器件的性能要求都不一样。器件的指标很难抽象到具体的数值标准,以保证芯片设计的好坏。

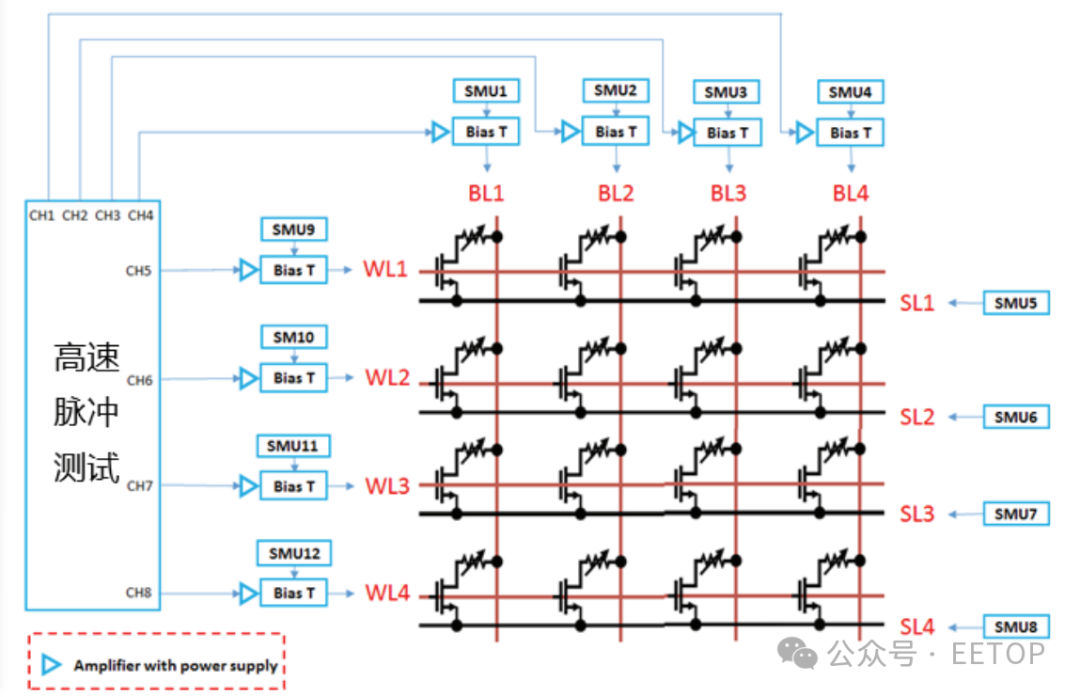

比较全新的一个概念就是做阵列测试。不一样的算法模型解决不一样的数学问题,从底层的设计是有区别的,对器件的要求也不一样。所以在小规模的阵列上,去做测试和研究,是有助于做器件的优化的。

图为一个 4X4 1T1R 阵列测试框图。从框图可以看出,阵列测试不仅测试硬件连接复杂,其控制流程及测试序列更需要定制。

高滨老师特别强调说:“不过最好还是要落实到器件上去做优化。去调整器件里面电子、离子的输运,最后去看整体算法的效果。这其实就是系统和器件之间的协同发展。”

而在新器件工艺上,当前摩尔定律正面临极限挑战,一个方向是继续“延续摩尔定律”。国际上几大公司,都还在不断研究新的先进工艺,如堆叠三维基层晶体管。但门槛太高,能做的企业寥寥无几。

高滨老师分享说:“目前另一个新的方向是单片三维集层,它与现在较热的 chiplet,其实是平行路线。具体做法是,在一个衬底上尽量把很多器件三维堆叠起来。相对chiplet,其器件间的带宽会更高。这是一个新的趋势,可用新型 TFT 材料、薄膜氧化物、二维材料等尝试做成后端兼容器件。”

面向传统存算分离架构制约算力提升的重大挑战,去年十月,清华大学吴华强、高滨团队成功研制出了国际首颗支持片上学习的忆阻器存算一体芯片,提出了一种适于忆阻器实现高效片上学习的新型通用神经网络算法和STELLAR架构,有效实现大规模模拟型忆阻器阵列与CMOS的单片三维集成,并成功演示了图像分类、语音识别和控制任务等多种片上增量学习功能。该成果通过算法、架构、集成方式的全流程协同创新,展示出高适应性、高能效、高通用性、高准确率等特点,为发展高算力芯片探索出了一条创新路径。

忆阻器的发展趋势

在新兴的信息时代,发展和探究忆阻器的各种性能刻不容缓。忆阻器全称记忆电阻,是一种具有电荷记忆功能的非线性电阻,于1971年,由加州大学伯克利分校的华裔科学家蔡少棠教授提出。蔡教授从电路完整性角度出发,从数学上推导出忆阻器的概念。

忆阻器是神经元网络的核心器件,它为发展信息存储与处理融合的新型计算体系架构,突破传统冯·诺伊曼架构瓶颈,提供了可行的路线,其性能直接影响神经元网络的计算能力。

忆阻器的发展有三个阶段:

第一个阶段主要做存储;

第二阶段,就是现在做的存算一体,加速人工神经网络的;

第三便是类脑计算,不过它本质还是忆阻器,因为它需要利用忆阻器的一些动力学特性。忆阻器主要是调节内部的离子输运,存算一体更多是利用它的静态过程。未来还可以利用电离子的很多动态过程,去做更像神经元的一些行为。

忆阻器也是目前材料和电子领域的研究前沿和热点。其中,氧化物材料在忆阻器研究中具有重大价值。高滨老师分享说:“虽然对于氧化物忆阻器目前看似已经到了发展的瓶颈期,但未来,还是有好几个突破点的。”

据高滨老师分享,可靠性和密度是非常值得关注的方向。

可靠性。一个器件能调节出很多个稳定的电路状态,叫多比特存储。只有做到多比特存储,很多计算的效率才能提高。而多比特存储,目前最高阻和最低阻都比较稳定。但中间阻态,由于原子分布的形貌比较特殊,就没那么稳定,这很大程度就限制了忆阻器的应用。如何把中间阻态做稳定,本身是一个科学问题。以及如何同时去监测中间阻态,对测试也提出了很大的挑战。

密度。高滨老师表示,终极目标是希望能与 M3D 高密度存储器拼密度,但这很难做到。清华大学现在在尝试用HBM的方式,把多片忆阻器堆叠起来。这就需要把片内忆阻器的尺寸尽量做小。其中面临的挑战就是忆阻器和晶体管的匹配问题,需要两者的共同优化,本质还是工艺。

高滨老师满怀期望的分享到:“未来,忆阻器还有可能会应用到高速存储,用忆阻器去研究忆阻器,就像用人去研究生物。这将是更高阶的智能。这个方向,我觉得在学术界,还是非常值得去探索的。但是短期落地还是有困难的。因为现在想做大规模的,无论是在工艺上,还是在算法上,都还存在很多挑战。不过,由高校牵头去探索,确实是一个非常好的方向。”

存算器件的发展与测试需求

类脑计算的研究,本身需要用到动力学特性,希望能看到电阻随时间怎么变。同时,希望有很多电阻状态,并且能监控每一个电阻状态的情况。其中,静态情况的保持,需要关注绝对的电阻数值;动态的,涉及到读和写的切换,速度越快越好。几纳秒的时钟内完成切换。

器件的测试结果,其实是没办法直接转换到芯片里面去做。在器件状态就得去做芯片方面的模拟测试。在静态测试转向动态测试,对于微安级的电流,需要有纳秒级别的写入或者读出,跟调控阻态的时候希望能有更精准的写和读,是相近的需求。

高滨老师表示,他们现在想做模仿类脑的神经形态器件,其实也是受限于设备。他分享说:“我们看到,近几年有一些这方面的研究,但是速度基本也都是在毫秒,也有可能是因为大脑就是毫秒,所以我们也就是做到毫秒。但如果能做到比大脑快,那肯定更好。”

现在超级神经元在毫秒量级,会有一个动力学的响应,器件可以做的很快,能做到纳秒量级的响应,是比生物量级快的一个超级大脑。我们相信,随着技术的不断进步和应用的不断拓展,存算一体技术将在更多领域发挥重要作用。

我们精心为您准备了忆阻器、存算一体芯片设计与测试相关的白皮书、测试方案,以及技术讲堂视频。帮助您深度了解该领域的相关知识。

资料清单一览

PDF文件:

1、忆阻器白皮书

2、神经形态计算器件和阵列测试解决方案

3、忆阻器单元基础研究测试方案

4、忆阻器单元性能研究测试方案

5、低维神经元网络阵列测试方案

6、神经元网络阵列测试方案

7、三端器件节点神经元网络阵列测试方案

视频文件:

1、技术讲堂:忆阻器存算一体芯片(主讲嘉宾:清华大学教授 高滨)

人工智能与芯片算力

存算一体技术

研究进展

器件测试的新挑战

2、技术讲堂:大模型时代的存算一体芯片(主讲嘉宾:清华大学教授 高滨)

大模型与存储墙

存算一体芯片技术

存算一体器件、工艺与芯片

存算器件的发展及测试需求

3、技术大讲堂:忆阻器的发展及测试(主讲嘉宾:泰克科技)

忆阻器的发展

忆阻器的测试问题及流程

基于忆阻器神经元/神经突触性能测试

4、专访:清华大学教授 高滨

基于忆阻器科研,探讨忆阻器、类脑计算科研进展,展望系统和器件协同测试未来可能性。

忆阻器资料包

扫一扫二维码

申请获取资料