前面我们分析了板载的资源,现在来创建工程进行测试。

vitis安装参见文章:《基于“矿板”低成本学习Zynq系列》之三-vitis安装https://mp.weixin.qq.com/s/30BN9VFjTkOpPZWRTDCVUg 文中介绍的是2023版,我这里安装的是最新版本2024.1,安装过程是一样的。

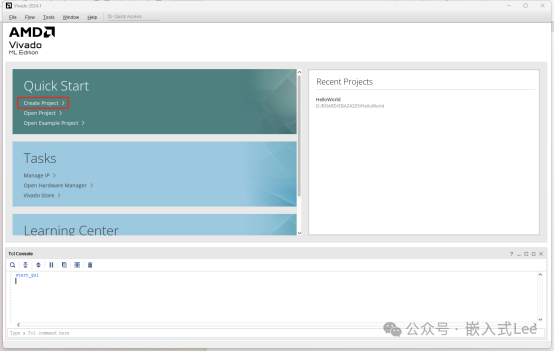

打开Vivado

创建工程

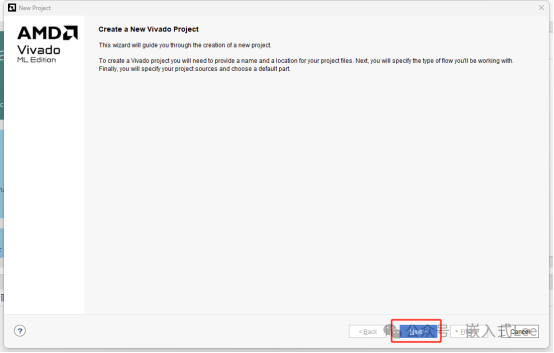

Next

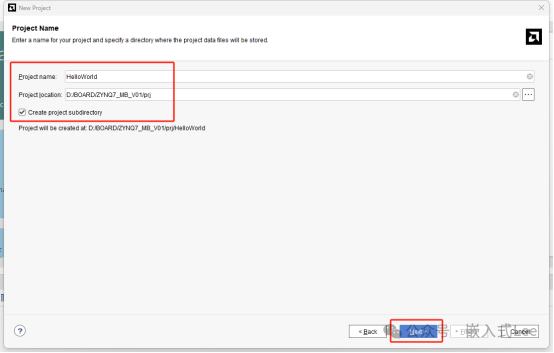

指定工程名和路径,Next

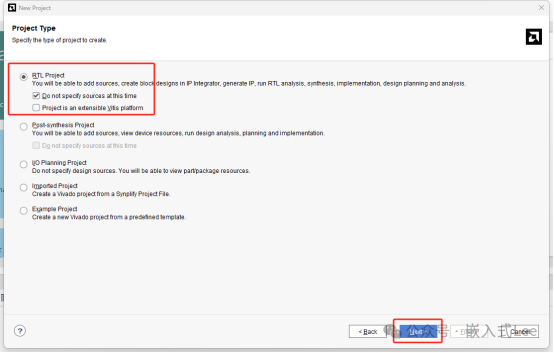

指定RTL Project,Next

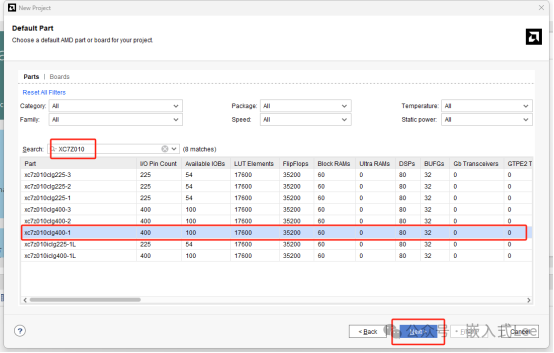

搜xc7z010,选择指定的SOC型号,xc7z010clg400-1,Next

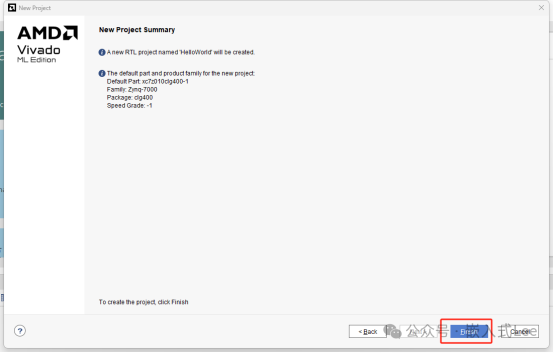

Finish

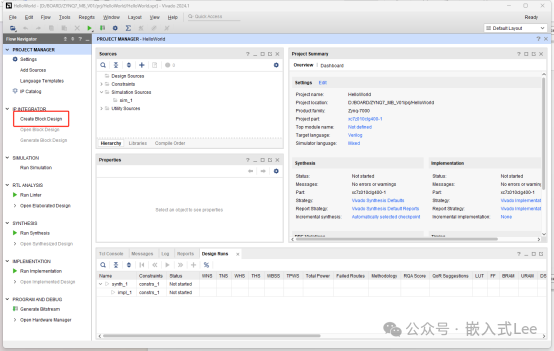

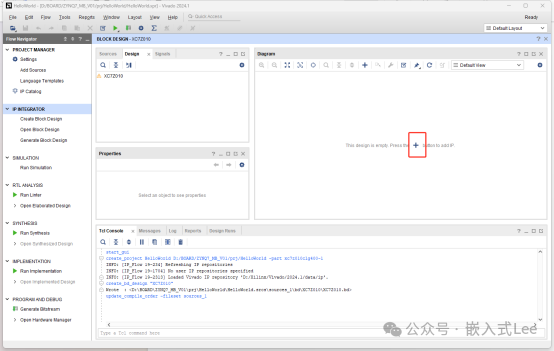

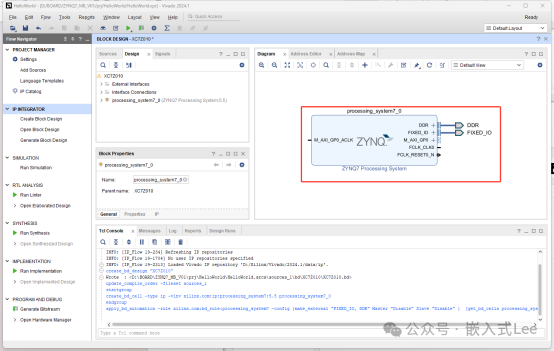

Create Block Design

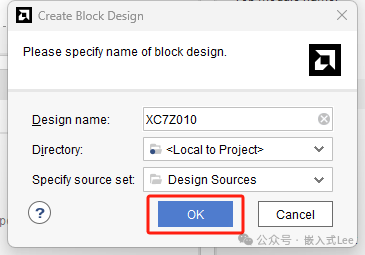

指定名字XC7Z010,点击OK

点击空白处的+号

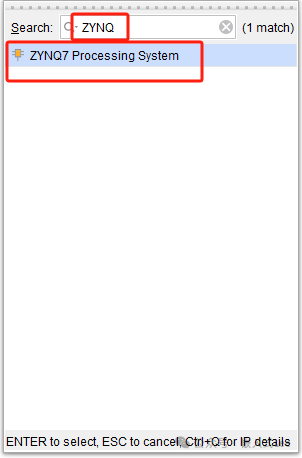

搜索zynq,双击ZYNQ7处理器系统

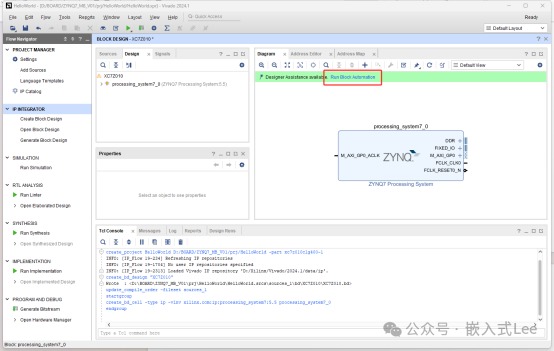

点击Run Block Automation

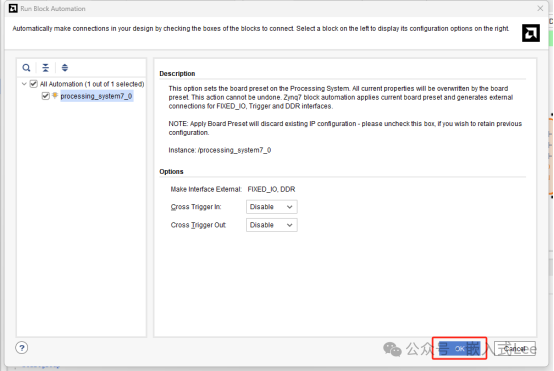

点击OK

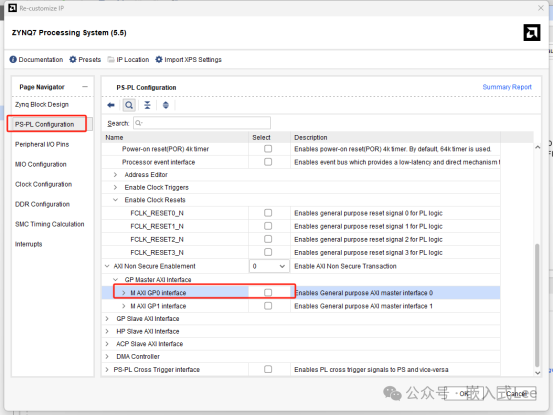

双击如下框图

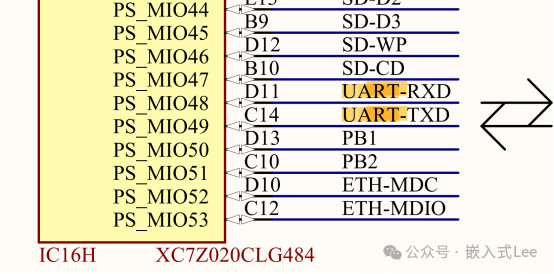

参考ZedBoard原理图

猜测和其一样是MIO48和MIO49

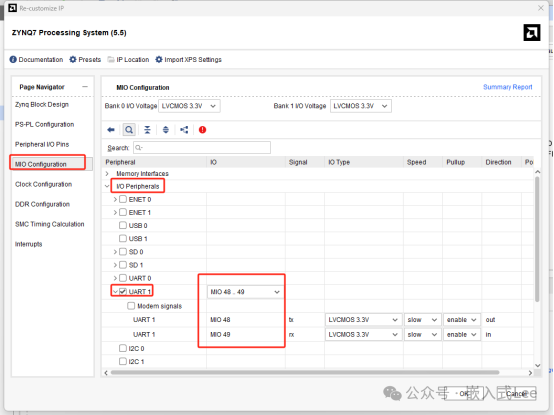

MIO Configuration->I/O Peripherals->勾选UART1,选择MIO48和MIO49

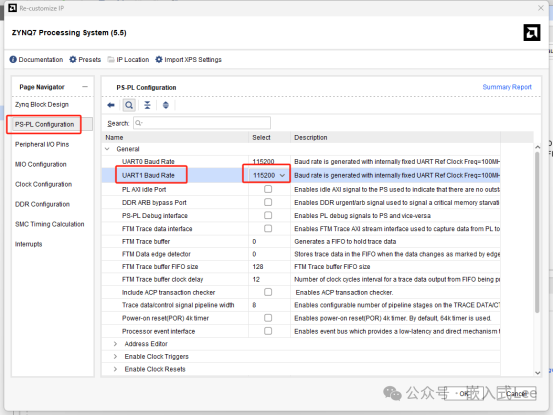

设置串口波特率为115200

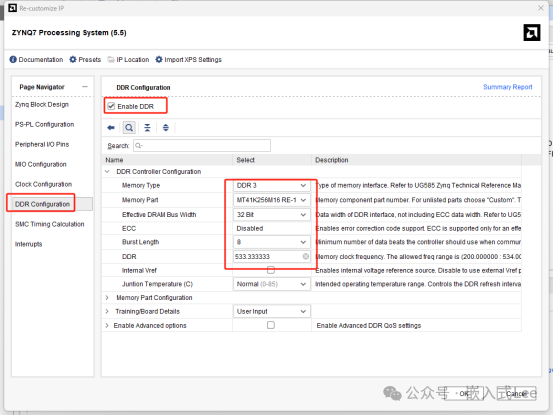

配置DDR

MT41K256M16,32位

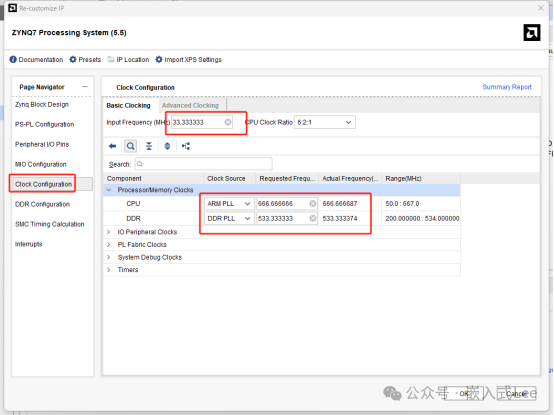

时钟配置,和外部晶振33.333MHz保持一致,其他默认

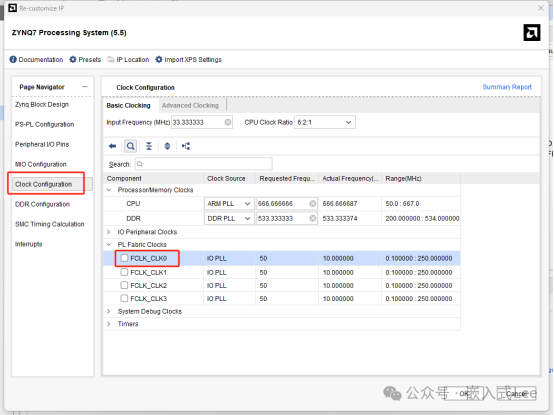

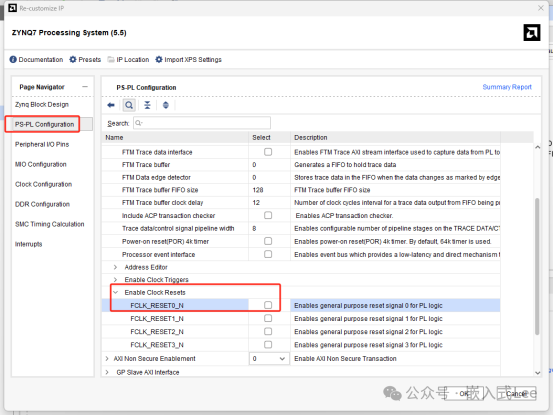

取消未用时钟

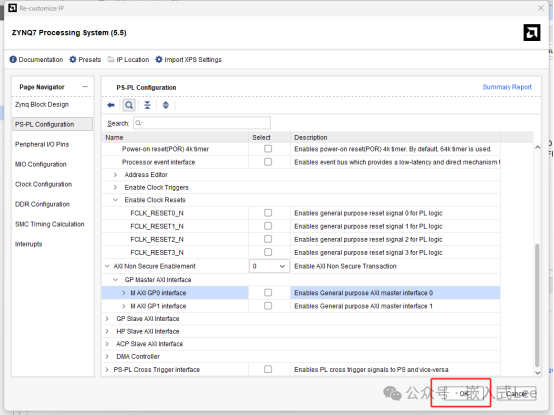

配置完点击OK

点击如下图标,弹出对话框点击OK

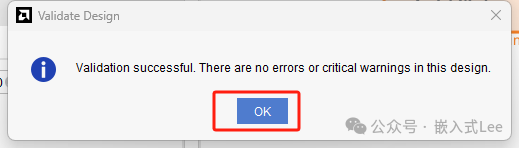

点击Sources选择刚创建的设计,右键点击->Generate Output Products

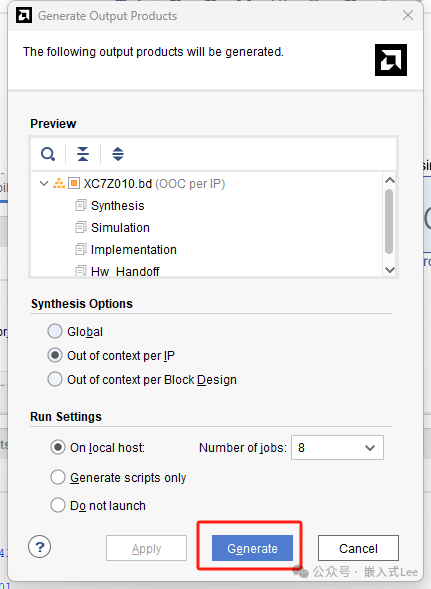

默认配置点击Generate

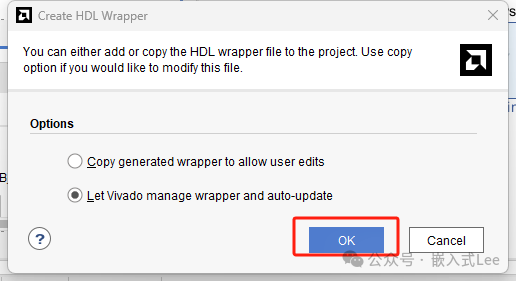

再次右键点击设计->Create HDL Wrapper

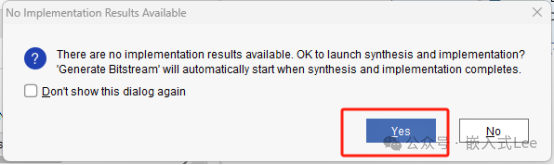

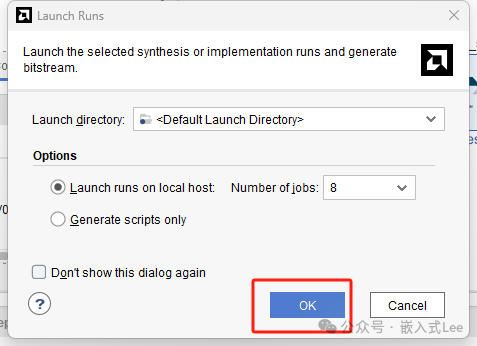

点击如下图标,默认配置即可

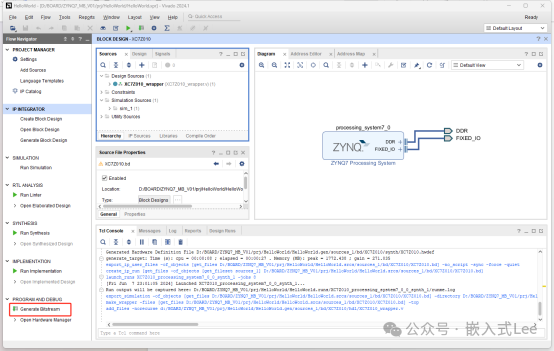

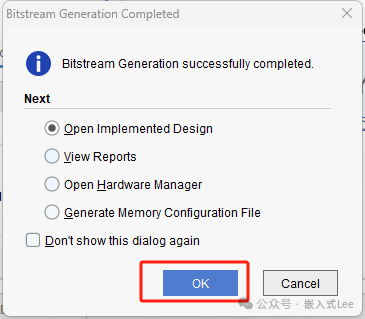

需要稍等一会

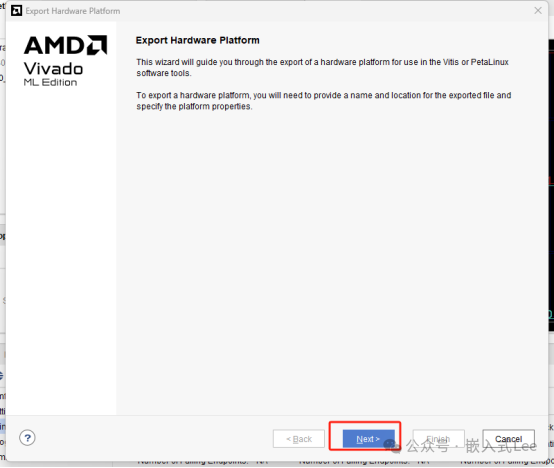

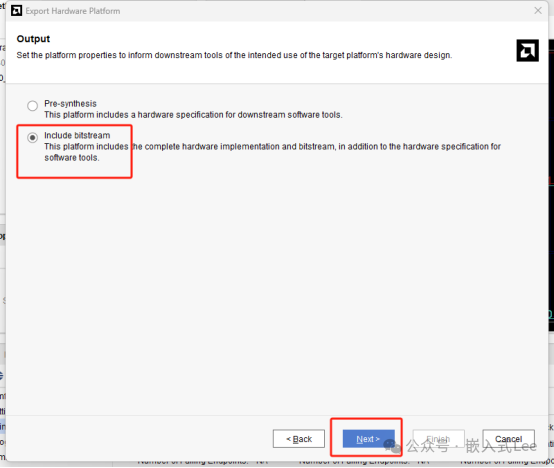

File->Export->Export Hard ware

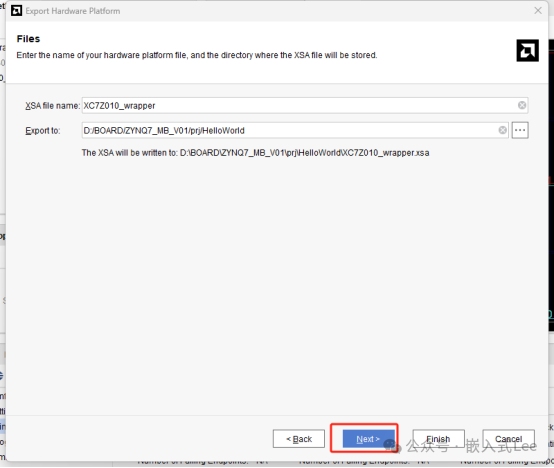

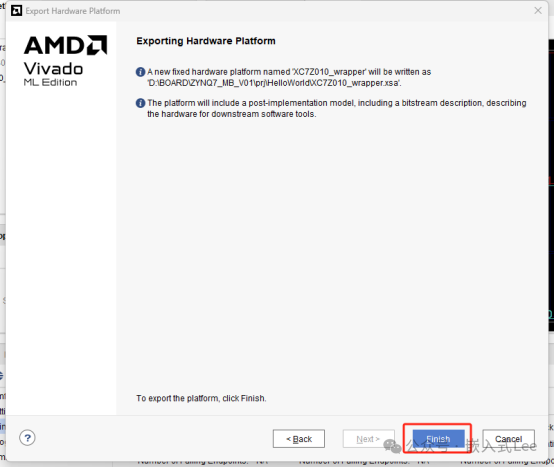

导出的是xsa文件

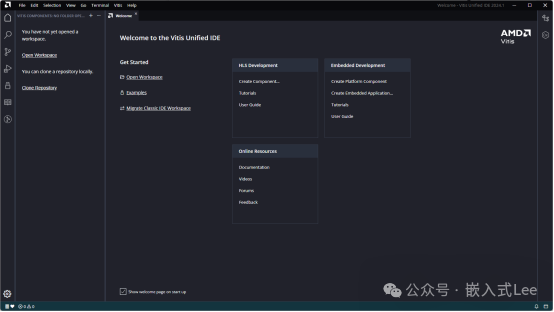

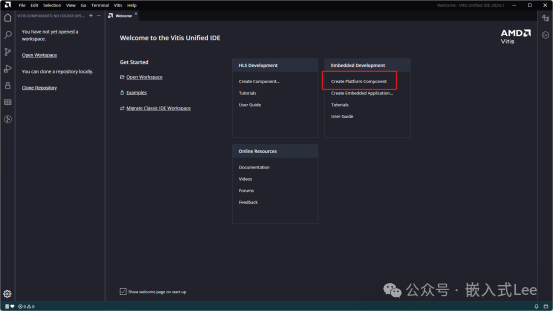

启动Vitis

Tools->Launch Vitis IDE

Create Platform Component

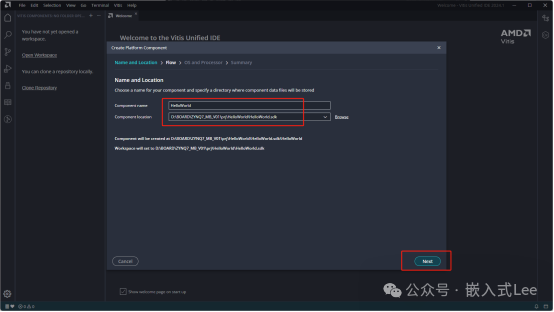

D:\BOARD\ZYNQ7_MB_V01\prj\HelloWorld下创建文件夹HelloWorld.sdk

设置名字HelloWorld,指定路径为刚创建的HelloWorld.sdk,Next

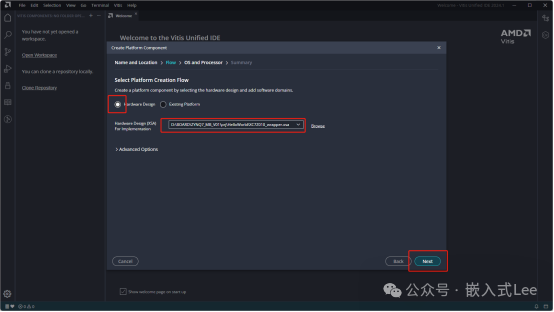

选择之前生成的xsa文件,Next

D:\BOARD\ZYNQ7_MB_V01\prj\HelloWorld\XC7Z010_wrapper.xsa

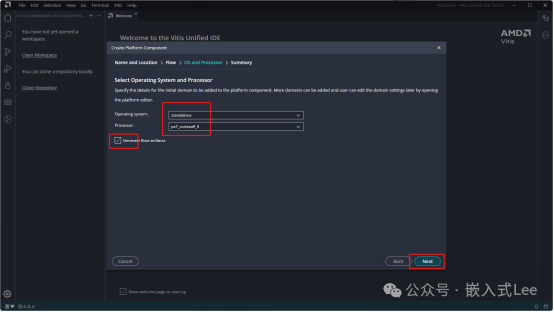

选择standalone程序,core0,勾选,Next

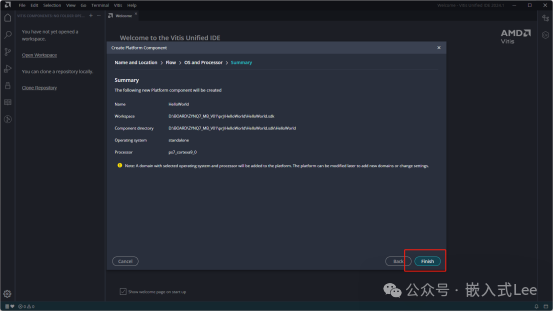

Finish

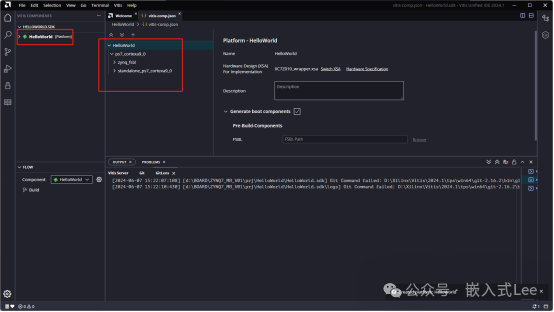

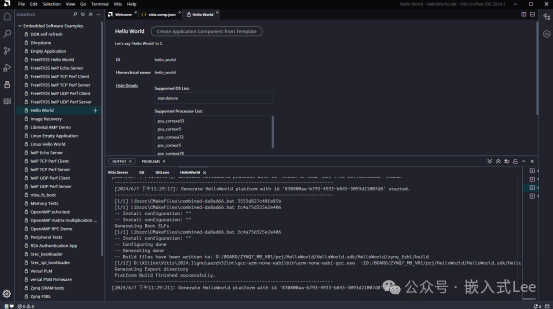

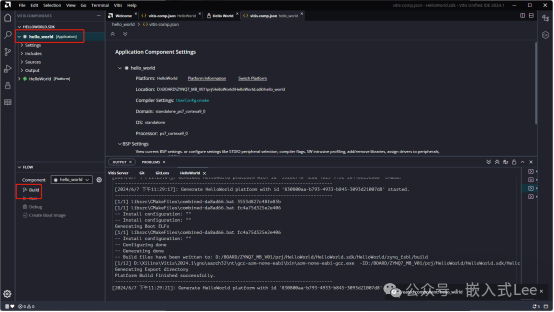

生成工程如下

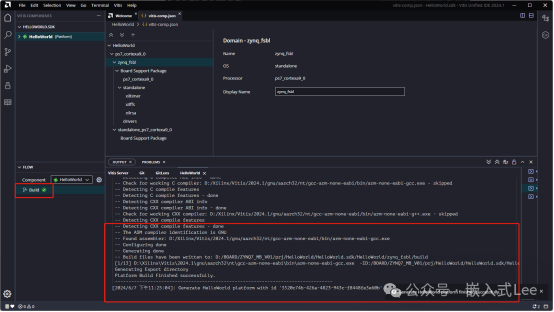

点击如下图标编译

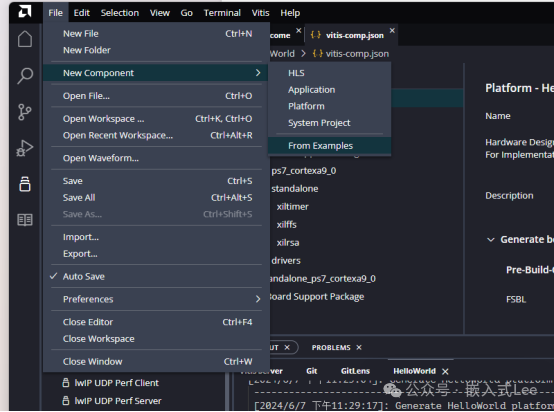

File->New Component->From Examples

点击HelloWorld后面的+

点击Next

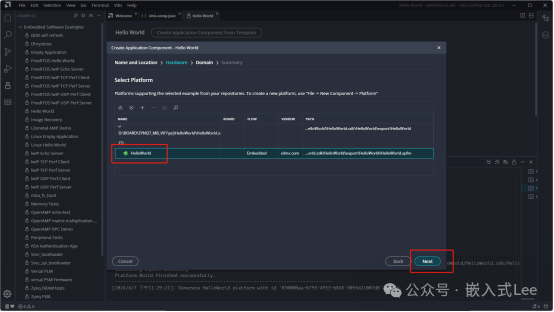

指定刚才创建的平台HelloWorld,点击Next

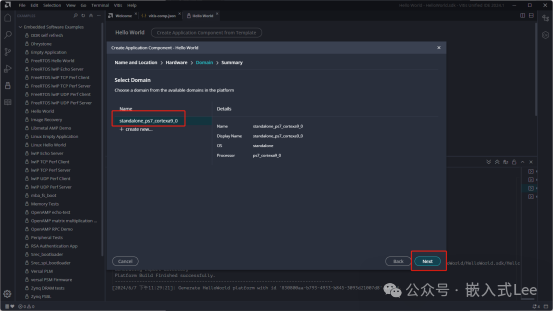

点击之前指定的core0,点击Next

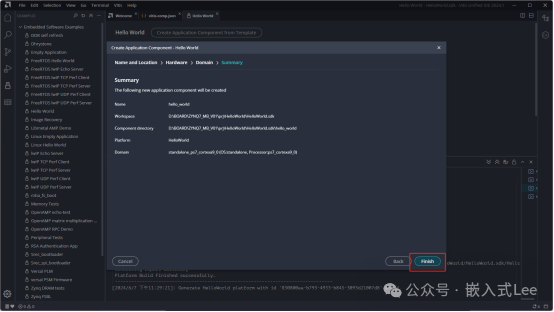

Finish

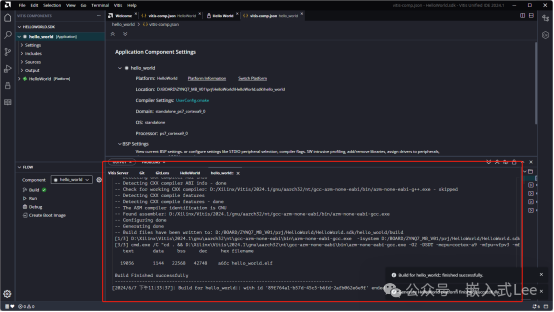

编译应用

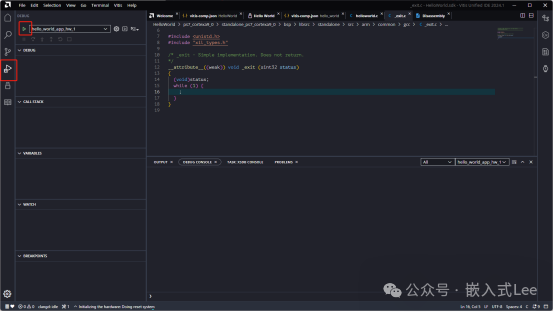

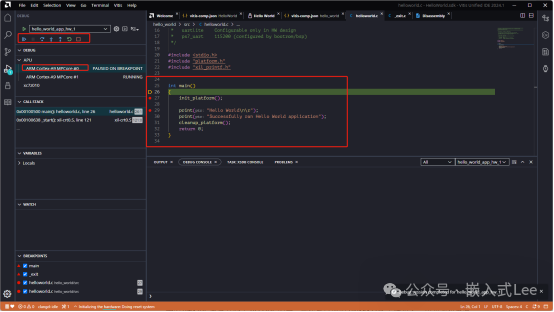

点击如下图标进入debug

可以单步运行

新的vitis IDE基于VSCODE,操作比以前的Vivado SDK方便很多,用起来也感觉顺手很多。

以上测试可以确认板子基本没问题,后面就可以编写程序遍历各个IO,确认各个接口和IO的对应关系。