芝能智芯出品

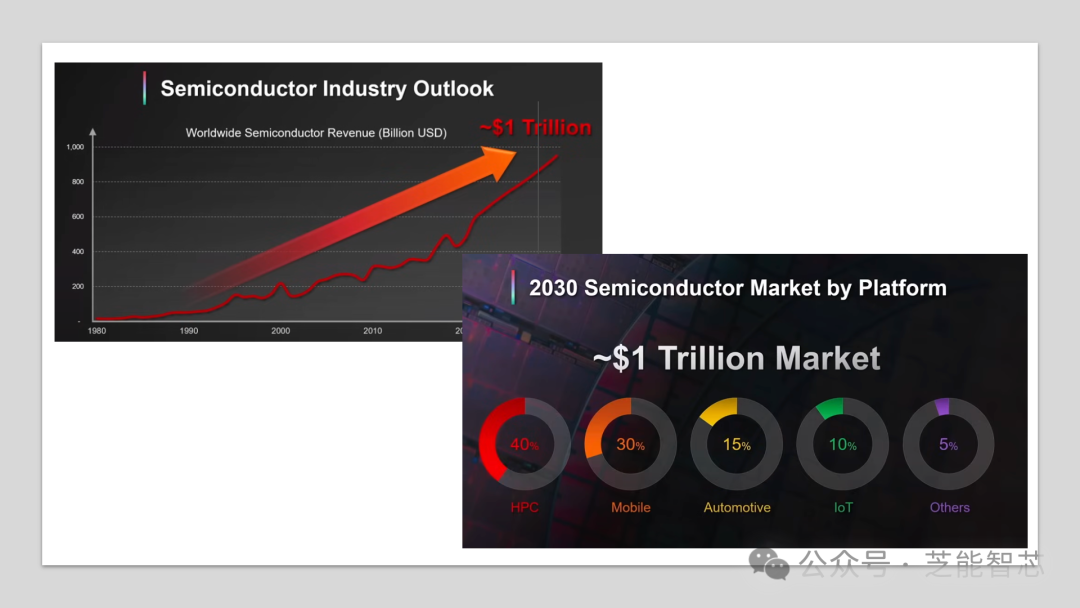

ISSCC2024年,台积电副总裁Kevin Zhang在2024年年度会议上1.1环节讲了《Semiconductor Industry: Present & Future 》,半导体行业在5G、人工智能和高性能计算等多年大趋势的推动下,展现出强劲的长期增长势头,不受周期性和宏观经济挑战的影响。

备注:视频已经下载下来了,我们开设了芝能智芯的星球,后续有价值的视频、白皮书,我们都会放进去。

预计高性能计算、智能手机、汽车和物联网这四个细分市场将占据接近万亿美元半导体业务的95%。

● 高性能计算(HPC)需求占比最大,达到40%;

● 智能手机占30%;

● 汽车和物联网分别占15%和10%。

人工智能与高性能计算

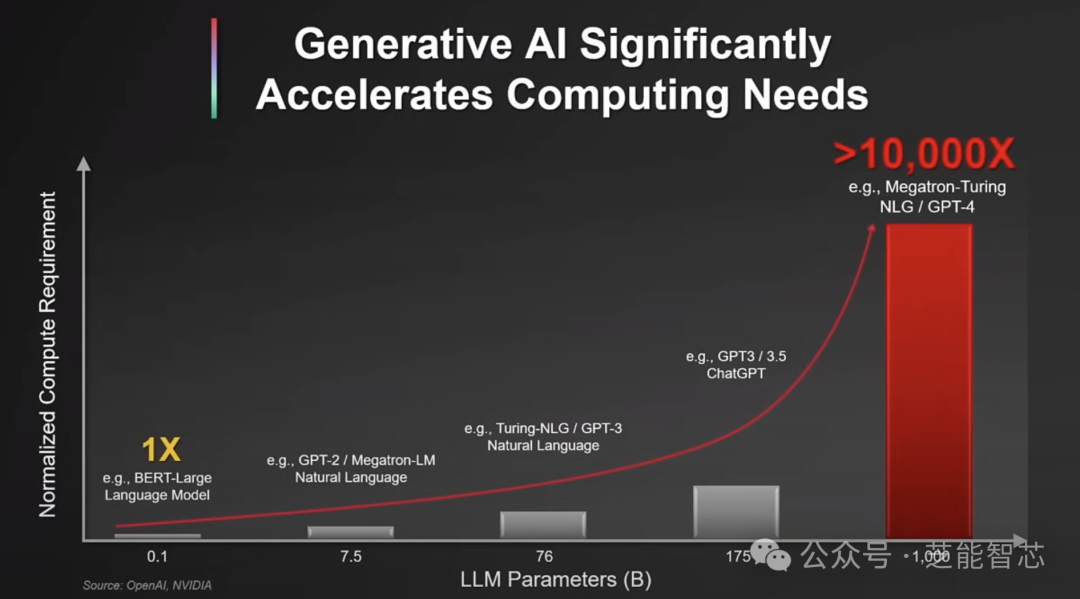

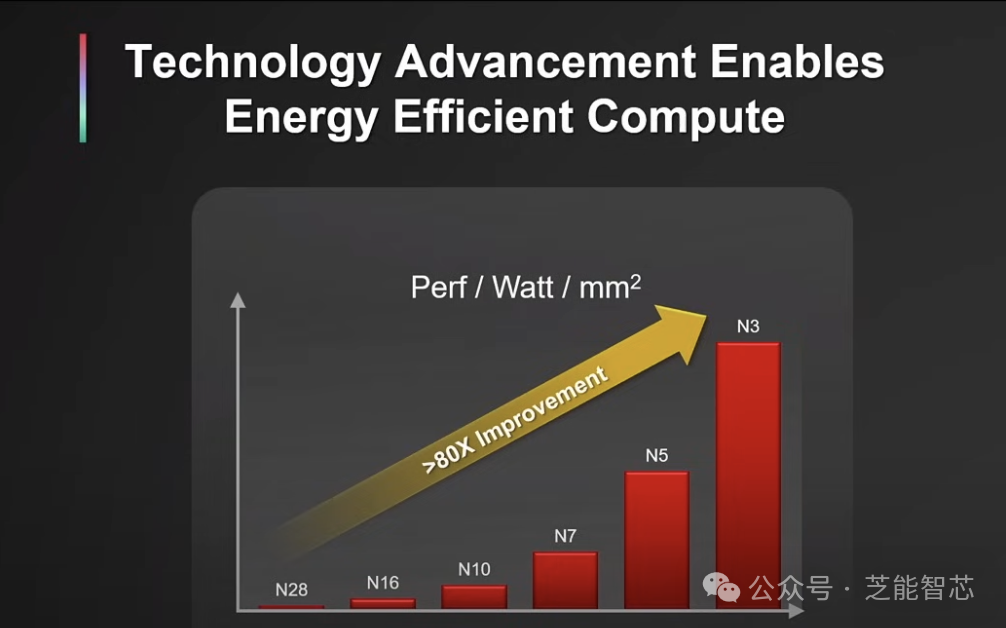

人工智能(AI)已迅速成为高性能计算(HPC)应用的关键驱动力。用于生成式人工智能的前沿大型语言模型(LLMs)的复杂性不断增加,其计算需求呈指数级增长。

在不到两年的时间里,LLMs的计算需求增长了超过10,000倍。随着这些模型的计算需求不断增加,半导体行业的创新也在加速。

从应用端来看,

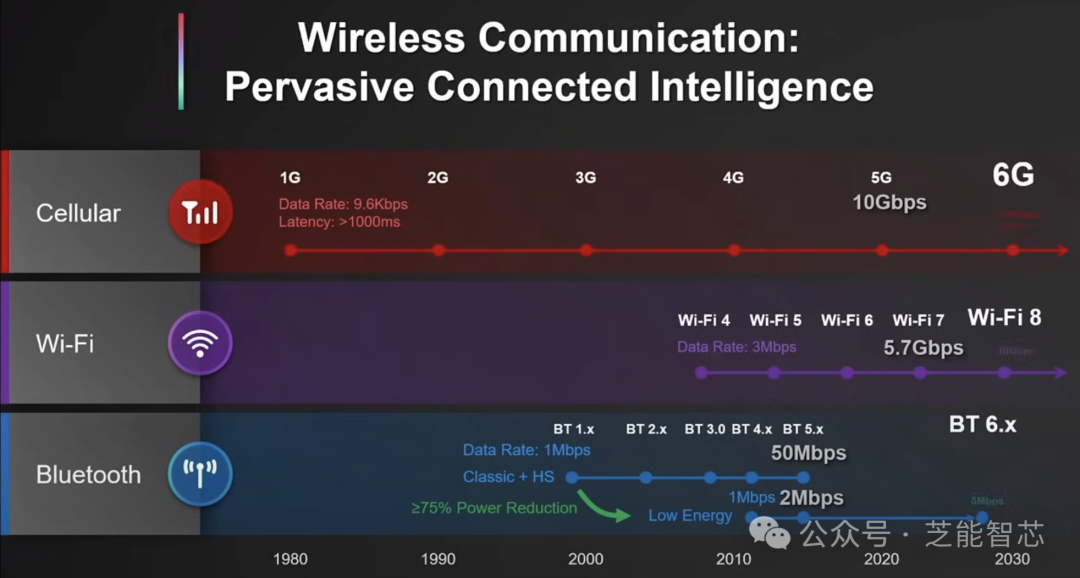

● 无限通信围绕6G、Wi-Fi8和BT6.X进行迭代。

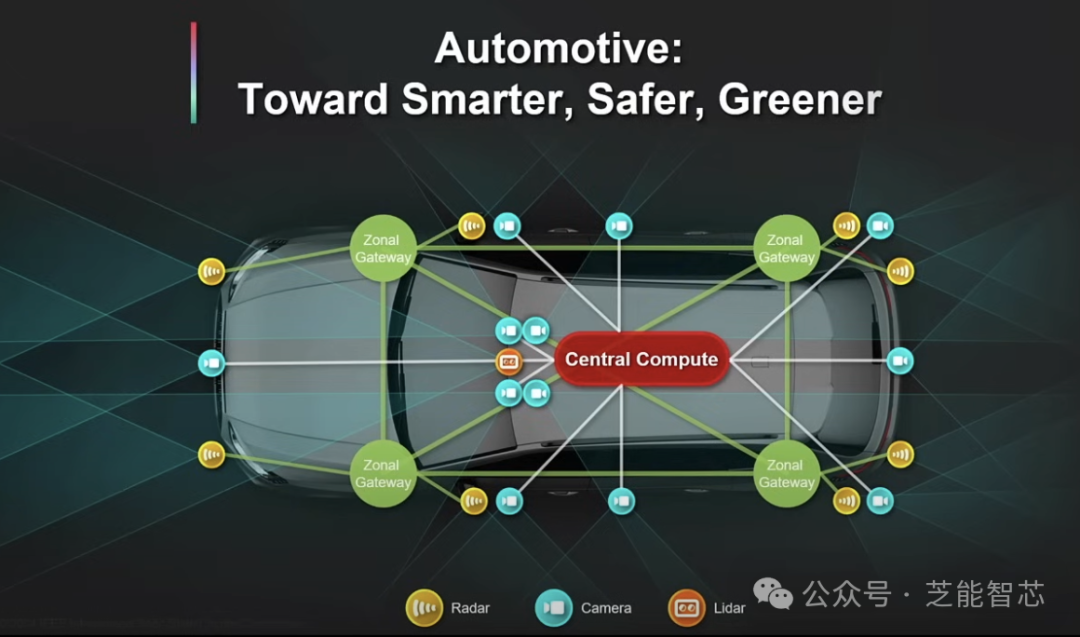

● 汽车围绕着更智能、更安全和更环保的方向发展,架构上更智能。

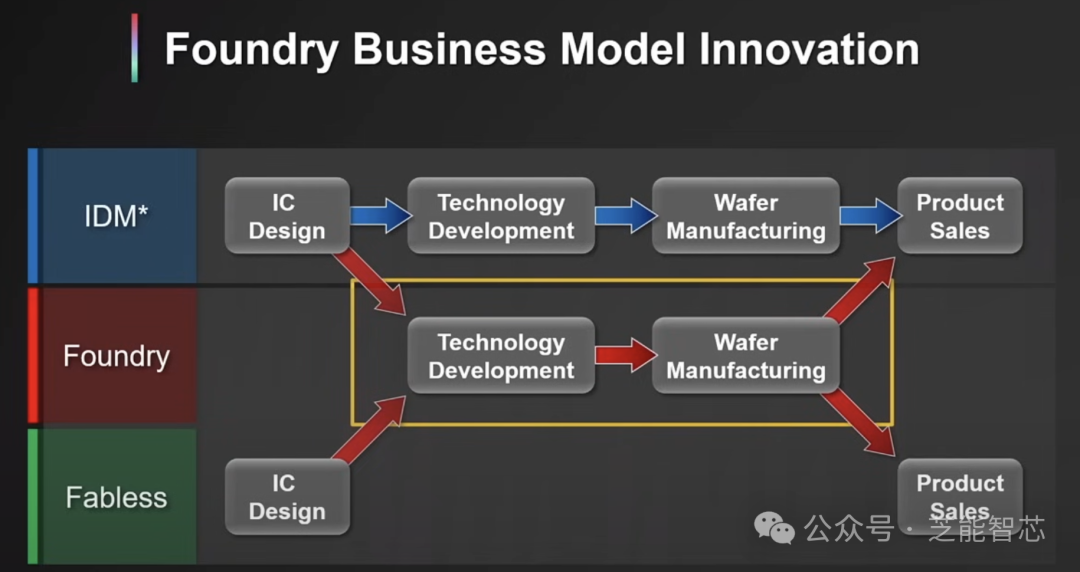

● 芯片代工业务模式的核心逻辑,围绕技术开发和制造的精益。

这里是叙述芯片代工企业的核心价值,进一步占据市场最重要的份额模式。

光刻技术的进步

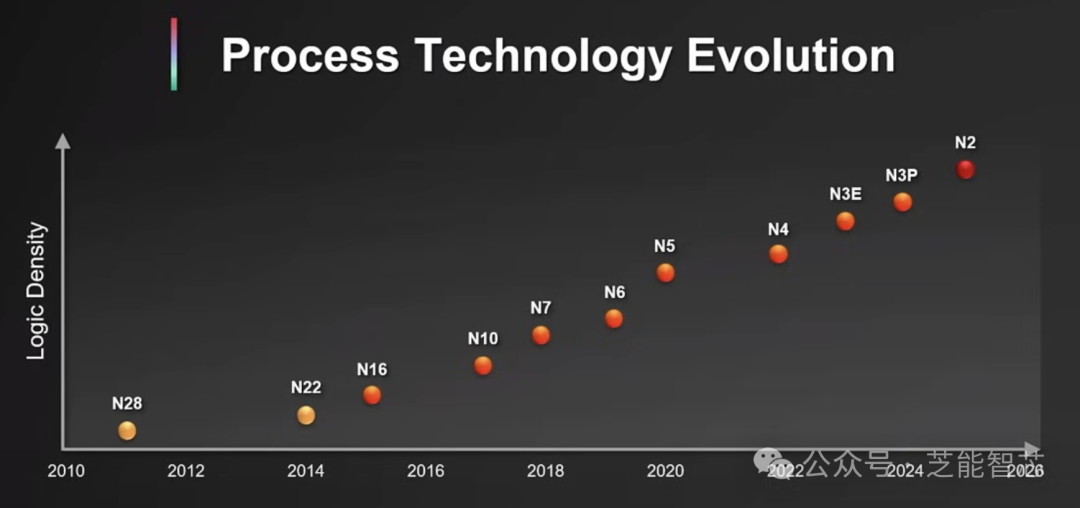

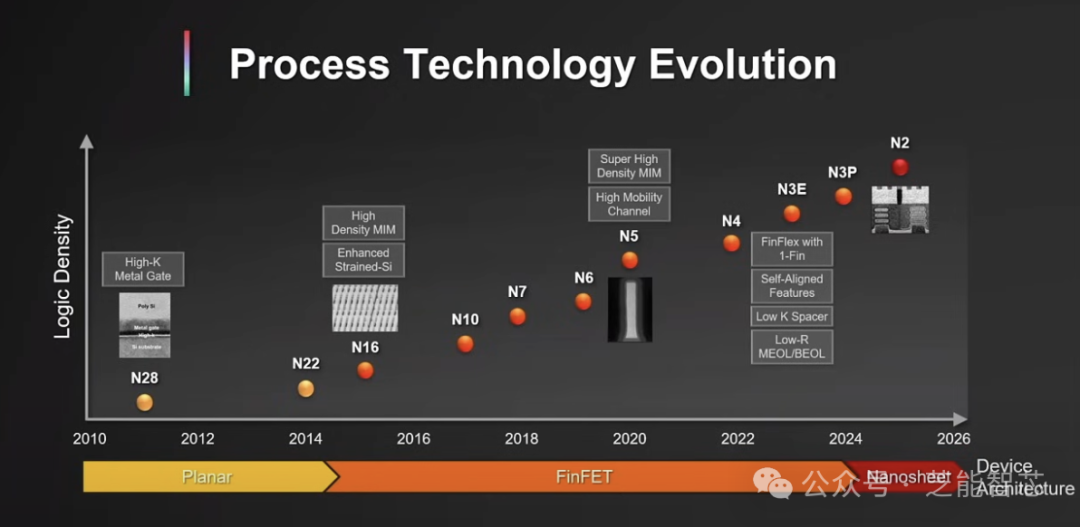

光刻技术在半导体制造中扮演着重要角色。随着时间的推移,光刻技术从单图案沉浸发展到双图案沉浸,再发展到具有自对准特征的双图案沉浸,以便打印出越来越小的临界尺寸(CD)。

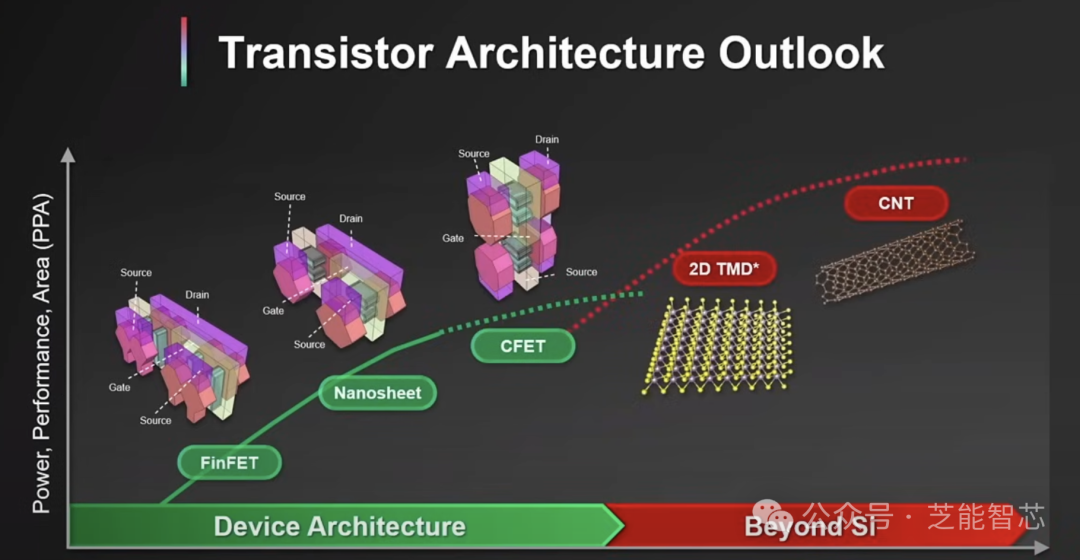

目前,光刻技术已进入超紫外(EUV)时代,间距缩放仍在继续。器件架构从平面发展到16nm节点的FinFET,大大改善了晶体管的静电性能。

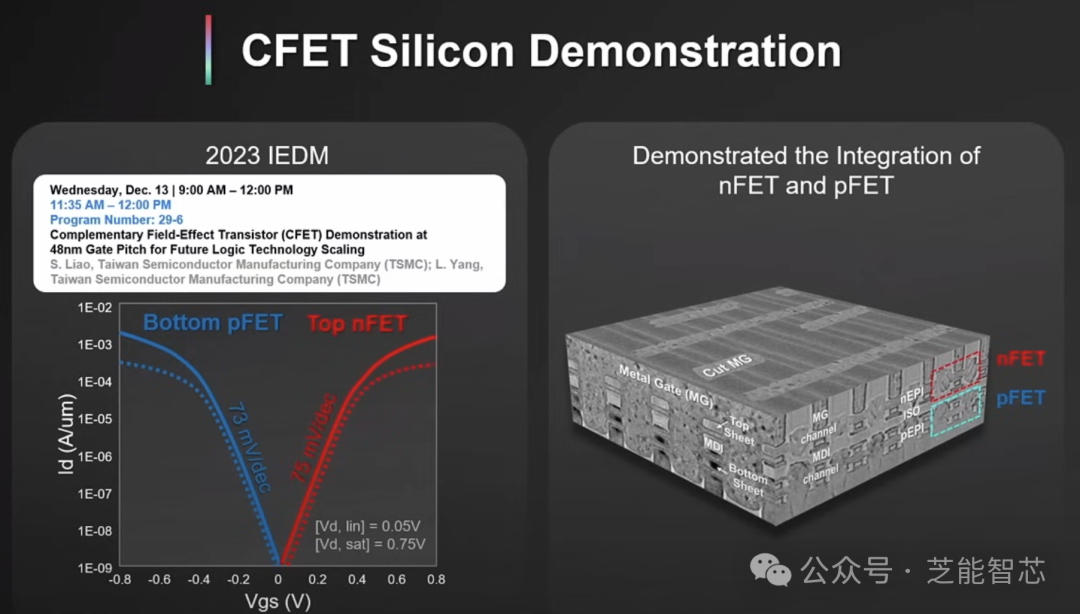

新兴的CFET架构

展望未来,垂直堆叠一个nFET和一个pFET,形成所谓的CFET(Complementary FET),可带来显著的密度扩展优势。除了CFET之外,低尺寸沟道材料还能进一步提高尺寸和能效。

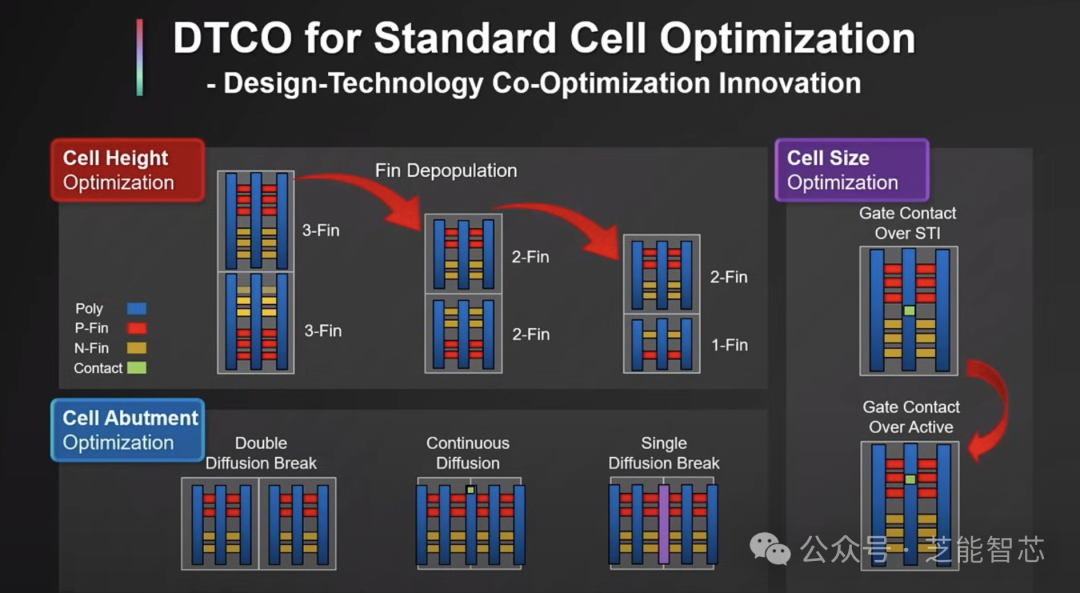

工艺创新与设计技术协同优化(DTCO)

DTCO通过调整技术定义来实现特定产品设计的优化,从而成为获取最大价值的关键。利用鳍片去顶来降低标准逻辑单元高度是改善产品性能、功耗和面积(PPA)的有效方法。在每个标准单元的鳍状结构达到2鳍状结构后,又进一步通过交织2鳍状结构和1鳍状结构标准单元来创建混合结构,从而推动PPA优化。

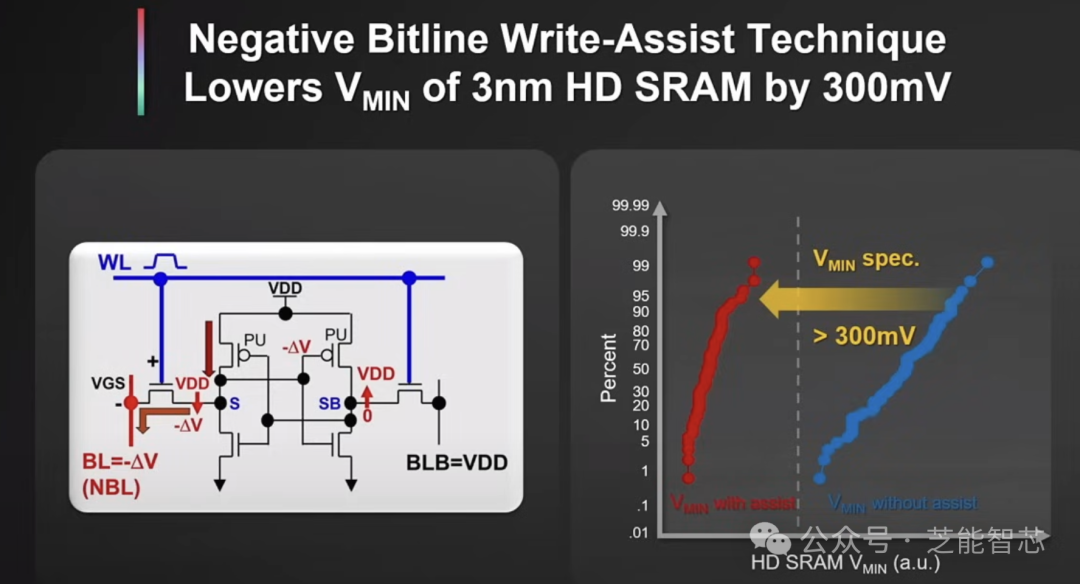

● SRAM和STCO的进展

DTCO在提高3纳米SRAM性能方面发挥了关键作用。例如,负位线(NBL)写入辅助技术的应用使HD SRAM的Vmin降低了300mV以上。为了满足未来计算工作负载对内存性能日益增长的需求,SRAM设计和高速缓冲存储器架构的系统技术协同优化(STCO)变得至关重要。

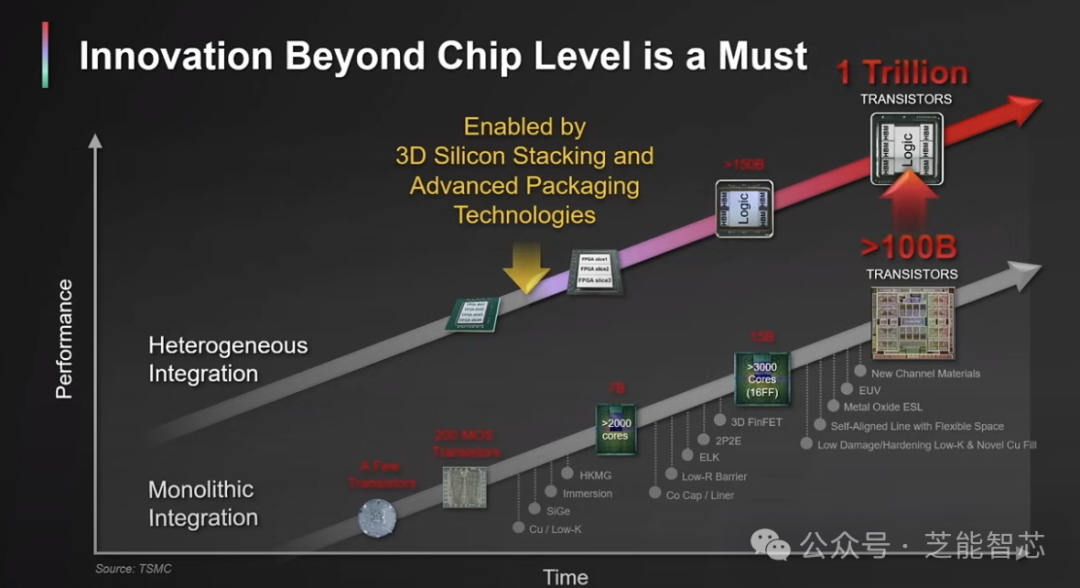

在高性能处理器上附加高速缓冲存储器的三维芯片堆叠技术具有显著的带宽和功耗优势,并已应用于高性能计算产品中。

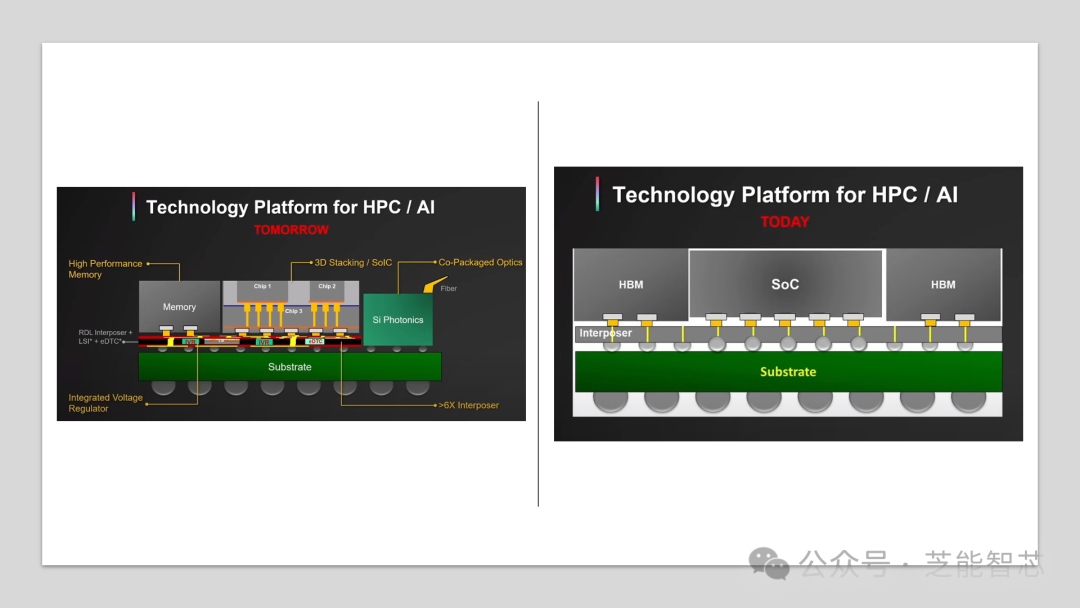

● 先进封装与系统级优化

除了芯片级的先进工艺技术开发外,先进的封装和集成对于实现系统级性能也越来越重要。高性能计算系统优化的关键因素包括用于集成更多计算资源的先进封装技术、用于解决内存带宽问题的内存和逻辑集成、超越片上电容器的电源传输优化,以及利用硅光子学和共封装光学器件(CPO)解决I/O瓶颈问题。

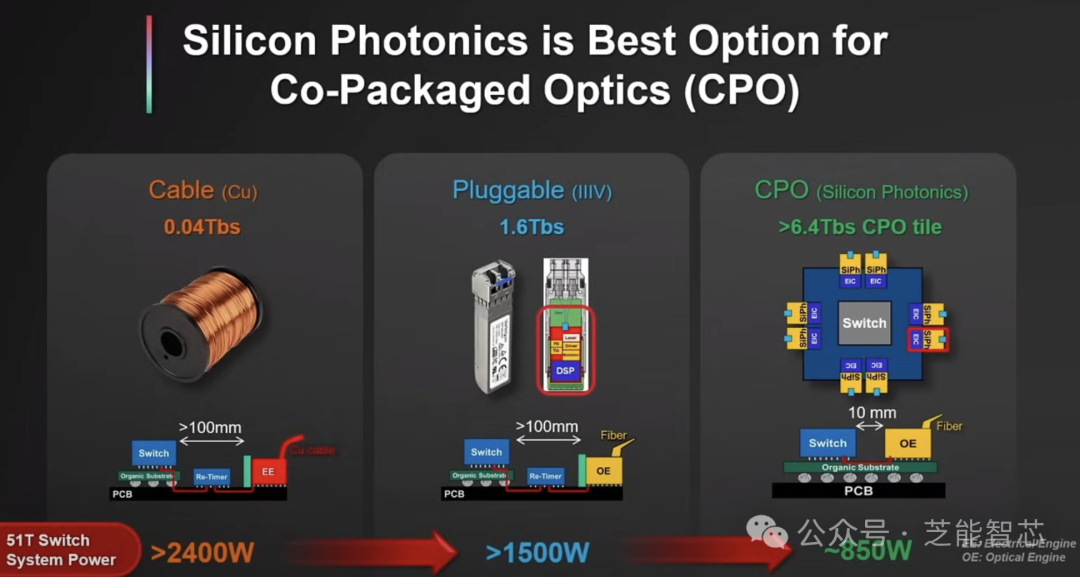

● CPO的未来前景

CPO(共封装光学器件)的带宽密度和能效有望超过224Gb/s。通过CPO,光子技术可以集成到计算SoC附近,提供与电气I/O相当的能效,但传输距离更长。CPO预计将带来超过170倍的速度提升,但耗电量仅为铜线互连的20%。

此外,光通道比电气通道更具可扩展性,因为数据可以通过多波长或多模光纤传输,然后复用到信号光纤中。

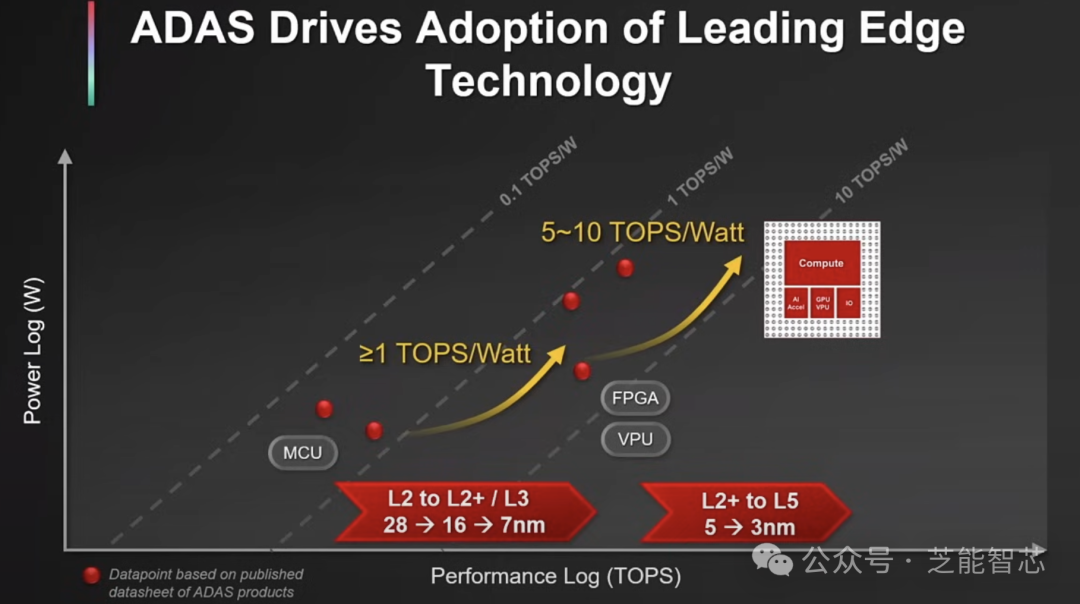

● 智能驾驶边缘技术导入

● 汽车MCU的MRAM和RRAM技术

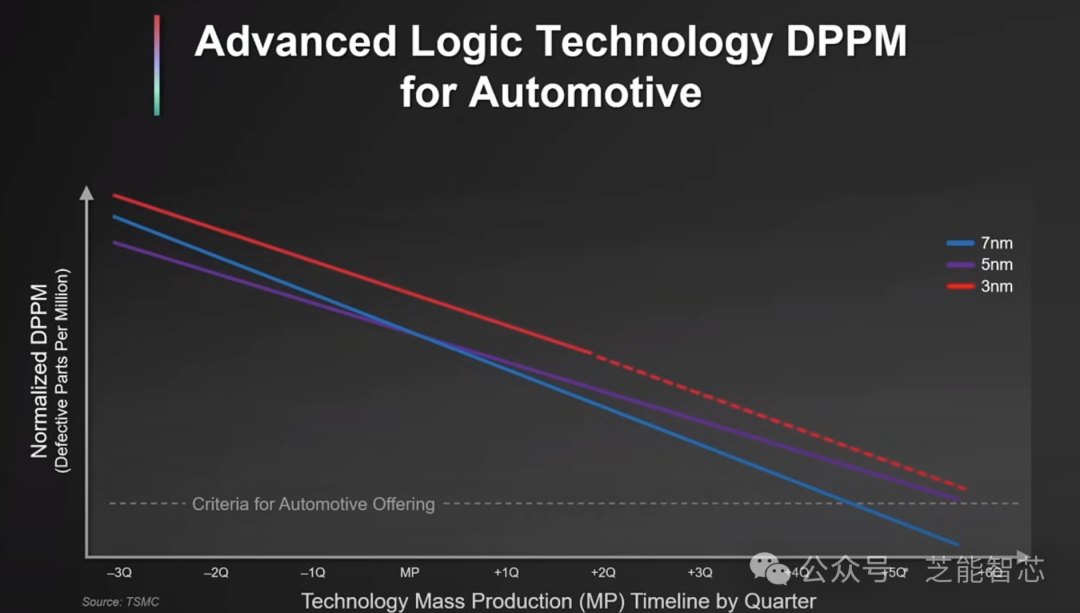

车用半导体技术一直落后于消费电子和高性能计算,主要因为汽车对安全性的要求极高,必须接近零缺陷率。

为加快引入速度,晶圆厂、半导体制造商和汽车设计人员需更紧密合作。台积电正通过预先应用自动设计规则来降低缺陷密度,未来不久将看到3nm技术在汽车中的应用。

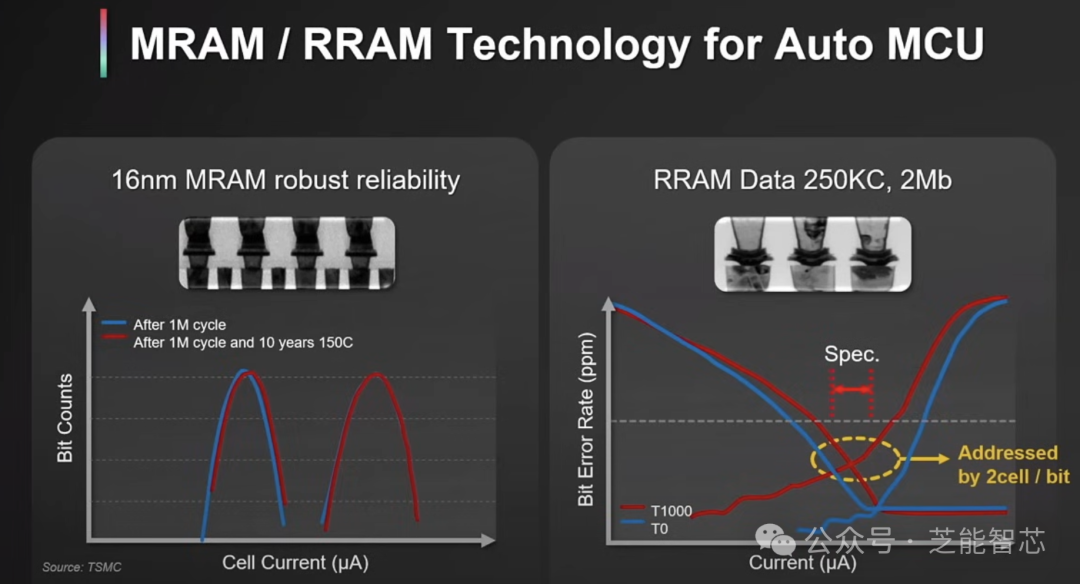

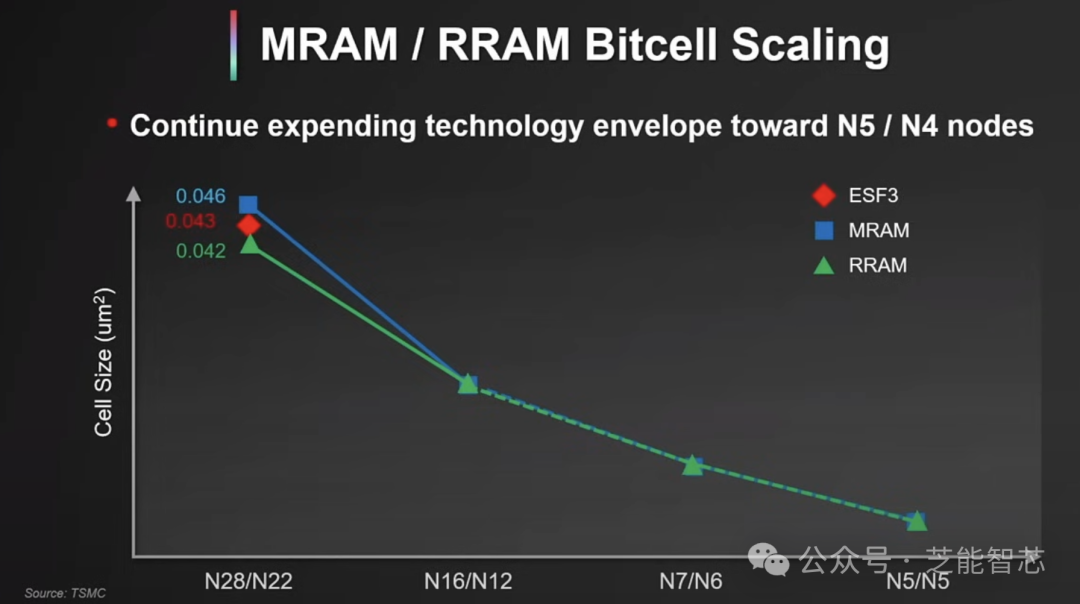

随着汽车转向区域架构,MCU(微控制单元)变得更重要,需要先进的半导体技术来提升运算能力。传统MCU多采用基于浮动闸极的技术,但在28nm以下遇到了瓶颈。

业界已在投资新型内存技术,如MRAM和RRAM等非挥发性存储器。这些技术将推动MCU从28nm缩小到16nm,甚至7nm。

小结

半导体行业正处于创新和发展的黄金时代。从高性能计算到先进的封装和集成技术,每一个环节都在不断突破和进步。