引言

随着电子设计自动化(EDA)验证工具的重要性日益增加,开发者们开始寻求减少流片成本和缩短开发周期的方法。其中,使用可编程逻辑芯片(FPGA)来构建有效的验证流程成为一种流行的解决方案,这种方法被称为原型验证。

原型验证在EDA流程中起到了至关重要的作用。一方面,它可以对芯片进行功能验证,确保设计的基本功能符合预期。在基本功能验证通过后,通过原型验证就可以提前开始驱动的开发,不用等待芯片流片(Tape Out)后的结果。当芯片回片后,应用程序可以直接基于原型验证版本的驱动进行简单的适配,从而应用于SoC(系统级芯片)上,这极大地缩短了SoC芯片的上市时间(Time-to-Market)。

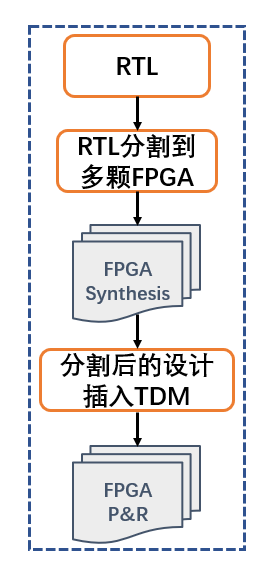

但随着ASIC设计变得越来越庞大和复杂,开发周期也日益紧迫,需要左移验证周期。相较于硬件仿真,原型验证变得愈发重要。然而,单片FPGA已无法满足大规模SoC的需求,商用原型验证系统的使用已经迈入多FPGA系统的时代。如今的研发团队迫切需要一款自动化程度高、性能强、稳定性好的国产商用原型验证平台。这样的平台不仅需要具备强大的RTL级分割、多片FPGA之间的互联拓扑结构、高效的自动化流程、优化的性能和可靠的稳定性,还需要满足国产化和可扩展性的要求,才能帮助芯片公司在激烈的市场竞争中脱颖而出。这些都对当前的原型验证提出了更高的要求,也带来了前所未有的技术挑战。

01

大规模SoC原型验证技术的挑战

02

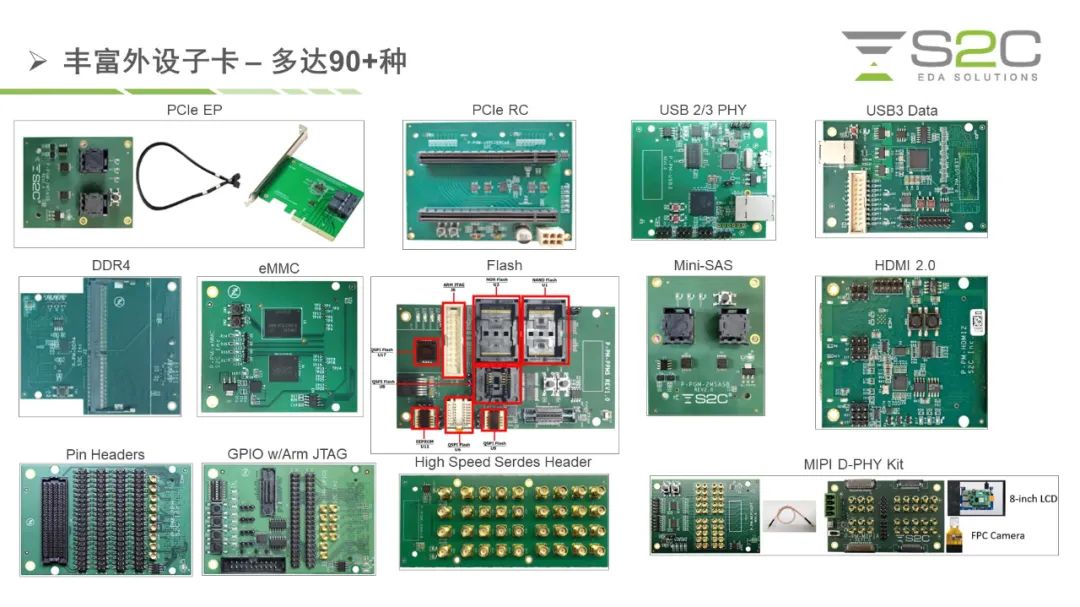

Prodigy芯神瞳原型验证解决方案