在使用高速模数转换器 (ADC) 进行设计时,需要考虑很多因素,其中 ADC 采样时钟的影响对于满足特定设计要求至关重要。关于 ADC 采样时钟,有几个指标需要了解,因为它们将直接影响 ADC 性能,尤其是信噪比 (SNR)。

在本文中,我们将探讨大量实验和权衡——并寻求在工作台上证明它们——以便让您更好地了解下一个 ADC 时钟设计。

时钟权衡及其对 ADC 性能的影响

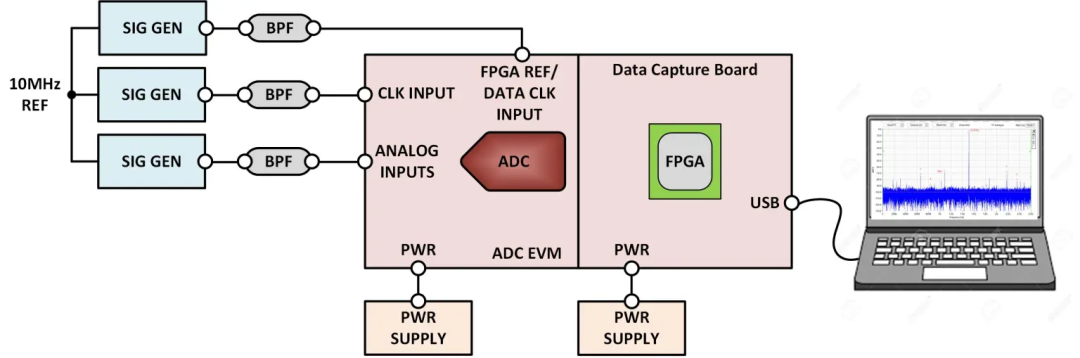

我们使用了一个带有三个信号发生器的评估模块,它们提供 ADC 所需的不同信号,如图1所示。模拟和时钟输入均通过 10 MHz 参考信号锁定参考,并使用带通滤波器进行滤波,以消除来自信号发生器的任何不需要的噪声和杂散。

图 1 ADC 测试测量设置在实验室中的样子。资料来源:德州仪器

在尝试最大限度地提高高速转换器设计的性能时,有许多权衡。让我们首先从源开始:实验室中用作采样时钟源的信号发生器。在实验中,我们使用了输出功率为 +10 dBm 的 25 MHz 时钟或信号发生器。我们在相同条件下配置每个信号发生器,以了解相对相位噪声对转换器性能的影响。

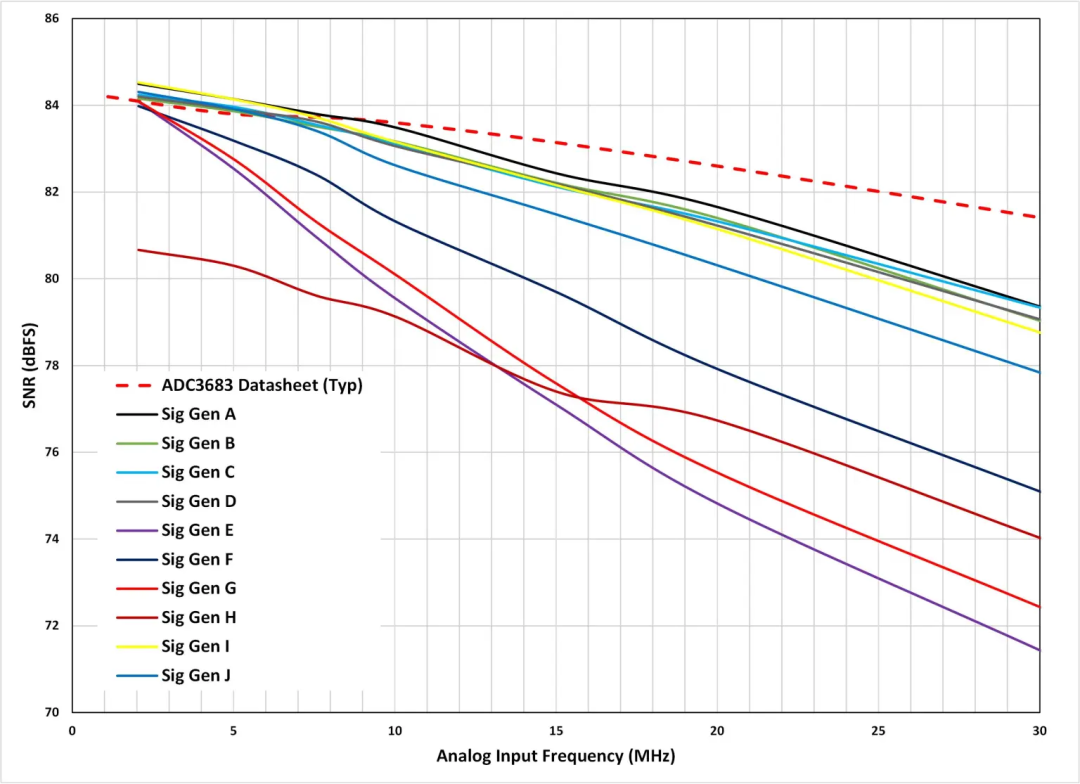

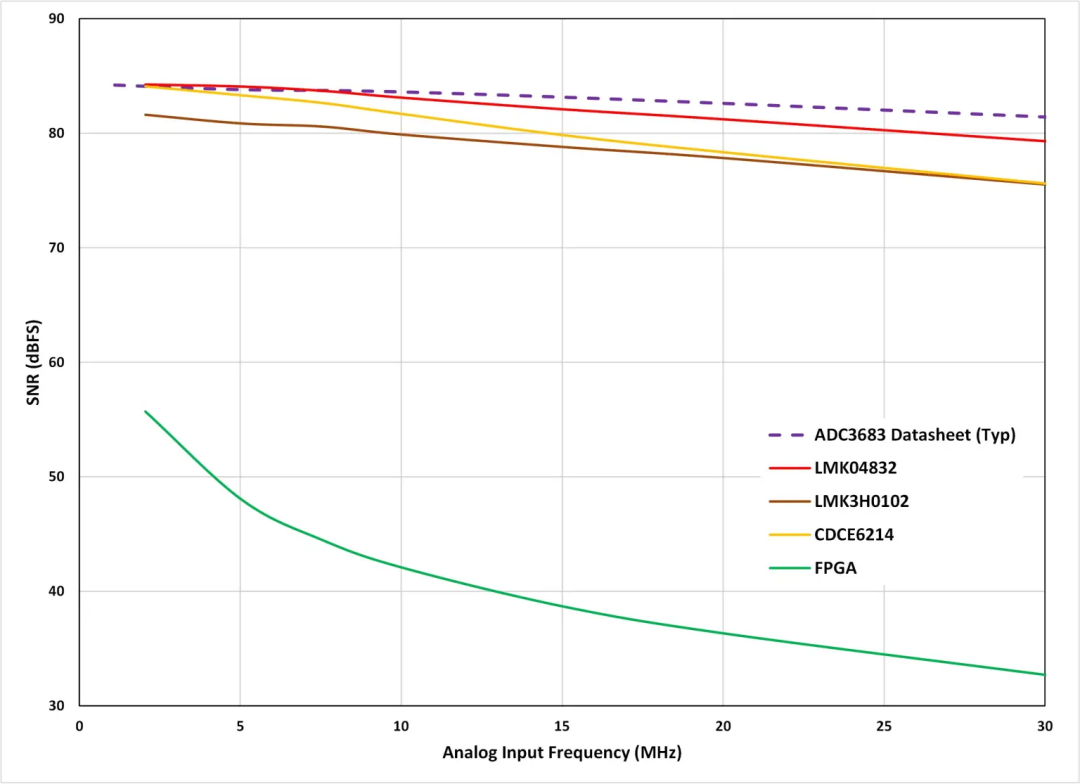

然后,我们利用图 2所示的不同信号发生器以 25 MSPS 的频率对 ADC 进行时钟控制。对于每个测试源,我们将时钟保持在 +10 dBm 不变,并将模拟输入频率 (Fin) 从 2 MHz 扫描至 30 MHz。在每个频率点,我们将信号发生器的输出功率水平调整为 -1 dBFS,然后测量相对于满量程的 SNR 值(以分贝为单位)。为了保持实验的一致性,我们始终使用性能最高的信号源作为模拟输入源。

图 2 ADC 的 SNR 与 Fin@-1 dBFS 的关系显示采用不同的时钟信号源,频率为 25 MSPS @ +10 dBm。资料来源:德州仪器

如图 2 所示,当模拟频率增加时,SNR 开始下降并恶化。这个术语称为“抖动受限”,这意味着在某个时刻,ADC 时钟源、时钟信号链或两者的抖动或相位噪声将开始主导转换器的整体性能,导致在使用噪声更大的时钟源操作转换器时 ADC 的 SNR 更差。

如您所见,随着模拟输入频率的增加,每个信号发生器的相位噪声贡献略有不同,而在较低的模拟输入频率下,相位噪声的影响较小。

时钟的斜率是影响 ADC 性能的另一个特性。时钟沿的斜率越尖锐,减少抖动的可能性就越大。当采样时钟沿穿过 ADC 的采样阈值时,尽量减少时钟沿的时序不确定性也很重要。

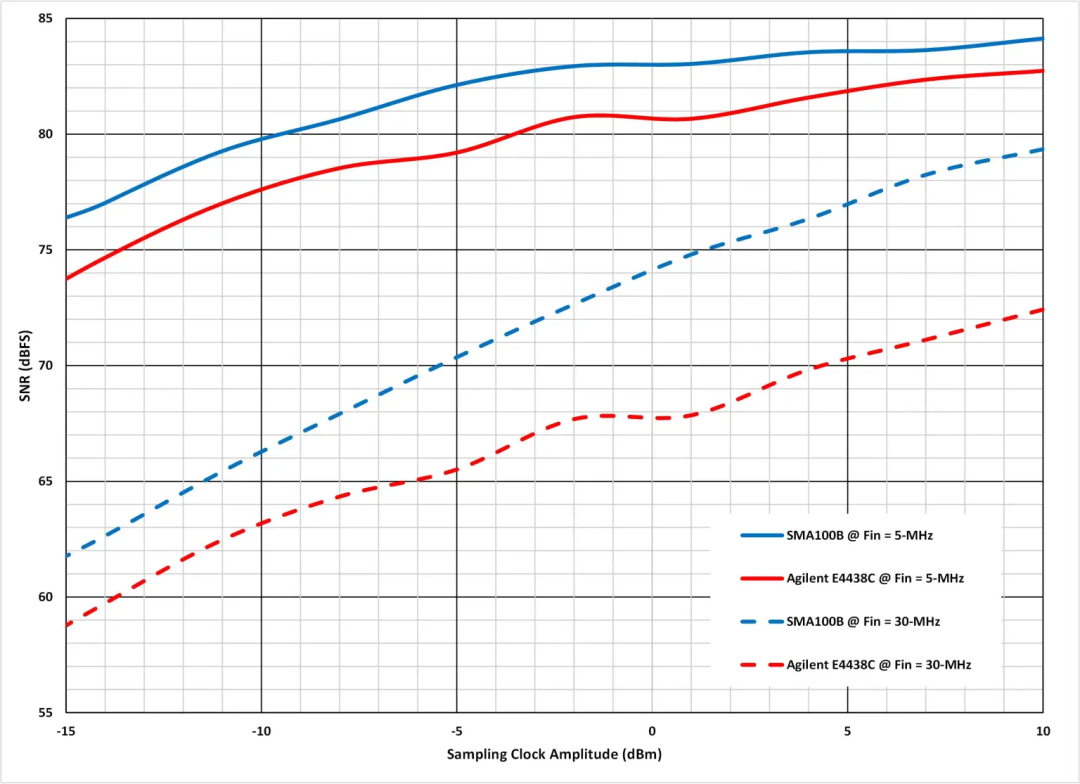

图 3展示了使用高性能信号时钟源和低性能信号时钟源时 ADC 采样时钟斜率对 ADC 性能的影响。从图中可以看出,当将 25 MSPS 时钟源的幅度水平从 +10 dBm 降低到 -15 dBm 并保持 5 MHz 和 30 MHz 模拟输入频率的输出功率水平恒定时,随着时钟信号源变为 +5 dBm 或更小,SNR 开始下降。

图 3 SNR 与采样时钟幅度的关系显示了斜率。来源:德州仪器

请记住,每个 ADC 都有自己的灵敏度水平;因此,+5 dBm 并不涵盖所有情况。它只适用于此 ADC 测试案例,以证明时钟源上更锐利的转换速率如何帮助您从 ADC 获得最佳 SNR。

根据预期的 ADC 性能应用时钟权衡

相位噪声曲线中噪声的一个较大贡献者是噪声基底,也称为宽带噪声。如果一个源的噪声基底高于另一个源,则噪声基底较高的源将增加相位噪声曲线下的面积,从而增加指定积分带宽的抖动值(请注意,抖动是相位噪声的积分)。

带通滤波器通常有助于降低时钟信号和/或模拟输入信号源的宽带噪声。它们还能过滤掉不必要的杂散信号,即使是高性能、低噪声信号发生器也会产生这种杂散信号。

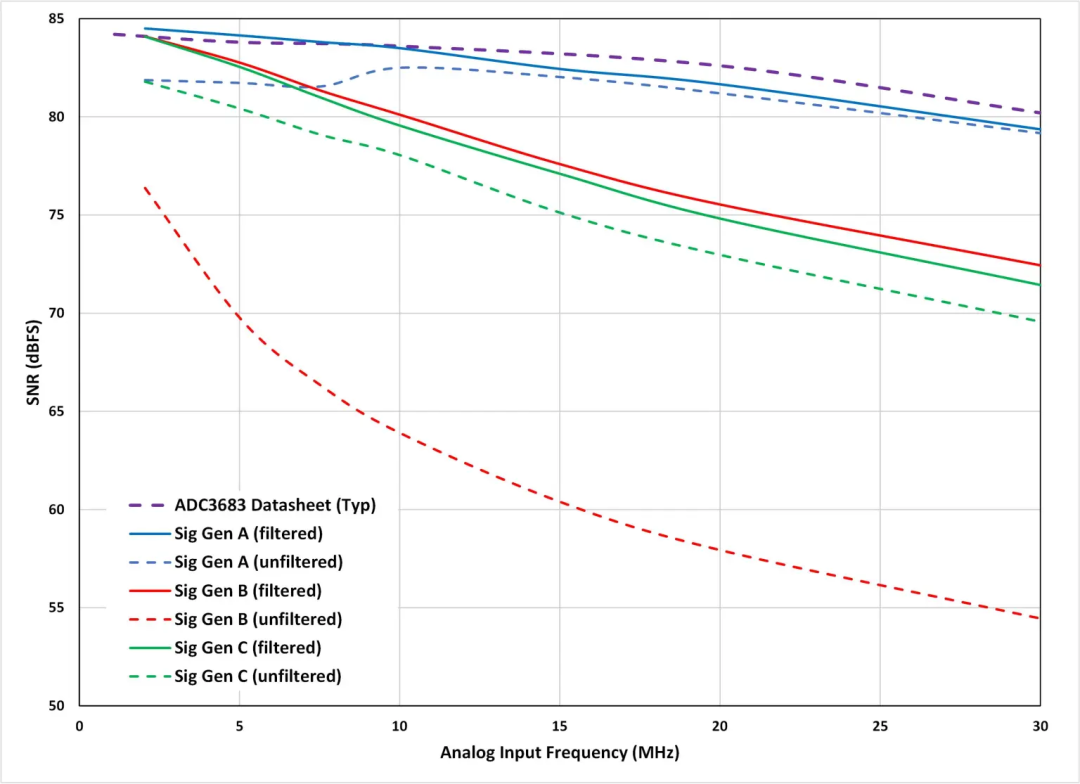

图 4展示了 ADC 的 SNR 性能与模拟输入频率的关系,使用相同的三个信号发生器作为采样时钟(滤波和未滤波两种情况)。在用于时钟的信号发生器的输出上应用滤波器时,可以清楚地看到 SNR 的改善。在性能较低、本底噪声较高的信号发生器上应用滤波器时,情况也是如此,因为其固有相位噪声本来就很差。

图 4显示了在使用不同时钟信号源时 ADC 的滤波和无滤波的 SNR。来源:德州仪器

到目前为止,我们已经使用信号发生器来演示时钟信号的各种权衡。然而,在现实世界中,大多数设计人员都会为他们的 ADC 设计选择特定的时钟设备。在某些情况下,设计人员甚至可能希望使用现场可编程门阵列 (FPGA) 作为 ADC 的采样时钟,尽管我们在 TI 不建议这样做,因为用作时钟的 FPGA 与其他时钟设备相比具有显着的抖动。

为了进一步解释 FPGA 时钟对 ADC 性能的影响,图 5展示了使用 FPGA 输出时钟为 ADC 提供时钟时对 ADC 的 SNR 性能的影响,而其他时钟设备则不然。具有较高相位噪声和较高本底噪声的时钟源会显著影响转换器的性能。

图 5这是时钟设备和 FPGA 输出时钟与 ADC 的 SNR 在模拟输入频率上的关系。来源:德州仪器

为了实现 ADC 数据表的 SNR,您可能需要考虑多种权衡,以优化您的应用的时钟信号链。这可能包括使用无源巴伦实现而不是有源设备,因为无源巴伦会将更少的噪声引入 ADC 或系统。虽然无源设备会带来更干净的性能,但它们有时在空间和成本方面存在劣势。

正如我们在本文开头提到的,具有高转换速率的快速上升信号(例如低压正射极耦合逻辑 (LVPECL) 或电流模式逻辑 (CML))可使 ADC 性能优于低压差分信号 (LVDS)。差分式接口也更好,因为它们本身可以消除任何共模噪声。将时钟设备输出配置为单端低压互补金属氧化物半导体 (LVCMOS) 信号会导致 ADC 的 SNR 性能降低。

选择合适的时钟

提供干净、高转换速率的时钟源对于最大程度地提高任何 ADC 性能都至关重要。这些基本原理在使用每秒千兆采样的 ADC 或任何高速 ADC 进行设计时也适用,尽管本文中的所有实验案例都在每秒兆采样的范围内。

了解相位噪声和抖动之间的差异也至关重要。确保将积分带宽上限设置为至少 Fs(我们建议为采样频率的两倍),以捕获采样时钟源贡献的抖动的噪声基底。请记住,宽带噪声基底是相位噪声和抖动计算的最大噪声贡献者,对 ADC 的 SNR 性能影响最大。

选择正确的时钟有助于实现 ADC 的预期性能,因为并非所有时钟设备、振荡器和信号源都是一样的。在适当的时候对时钟进行滤波,有助于降低杂散、降低宽带噪声或两者兼而有之。然而,使用滤波器时可能会有权衡,因为滤波器会降低时钟沿的斜率。

远离 FPGA 时钟。我们知道,它们在 FPGA 结构中设计和实现起来很简单,而且是一种低成本的替代方案。但如果 ADC 的 SNR 性能是您设计的重点,那么它们就无法提供所需的性能。

选择正确的时钟接口也很重要。差分信号是消除时钟信号上的共模噪声和干扰的关键。使用 LVPECL 或 CML 类型的接口可获得最佳的斜率信号质量,而不是 LVDS 或单端 LVCMOS 时钟信号接口。

6月20日-21日将在上海举办一期高级电源管理芯片设计课程,本课程将讲述电源管理电路中最常见的模块LDO和DC-DC的相关知识、设计技巧和前沿揭秘,包括模拟LDO,数字LDO,电感型DC-DC,电容型DC-DC和最近关注度很高的混合型DC-DC。

--点击图片即转至课程页面

7月16日-17日将在上海举办一期高级数模转换器(ADC)课程,本次课程首先深入探讨大规模时间交织 ADC 的交织器拓扑结构,探讨非理想情况、设计注意事项、建模技术和详细案例研究。随后,特别关注对高性能大规模 TI ADC 至关重要的外设块的设计挑战和解决方案,包括输入缓冲器和参考缓冲器。此外,还研究了极限采样器、残差放大器和时钟等关键 SAR ADC 块,通过全面的案例研究介绍了基本概念和先进技术。

今天小编带来了:ISSCC2024套餐,里面有文章、Short Course、PPT、Tutorial等,同学可以拿回去自己学习研究。

ISSCC2024完整资料领取方式如下

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台