赛题:ASIC DRC违例预测模型设计及AI-PC部署挑战赛

赛题背景:

随着人工智能和大数据应用的不断发展,对于高性能、低功耗的ASIC(专用集成电路)芯片需求日益增长。然而,设计和验证ASIC芯片的过程中,面临着一个重要的挑战:设计规则检查(DRC)违例的预测和解决。DRC是芯片设计流程中的关键步骤之一,用于确保芯片布局和连线满足制造工艺的要求。DRC规则由芯片制造工艺厂商提供,通常包括关于金属线间距、晶体管尺寸等方面的规定。设计人员必须确保他们的设计不会违反这些规则,否则可能导致芯片生产失败或性能下降。

传统上,DRC是在设计完成后进行的,但随着芯片规模的不断增大和制造工艺的不断进步,DRC的复杂度也呈指数级增长。这导致了设计验证周期的延长和生产成本的增加。因此,提前识别可能的DRC违例并及时进行修复变得至关重要。AI在解决这一挑战中发挥了重要作用。通过利用大量历史设计数据和对应的DRC结果,可以训练AI模型来预测新设计中可能出现的DRC违例。这种方法可以大大加速设计验证过程,降低成本,并提高芯片的生产质量。

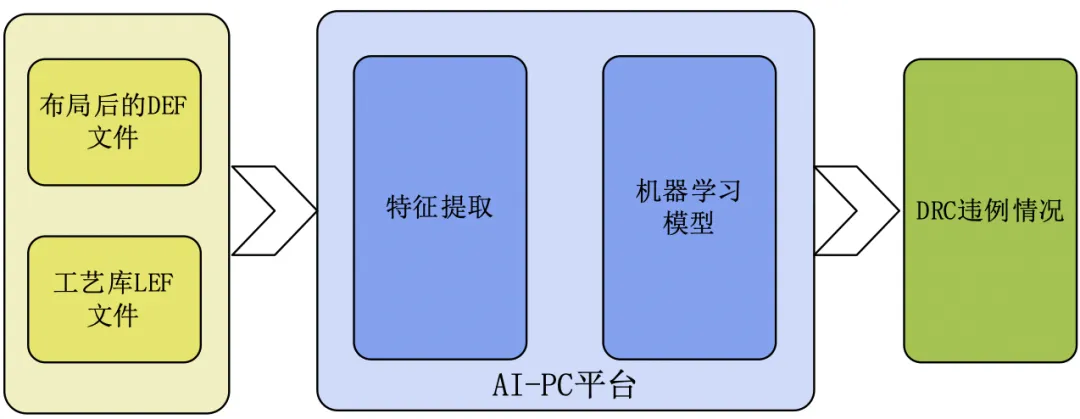

本次赛题旨在促进AI在ASIC EDA算法领域的应用,同时探索EDA算法在AI-PC平台的异构计算部署,进而提升EDA算法在AI-PC上的计算效率。

报名与提交

报名:请点击以下链接或扫描二维码报名

组委会将根据报名信息通知培训时间

https://www.wjx.top/vm/mBrTh1g.aspx

提交:请参赛队伍将作品提交至邮箱

aipc_contest@163.com

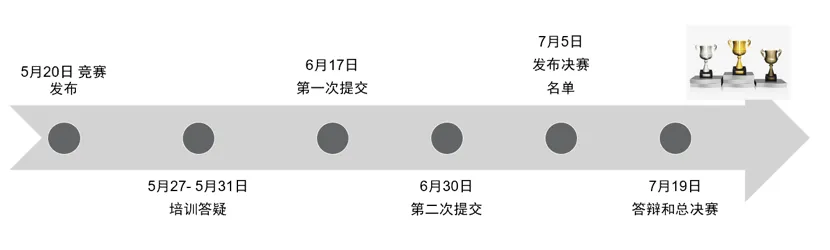

比赛设置两次提交机会,取成绩最佳的一次

赛题详情:CCF-DAC挑战赛 2024赛题发布