今天,首先要分享的是论坛网友bearlin12在2019年发布的《版图笔记 (1)》。尽管这篇文章已经发表了一段时间,但根据网友们最近的留言,它仍然具有很高的参考和学习价值。希望大家能从中受益。

文章链接:

https://blog.eetop.cn/blog-1674463-6943687.html

作者博客地址:

https://blog.eetop.cn/1674463

正文:

芯愿景导入电路

① 在Cadence下:

File→Export→EDIF 200...→Browe选择文件→Output File 改名→OK

导出edif ,out后叫经理导入到共享,再从共享拉到桌面。

② 在ChipAnalyzer下:

文件→导出EDIF 200网表格式。

在D/Chiplogic Family/ChipAnalyzer/Bin下找到导出的网表文件。

在D/Chiplogic Family/ChipMaster/Project下复制多一个analogLib1,再建多一个数字电路的文件夹,只要Symbol。

③ 在ChipMaster下:

新建单元库→导入***.out文件→删除多余单元→再导入***.edif文件→打开顶层文件。

设置顶层文件(右键→设置为顶层文件)→电路→显示线网列表窗口→全选后右键→自动标号化长引线...→填写引线长度阈值→回到顶层文件→调整间距→导出EDIF 200→放到共享上叫经理导入Cadence。

(去掉提图中的悬空线头:工具→选项→单元数阈值:0)

④ 在Cadence下:

导入EDIF 200。

设置点亮线加粗

CIW窗口的Tools→Display Resource Manager...→Edit→Layers下选LSW→分别设置y1 drawing,y2 drawing,y3 drawing……的Line Style。

查找单元器件(电路)

Edit→Search→Final

长出nplus\pplus(铝栅)

(先画上area层)Verify→DRC→设置Rules File文件(gate.rul)→OK

加载技术文件

Tools→Technology File Manager...→Attach...

回原点

Edit→other→Move Origin

基于Dracula的LVS

① 建立文件

单独建一个run LVS文件夹,在这个文件夹里导入版图的***.gds文件;电路的***.cdl文件;复制好规则文件***.lvs

① vi ***.lvs改写两项

PRIMARY=版图文件名;

INDISK=版图文件名.gds;

② LOGLVS

→Cir netlist(cdl文件名)→con ...(电路名)→x→PDRACULA→/g ***.lvs→/f→jxrun.com

③ vi lvs.lvs(打开lvs文件,检查错误)

查找Dracula的LVS错误

① Tools→Dracula Interactive,会出现DRC、LVS工具栏

② LVS→Setup...

③ 在Dracula Data Path中输出LVS的路径,会跳出View LVS选项卡

*Dracula修改版图后可直接jxrun.com跑LVS,修改电路需重新开始跑LVS。

制成cell

Edit→Hierarchy→Make Cell...

打散cell

Edit→Hierarchy→Flatten...

切角

Edit→Other→Modify Corner...→chamfer(角)

进入模块编辑

Shift+X 退出:shift+B

看到总模块的情况下编辑指定模块

X 退出:shift+B

生长层

Create→Layer Generation...→在这层的基础上 GROW BY距离 =需要生长层

全范围缩小增大

Edit→other→Size→设置Size Value

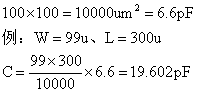

电容算法

电阻算法

取消查看DRC错误

Verify→Makes→Delete All...→OK

Library Manger分类

勾选Show Category→Category下建TOP

从其他路径下加载Library

Library Manager下Edit→Library Path→OK→Edit→Add Library→选择Library→Save AS

环线

create→Multipart Path→F3

Subrectangle:(中间孔的设置)

Layer:cont

Begin offset:-0.3(孔到包围线顶部距离)

End offset:-0.3(孔到包围线底部距离)

Width:0.8(孔的宽度) Length:0.8(长度)

Space:1.2(孔与孔的距离)

Separation:-1(孔中心到环中心线的距离,多排孔改这个距离即可)

Gap:minimum

Fustification:center(中心对称)

Enclosure Subpath:(外包层设置)

Layer:pplus

Begin offset:0.5 Enclosure:-0.5

End offset:0.5

→Apply→save.Template

版图里查找标号

(要有text层!)

Shift+S→Search for: label→Add Criteria→text==标号→勾选Zoom To Figure→Apply或者next

识别线名

(在Dracula LVS时)View LVS→选中线→Cursor Pick

从Library里移除或引进的Library

(只看不见,不删除!)

Library Manager下的Edit→Library Path→OK→选中其中一个Library→Edit→Remove Library Definition

替换电阻电容(电路)

在Library Manager下复制analogLib的电阻电容。

在CIW下:Tools→CDF→Edit→CDF Type:Base→Browse→选择复制到的Library下的电阻电容→下拉到Simulation Information→Edit→Choose Simulator:auCdl→修改Malel Name

做Pcell基本操作

添加图层:LSW下Edit→Set Valid Layers...→选Stretch dgþ→OK

版图窗口下:Tools→Pcell→Stretch→【Stretch in X(X方向拉伸)、Stretch in Y(Y方向拉伸)、Qualify(指定对象)、Modify(修改)、Redefine..(重新定义)】

Stretch in X——沿X方向拉伸(垂线)

Stretch in Y——沿Y方向拉伸(横线)

查看:Pcell→Parameters→Summarize

修改:Pcell→Stretch→Modify→选择Stretch线进行修改

保存:Pcell→Compile→To Pcell或点保存

查看版图里的库

Shift+T

查找版图DRC错误

Verify→Markers→Find...→勾选Zoom To Markers

版图复制Layout里自动变换成当前Library

复制Layout→To下的Library改成目标Library→勾选Copy Hierarchical 和Update Instances→OK→选Overwirte All(覆盖)或Fix Erros(命名)→OK

修改Netlist

搜索:/NP→(大写N向上翻,小写n向下翻)查找所有NP→:%/NP/PM/g→:wq

range 指范围,1,7指第一行至第七行,1,$指从第一行至最后一行,就是整篇文章, 也可以%代替。%是目前编辑的文章,#是前一次编辑的文章。

pattern 指要被换掉的字串,可以用regexp来表示。

string 将Pattern由String所取代

c Confirm,每次替换前询问

e 不显示error

g globe,不询问,整行替换前询问

i ignore不分大小写。

LVS跳线设置

LVS Options→Connect→勾选Connet nets with...(:)

打开Calibre运行LVS、DRC

在/home/lcm 0315下Vi .bashrc→复制/user/local/eda/……/license.dat到/home/lcm0315→回车运行

华润工艺转换方正工艺

在做好的Library下:cell复制cell_copy→打散cell_copy→T2改成A2→新建Library→再复制打散的cell_copy到新Library下→在cell_copy上生长gate.rul(最好单独一层)→跑DRC→根据错误,在原Library的cell里改错→再重复转换步骤,如此往复,直到修改完成。

欢迎大家访问作者博客

觉得有帮助可以关注并点赞支持作者

(第一次注册需要在电脑端进行)