芝能智芯出品

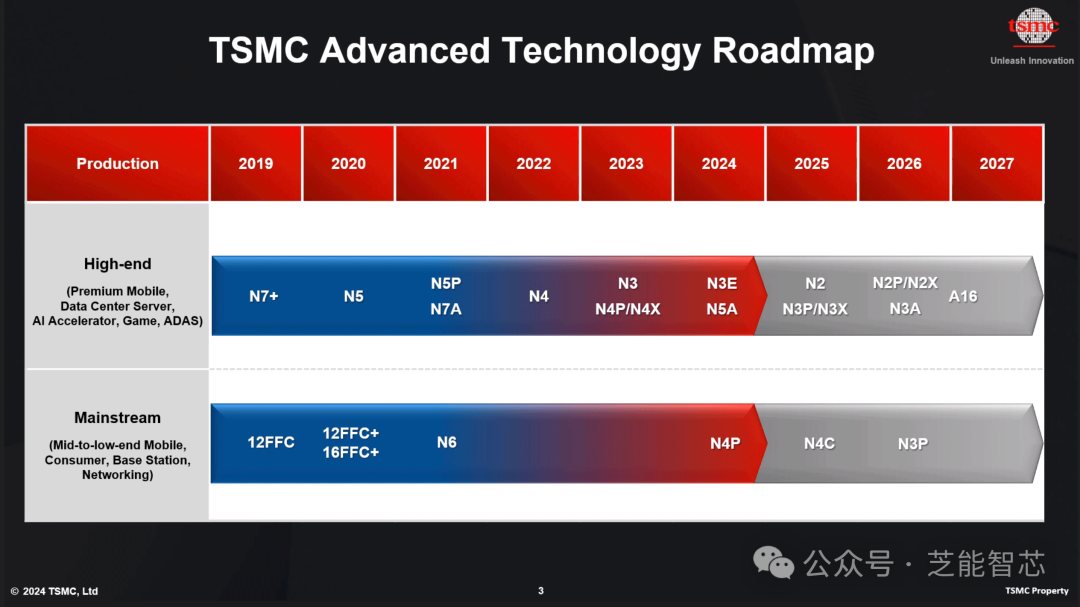

台积电在2024年北美技术研讨会上的发布,为全球芯片制造业投下了一枚震撼弹。会议中,台积电不仅确认了其2纳米(N2)工艺技术的时间表,生产计划稳扎稳打,预计在2025年下半年进入大规模生产阶段。

这一代技术的核心在于首次使用全栅极(GAAFET)纳米片晶体管,与传统FinFET结构相比,GAAFET提供了更精细的电流控制能力,从而在相同功耗下实现更高的性能或在相同性能下大幅降低功耗。

值得注意的是,原定于N2P版本中的背面供电网络(BSPDN)被取消,转而采用常规供电电路,这一调整可能是出于成本效益的考虑。

NanoFlex:

芯片设计的定制化革命

NanoFlex是此次发布的一大亮点,这项新技术允许设计者在单一芯片设计中混搭不同库的单元,无论是追求高性能、低功耗还是面积最小化。

这代表了一个巨大的进步,因为它赋予了设计者前所未有的自由度,去精确地调校其产品以满足特定应用的需求。与现有的FinFlex技术相比,NanoFlex因为GAAFET的引入而更加灵活,能够通过优化通道宽度、构建不同高度的单元,进一步提升性能或效率。

● SHPMIM电容器:电源稳定性的飞跃

除了工艺节点和设计技术的革新,台积电还在N2技术中引入了超高性能金属-绝缘体-金属(SHPMIM)电容器,其容量密度是前代技术的两倍以上,同时显著降低了电阻,这对于维持芯片的电源稳定性至关重要,尤其是在高性能计算和5G等高要求领域。

成熟节点的持续优化:

N4C的登场

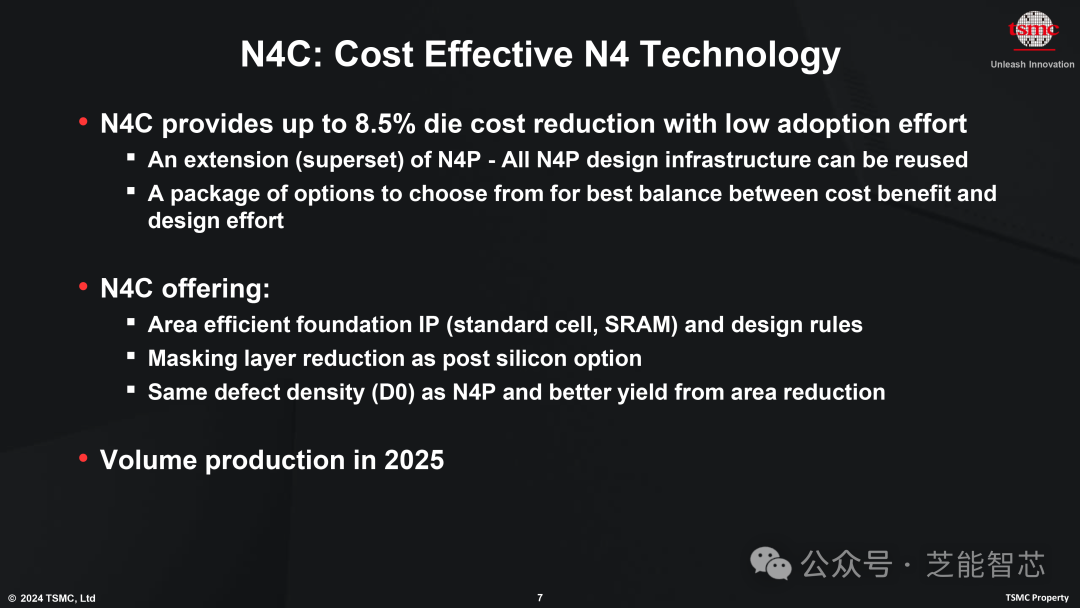

台积电在2025年推出一种更经济的4纳米(N4C)工艺技术,通过一系列优化措施将生产成本降低8.5%,提升现有成熟工艺的性价比,以满足不同市场和客户需求。

N4C是台积电5纳米级家族的最新成员,是对N4P技术的进一步优化。通过重新设计标准单元和SRAM单元、调整设计规则及减少制造过程中的掩膜层数,N4C旨在缩小芯片尺寸、简化生产流程,从而达到成本节省的目的。

此外,它还承诺在保持与N4P相同的晶圆级缺陷密度的同时,通过减小芯片面积提升良品率,即在单位晶圆上产出更多无瑕疵的芯片。

台积电业务开发副总裁Kevin Zhang强调,N4C将为使用4纳米技术的客户提供额外的成本节约途径,允许他们通过去除部分制造步骤和改进原有IP设计来减少总体拥有成本。N4C兼容N4P的设计基础设施,尽管目前对于是否能直接复用N5或N4P的IP还有待明确,但台积电表示会为客户提供灵活的选择,以平衡成本效益与设计投入。

此新工艺的引入正值台积电客户正转向使用其最先进的3纳米技术之际,特别是考虑到3纳米系列中N3B的成本问题和性能、密度提升的相对有限。N4C凭借其成本效益和成熟的FinFET架构,预期将成为一个长寿命周期且受欢迎的节点,尤其吸引那些寻求控制成本并维持技术稳定性的客户。

预计N4C将在明年的某个时间点开始批量生产。鉴于台积电在5纳米制程上的丰富经验和高良率,N4C有望在启动之初就展现出良好的生产效率和品质表现,进一步巩固台积电在全球半导体制造领域的领先地位。

小结

台积电2纳米技术的逼近和NanoFlex的引入,芯片设计将进入一个更加定制化和高效的时代。同时,对成熟节点的持续改进,如N4C的推出,展现了台积电对市场多元化需求的深刻理解。